使用時鐘分配設備時或時鐘ADC和DAC的扇出緩沖器,需要處理信號衰減的兩個主要來源 - 印刷電路板(PCB)走線實現和輸出端接。

時鐘走線和信號擺幅

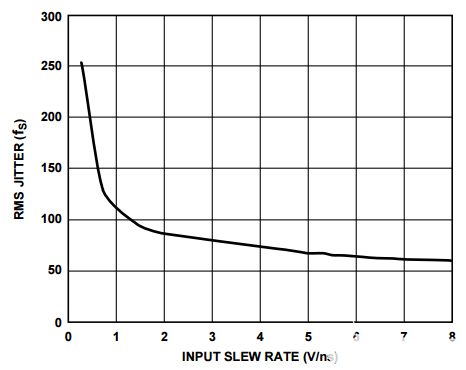

PCB走線的行為類似于低通濾波器,當時鐘信號沿走線行進時會衰減,并隨著走線長度的增加而增加脈沖邊沿失真。較高頻率的時鐘信號會受到更大的衰減、失真和噪聲的影響,但為了改善抖動(在低壓擺率下最差)(圖 1),通常使用具有高壓擺率的時鐘邊沿。要正確實現高質量的時鐘,請使用高擺幅時鐘信號和短時鐘PCB走線;將要時鐘的設備放置在盡可能靠近時鐘分配設備的位置。

圖1.ADCLK925 均方根抖動與輸入壓擺率的關系

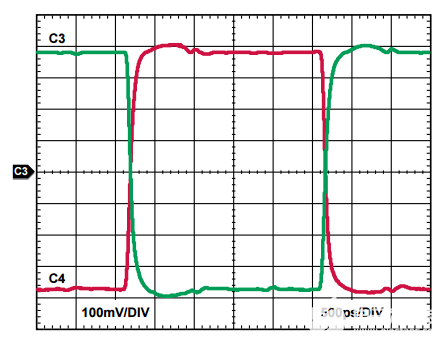

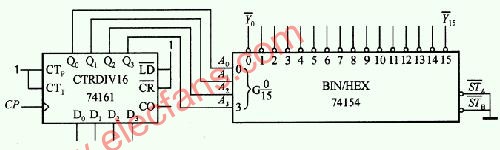

兩種這樣的時鐘分配器件是ADCLK9542時鐘扇出緩沖器和ADCLK9143超快時鐘緩沖器。ADCLK954內置12個輸出驅動器,可將800 mV全擺幅ECL(發射極耦合邏輯)或LVPECL(低壓正ECL)信號驅動至50 Ω負載,總差分輸出擺幅為1.6 V,如圖2所示。它以 4.8 GHz 的切換速率運行。ADCLK914可以將1.9 V高壓差分信號(HVDS)驅動至50 Ω負載,總差分輸出擺幅為3.8 V。ADCLK914具有7.5 GHz切換速率。

驅動DAC時,時鐘分配器件應盡可能靠近DAC的時鐘輸入,以便所需的高壓擺率、高幅度時鐘信號不會導致布線困難、產生EMI或因電介質和其他損耗而降級。注意,特性阻抗(Z0) 的跟蹤將隨跟蹤維度(長度、寬度和深度)而變化;驅動器的輸出阻抗必須與該特性阻抗相匹配。

圖2.采用3.3 V電源供電的ADCLK954時鐘緩沖器輸出波形。

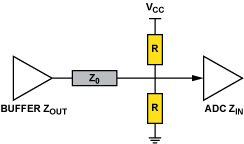

輸出端接

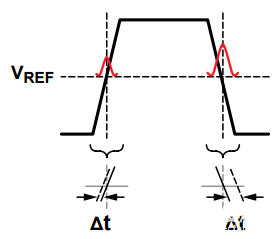

時鐘信號衰減會導致抖動增加,因此端接驅動器輸出以避免信號反射并在相對較大的帶寬上最大化功率傳輸非常重要。實際上,反射可能會導致下沖和過沖,嚴重降低信號和整體時鐘性能,或者在極端情況下,可能會損壞接收器或驅動器。當走線未正確端接時,會發生由阻抗不匹配引起的反射。由于反射系數的高通特性,它們對于具有快速上升和下降時間的高速信號更為重要。反射脈沖疊加在主時鐘信號上,從而降低時鐘脈沖的性能。它還通過在上升沿和下降沿增加延時不確定性或抖動(?t)來影響時鐘信號的邊沿,如圖3所示。

圖3.由于端接不當導致反射信號的抖動影響。

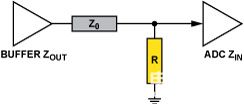

由于終止不當而導致的回波大小隨時間變化,因此?t也會隨時間變化。終止時間常數也會影響回波脈沖的形狀和寬度。由于這些原因,這種額外的反射引起的抖動形狀(看起來是高斯的)增加了經典抖動。為避免這種抖動和時鐘質量降低的不利影響,請使用適當的信號端接,如表1所示。Z0是線路的阻抗;Z外是驅動器的輸出阻抗;和Z在 是接收器的輸入阻抗。僅顯示了CMOS和PECL/LVPECL電路。

表 1.時鐘端接

| 方法 | 描述 | 強度 | 弱點 | 評論 |

|

串聯端接 |

首席營銷系統 |

|

實際上,緩沖器輸出端省略了電阻(R),因為電阻(R)在整個頻率上的動態行為很難匹配阻抗。 |

低功耗解決方案(無接地灌電流)。 易于計算 R (Z0– Z外). |

上升/下降時間受電路R和C的影響,增加抖動。 僅對低頻信號有用。 |

CMOS 驅動程序。 不適用于高頻時鐘信號。 適用于低頻時鐘信號和非常短的走線。 |

|

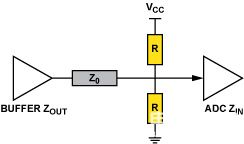

下拉電阻 |

首席營銷系統 |

| 非常簡單(R = Z0) |

高功耗。 |

不推薦。 |

|

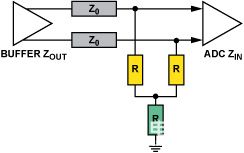

| 綠佩克利 |

|

簡單的 3 電阻解決方案。 在節能方面略好,同時與 4 電阻端接相比節省了一個元件。 |

推薦。 將終端電阻放置在盡可能靠近 PECL 接收器的位置。 |

||

|

交流端接 |

首席營銷系統 |

|

無直流功耗。 |

C應小以避免高功耗,但不要太小以允許灌電流。 |

||

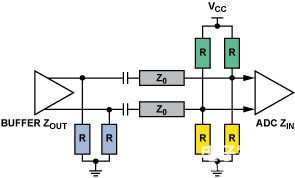

| 綠佩克利 |

|

交流耦合允許偏置電壓調整。避免電路兩側之間的功率流動。 |

交流耦合僅推薦用于平衡信號(50% 占空比時鐘)。 | 交流耦合電容器應為低ESR、低電容。 | |

|

電阻橋 |

首席營銷系統 |

|

合理的功率權衡。 |

單端時鐘使用兩部分。 |

||

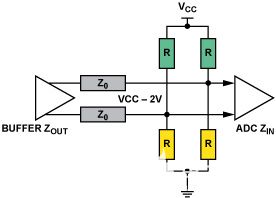

| 綠佩克利 |

| 使用四個外部器件用于差分輸出邏輯。 | 廣泛用于 3.3V LVPECL 驅動器的端接。 |

-

濾波器

+關注

關注

161文章

7795瀏覽量

177994 -

adc

+關注

關注

98文章

6495瀏覽量

544466 -

PCB

+關注

關注

1文章

1795瀏覽量

13204

發布評論請先 登錄

相關推薦

功率分配器

信號分配器

這是延長器還是分配器?

高速轉換器時鐘分配器件的端接

音視頻/信號分配器,音視頻/信號分配器是什么意思

VGA分配器,VGA分配器是什么意思

分配器,什么是分配器

高速轉換器時鐘分配器件的端接

高速轉換器時鐘分配器件的終止

高速轉換器時鐘分配器件的終止

評論