追求更小的 DRAM 單元尺寸(cell size)仍然很活躍并且正在進行中。對于 D12 節點,DRAM 單元尺寸預計接近 0.0013 um2。無論考慮使用 DUV 還是 EUV 光刻,圖案化挑戰都是重大的。特別是,ASML 報告說,當中心到中心(center-to-center)值達到 40 nm 時,即使對于 EUV ,也不推薦使用單一圖案化。在本文中,我們將展示對于 12 納米及更高節點的 DRAM 節點,電容器中心到中心預計將低于 40 納米,因此需要多重圖案化。

存儲電容器的 DRAM 單元布局

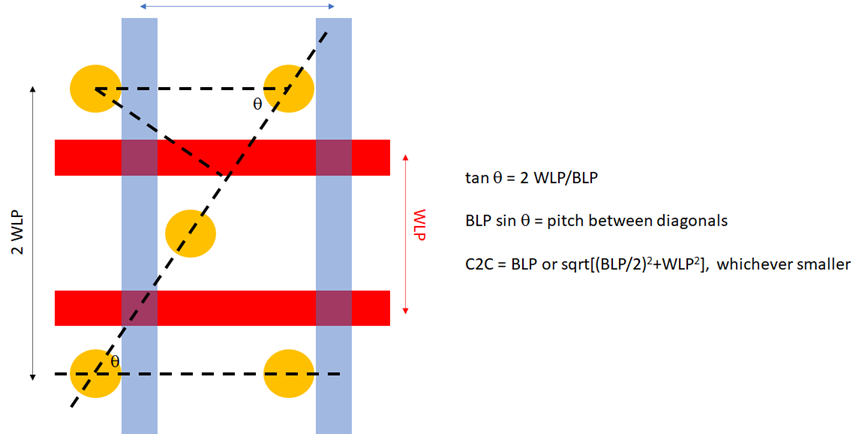

存儲電容器排列成六邊形陣列(圖 1)。有源區設計規則由位線間距和字線間距決定。

圖 1. DRAM 單元網格上的存儲節點(黃色)。BLP=位線間距,WLP=字線間距。

對于 0.001254 um2的單元尺寸和略低于 12 nm 的有源區設計規則,38 nm 的位線間距和 33 nm 的字線間距將導致 38 nm 的中心到中心和 32.9 nm 的對角線間距。

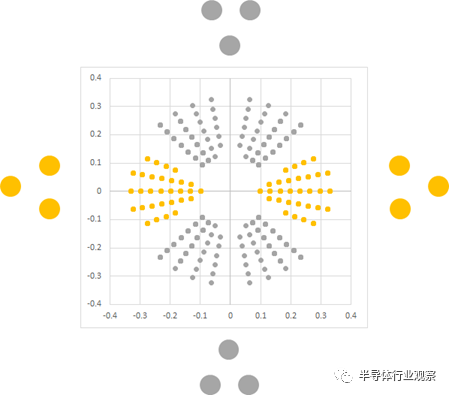

對于 0.33 NA EUV 系統,六邊形陣列將使用六極照明(hexapole illumination),其中每個極產生三光束干涉圖案(圖 2)。四個象限極產生與其他兩個水平極不同的模式。這導致具有獨立隨機性的兩個獨立劑量分量。這些被添加到最終的復合模式中。

圖 2. DRAM 存儲模式的六極照明由 4 個象限極(灰色)和兩個水平極(黃色)組成。根據照明方向,生成的三光束干涉圖案具有特定方向。

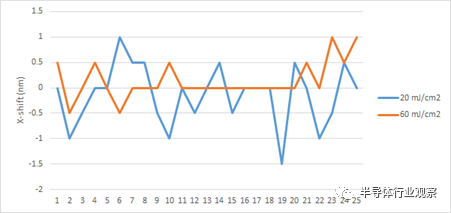

由于特征邊緣處大量吸收的光子散粒噪聲,圖案放置誤差的隨機效應非常顯著,正如參考文獻中已經公開的那樣。1,很容易超過 1 nm 的覆蓋規格。較低的吸收劑量似乎明顯更差(圖 3)。

圖 3. 38 nm x 66 nm cell(字線間距 = 33 nm)中中心柱的隨機放置誤差(僅 X),在 0.33 NA EUV 系統中具有預期的六極照明。這里顯示了兩個吸收劑量的一系列 25 個不同實例。

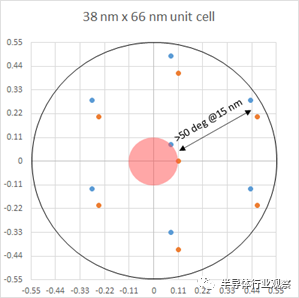

轉到 0.55 NA 會增加焦點深度嚴重降低的問題。NA 為 0.55 會導致 15 nm 散焦,導致最內層和最外層衍射級之間的相移 >50 度(圖 4),這會由于褪色嚴重降低圖像對比度。

圖 4. 0.55 NA EUV 系統上的 15 nm 散焦導致最內層和最外層衍射級之間的相移 >50 度。

因此,存儲節點圖案很可能需要由兩個交叉線圖案形成(圖 5)。每個交叉線圖案可以通過 EUV 單次曝光或 DUV SAQP(自對準四重圖案)形成。兩種選擇都是單掩模工藝。SAQP 工藝更成熟(早于 EUV)并且沒有 EUV 的二次電子隨機問題,因此它應該是首選。盡管如此,對于 SAQP 情況,間隔線必須在布局和線寬粗糙度方面得到很好的控制。

圖 5. 存儲節點圖案可以由兩個交叉線圖案的交叉點形成。

三星還展示了一種二維間隔蜂窩圖案,而不是線型 SAQP,它使用具有起始蜂窩圖案的單個掩膜,而不是具有起始線圖案的兩個掩膜。

雖然上述情況考慮了 38 nm 位線間距和 33 nm 字線間距,但由于六邊形對稱性,它也適用于交換間距的情況(33 nm 位線間距和 38 nm 字線間距)。

DRAM 技術,趨勢和挑戰

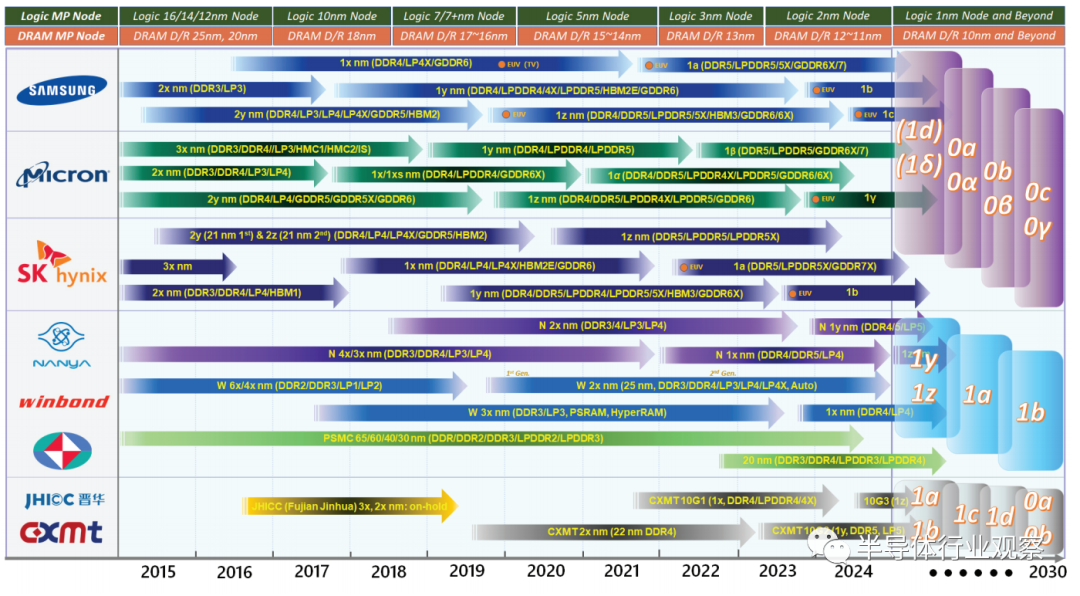

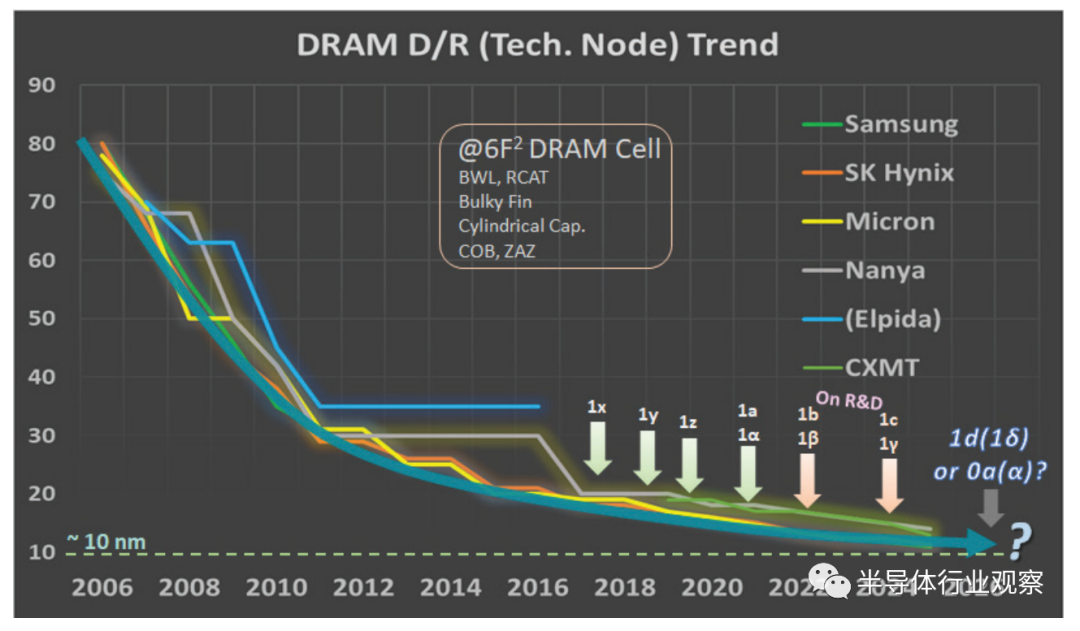

圖 1 顯示了來自三星, 美光, SK海力士,Nanya, PSMC, and CXMT廠商的 DRAM 路線圖。三星、美光和 SK海力士三大廠商已經展示了適用于 DDR4、DDR5 和 LPDDR5 應用的具有 15nm 和 14nm 級單元設計規則 (D/R) 的 D1z 和 D1a 產品。三星已在 D1x DDR4 試用車(TV) 產品和 D1z LPDDR量產產品中采用 EUV 光刻技術,而美光和 SK 海力士則為 D1z 代保留了基于 ArF-i 的雙圖案化技術 (DPT) 工藝。到 2030 年,將生產出D1d(或 1δ)、D0a(或 0α)和 D0b(或 0β)等設計進一步縮小的幾代 DRAM。

圖 1.由TechInsights 提供的 DRAM 路線圖,顯示 2020 年至 2022 年市場上商業化的 D1z 和 D1a DRAM 產品。到 2030 年,將生產出D1d(或 1δ)、D0a(或 0α)和 D0b(或 0β)等幾代產品。

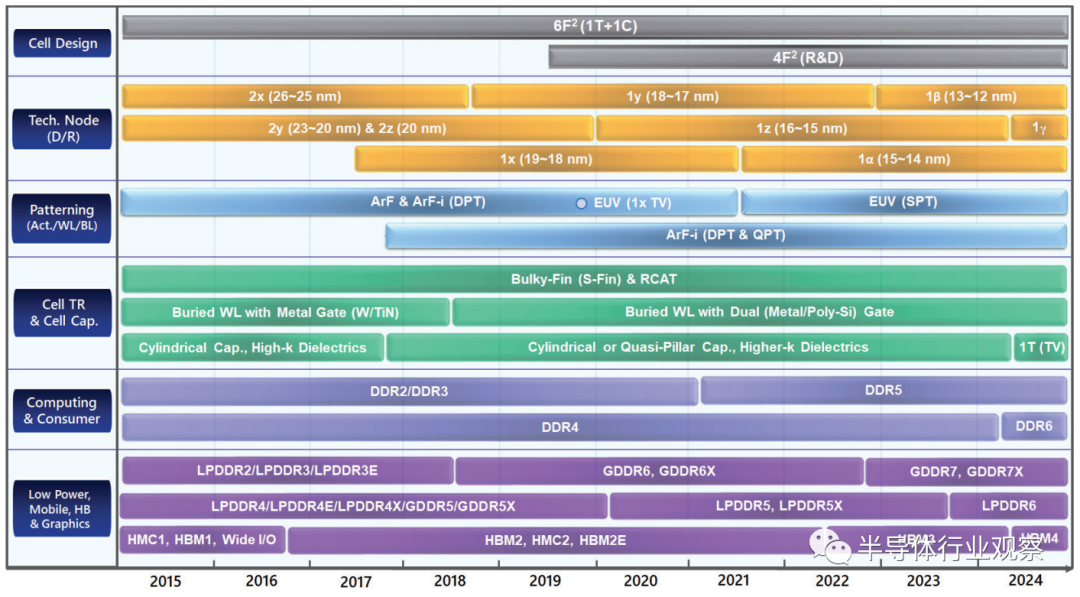

圖 2. DRAM 設備的技術/應用路線圖顯示 6F2 1T+1C 單元設計擴展到更多下一代 DRAM,盡管 DRAM 廠商一直在開發 4F2 單元結構,例如 1T DRAM 或無電容器 DRAM 原型。

到目前為止,已經有了 8F2 和 6F2 DRAM 單元設計,其中單元包括 1T(晶體管)和 1C(電容器)。這種 1T+1C 單元設計將用于未來幾代 DRAM 的 DRAM 單元設計。然而,由于工藝和布局的限制,DRAM 廠商一直在開發 4F2 單元結構,例如 1T DRAM 或無電容器 DRAM 原型,作為擴展 DRAM 技術的下一個候選者之一(圖 2)。具有 B-RCAT 結構的大塊鰭(或鞍鰭)用于單元存取晶體管,然而,掩埋字線柵極材料已經從單鎢層變為多晶硅/鎢雙功函數層,以有效控制柵極泄漏。在這種情況下,具有較低功函數的多晶硅上柵極提高了 GIDL 電場 (30%) ,增大了擴散電阻。此外,美光使用純 TiN 柵極進行 D1z 和 D1α 代單元集成。雖然圓柱型結構是DRAM單元電容器集成的主流,但SK海力士(D1y和D1z)和三星(D1z)采用了準柱狀電容器(或單面柱狀電容器)結構,其中單元電容器僅外表面呈圓柱狀,這導致單元電容比上一代更小。幾年后,DDR5、GDDR7、LPDDR6 和 HBM3 產品將在市場上普及。

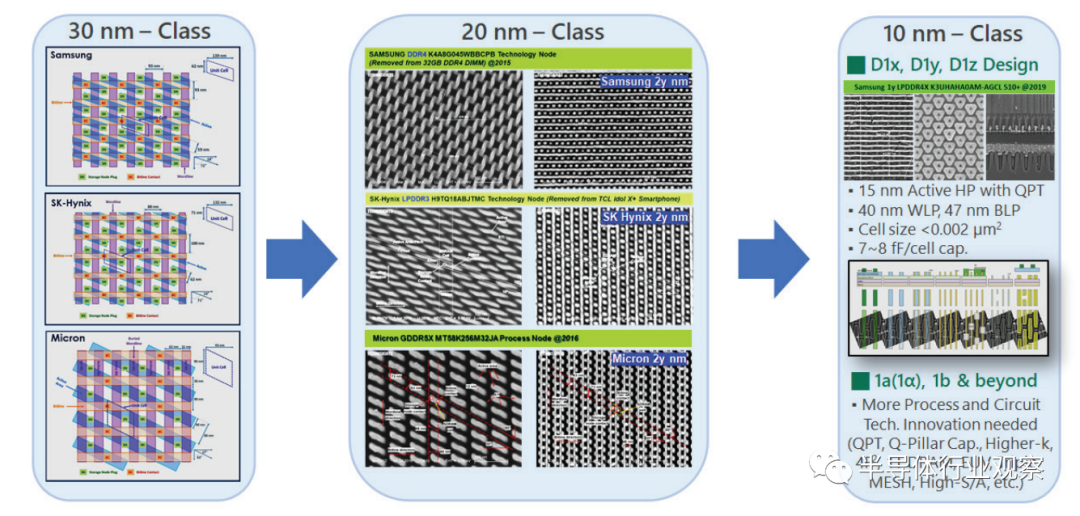

對于 10nm 級及以上的 DRAM 單元設計,應在其中加入更多創新的工藝、材料和電路技術,包括更高 NA EUV、4F2、1T DRAM、柱狀電容器、超薄 high-k 電容器介質和低 -k ILD/IMD 材料(圖 3)。

圖 3. 從 30nm 級到 10nm 級的 DRAM 單元設計和技術趨勢。需要更多創新技術來滿足單元電容、尺寸縮小和提升速度的要求。

圖 4 顯示了主要廠商的 DRAM 設計規則 (D/R) 趨勢。如果他們保持 6F2 DRAM 單元設計以及1T+1C 結構,2027 年或 2028 年 10nm D/R 將是DRAM 的最后一個節點。DRAM 單元微縮將面臨若干挑戰,例如 3D DRAM、減少row hammer(電路)、低功耗設計、刷新降低和管理刷新時間、低延遲、新功函數材料、HKMG 晶體管和片上 ECC。最受歡迎的功能將是“速度”和“感應裕量(sensing margin)”。三星用于 DDR5 和 GDDR6 的 HKMG 外圍晶體管技術就是增加 BL 感應裕量和速度的一個例子。

圖 4. DRAM D/R 趨勢顯示 6F2 單元設計的局限性。2027 年或 2028 年,10nm D/R 將是 6F2 DRAM 的最后一個節點。

-

電容器

+關注

關注

64文章

6228瀏覽量

99846 -

DRAM

+關注

關注

40文章

2319瀏覽量

183605 -

EUV

+關注

關注

8文章

607瀏覽量

86061

原文標題:DRAM制程

文章出處:【微信號:半導體設備與材料,微信公眾號:半導體設備與材料】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DRAM的基本構造與工作原理

DRAM與NAND閃存價格大幅下跌

SRAM和DRAM有什么區別

DRAM存儲器的基本單元

DRAM的分類、特點及技術指標

DRAM內存操作與時序解析

DRAM在計算機中的應用

HV-CMOS工藝制程技術簡介

DRAM制程分享

DRAM制程分享

評論