01 容差的概念

在工業生產中,通常把產品或零部件的參數(或質量特性值)的容許變化范圍成為容差。在機械、電子等不同行業,產品的研發、設計、制造等環節都會涉及容差。從工程角度看,容差是實際參數值的允許變動量,這里的參數既包括機械加工中的幾何參數,也包括物理、化學、電學等學科的參數。由于在生產過程中不能做到完全精確,就需要規定指標允許有一定的容許范圍,這就是容差。

如手表走時的誤差、產品測試過程中的設備狀態參數允許變化的范圍、棉紗單位面積的瑕疵點數等。

對于機械制造來說,容差通常稱為公差,指允許幾乎形狀和尺寸的變動量,如尺寸公差、形狀公差、位置公差等。

機械產品容差的目的是為了確定產品的幾何參數,使其變動量在一定的范圍之內,以便達到互換或配合的要求。從統計角度看,可以認為,某一指標的容許變化范圍成為容差;

從設計質量角度看,容差是一種允許極限,是從經濟角度考慮允許質量特性值的波動范圍,它是貫穿于產品設計、制造、裝配、使用與維護等整個壽命周期的重要技術信息。

02 容差在產品設計中的作用

容差有什么作用呢?對某一產品來說,若容差過松,往往生產成本較低,但產品質量與可靠性、裝配性能、維修性、保障性、測試性、安全性等可能難以達到設計要求;若容差過緊,雖然質量能得到要求,但制造需要更高的要求和成本。因此,容差在質量與成本之間扮演者重要角色,在設計和制造環節之間起著不可缺少的橋梁作用,它不僅影響產品的質量與可靠性、產品功能的實現、工藝方法的選擇,而且對產品的生產制造成本、使用維護成本及全壽命周期成本等產生顯著影響。

21世紀的制造企業面臨這全球性以知識為基礎的競爭,企業必須解決縮短生產時間T、提高性能質量Q、降低制造成本C、提供優質服務S以及保持清潔環境E等問題,應保證T、Q、C、S與E的和諧統一。

一方面,產品的質量是由顧客提出的,質量工作應源于顧客需求,終結于顧客滿意,制造商必須將顧客的聲音(voc)貫穿于整個供應鏈的所有行動之中。

產品的形成過程實際上就是產品質量的形成過程,影響質量的因素貫穿于產品的整個壽命周期,包括開發研制、采購、生產、檢測和測試、安裝于運行、技術服務和維護等幾個方面,僅對制造過程進行控制是不能保證產品質量的。

另一方面,在質量保證的過程中又要平衡相關成本。

但企業往往在質量和成本之間難以協調統一。從各個行業工程實踐經驗來看,設計決定了產品的固有質量和產品80%的成本。

因此,許多新的設計理念和制造模式,如六西格瑪設計(DFSS)、虛擬制造、網絡制造、敏捷制造、并行工程等應運而生,需要人們去探討和研究這些新設計理念和制造模式所涉及的理念和技術問題。質量企業的立足之本,成本是生產之道,縮減成本、提高質量是現代企業管理中經常提及的目標,而容差設計的課題就是解決質量與成本之間的平衡問題。

既然容差的作用非同小可,那么,如何設計容差的問題就顯得很重要了。容差設計是通過研究容差范圍與產品質量、成本之間的關系,對質量和成本進行綜合平衡的科學方法。工程實踐與理論均表明,容差設計的好壞很大程度上決定了產品最終質量與全壽命周期成本,從而決定企業獲利的情況。

因此,容差設計問題仍然是理論界應當而且十分關注的問題。

制造可靠的硬件要求你在設計階段就應考慮所有的容差。許多參考文獻討論了由于參數偏差引起的有源器件誤差,說明如何計算運算放大器失調電壓、輸入電流以及類似參數的影響,但是考慮無源元件容差的參考文獻卻寥寥無幾。確實考慮了元件容差的參考文獻也是從科學家的角度而不是從電路設計師的角度出發的。

然而,只要利用基本的電路公式和元件極限值來計算某個電路參數(如輸出電壓)在設備生命周期內在最壞情況下的取值范圍,你就能夠理解最壞情況的設計。最壞情況的設計允許元件數值有一個很寬的范圍,由此產生多種多樣的解決方案,其中有些解決方案可能是不可取的。

無源元件容差計算

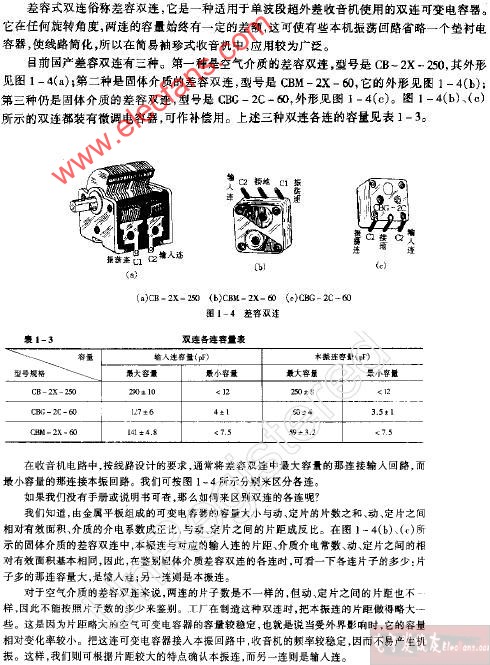

電阻器是所有電子電路的基本元件,所以你應該詳細地予以考慮。電阻器規定有購買容差P,你可以用百分比來度量P,常見的容差實例有0.5%、1%、2%、5%和10%。購買容差保證在你得到電阻器時其阻值在標稱值之內。一只電阻器的阻值在你購買時通常接近其極限值,這是因為許多制造商在為電阻器容差嚴格分級時選擇并消除分布中心,以便按更嚴格的容差等級銷售。

在裝配過程中,諸如焊接等外部應力都會使電阻器阻值改變。因此,在完工的裝配件出廠之前,電阻器阻值變化可能會超過購買容差。因為溫度、老化、壓力、濕度、裝配、陽光和灰塵等的外部應力都會改變元件的成分、尺寸和表面特性,所以元件值在其生命周期內會不斷變化。在工作過程中元件值的變化稱為漂移容差D,也以百分比來度量。

表1示出了估算的電阻器容差。注意,購買容差是與漂移容差不相關的,因為你可以通過微調來降低或消除購買容差,而漂移容差是在正常工作時發生的,除非在測量前系統進行校準,否則就會引起差錯。某些電阻器的漂移容差大于購買容差。

電阻器的制造工藝和工作環境決定漂移容差。因為過大的漂移會導致廢品,所以制造商們都采用穩定而可控的方法和抗漂移材料來制作容差嚴格的電阻器。在工廠中將漂移降低到最小的嚴格工藝和材料控制技術,在現場卻不能將漂移降至最小。表1中的漂移容差在-25℃~+85℃的環境溫度及合理外應力作用下是最壞情況的容差。除非制造商另有說明,溫度漂移是不可預測的,電阻器阻值可能會由于溫度的升高而增大或減小。在采用較低漂移容差之前,設計師應該向電阻器制造商咨詢。

電阻器通常用R1或R2表示。遵照這個命名法,你可以用(1±T)R1來計算最終的電阻器阻值,以得到最壞情況的電阻器阻值,其中T是用小數表示的總容差。你可以使用加/減符號,因為容差的極性取決于外部條件、制作方法、材料和內部應力。你在計算時應該假設最壞情況的容差極性。你必須將各個電阻器容差表示為正的或負的,利用無論哪一個容差都能得到最壞情況的計算結果,除非數據表說明所有的電阻器都以指定的方向漂移。在計算R1=10 kΩ、容差為5%的絕對最壞情況的最大值時,你應該使用(1+0.01(5)+0.01(5))R1=1.1R1=11 kΩ。而該電阻器的絕對最壞情況的最小值為(1-0.01P-0.01D)R1=(1-0.05-0.05)R1=9kΩ。

本文沒有詳細討論電容器容差的計算,你可以采用相同的方法對待電容器容差。由于各制造商用來制作電容器的方法差別很大,各類電容器之間的容差差別也比電阻器大得多。電解電容器的購買容差通常為80%,-20%,而有些玻璃電容器和NPO陶瓷電容器的購買容差則為1%。一般而言,最好將所有電容器容差增大至三倍,除非制造商的產品說明書另有不同建議。這種做法從保守的角度來看是錯誤的,不過在你不了解情況時就是一種很好的判斷方法。

非比例計量電路

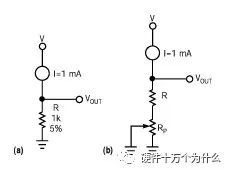

對于非比例計量電路,你必須取最大的電阻器容差,這是因為兩種容差不會相消。你可以利用公式VOUT=IR來計算輸出電壓,式中I是一個理想的1mA電流源,而R是一個容差為5%的電阻器(圖1a)。

VOUT=1mA (1±0.05±0.05)1 kΩ=(1±0.05±0.05)V。VOUT的范圍為0.9V≤VOUT≤1.1V,不過,你只要利用另一個電阻器來調整初始容差,就可將VOUT的范圍縮小(圖1b)。

圖1,非比例電路必須假設最大電阻器容差不會相消。基本的計算很簡單(a),你只要增加另一只電阻器來調節初始容差,就可以縮小VOUT的范圍(b)。

你可以如下計算可變電阻器阻值RP:

1、選擇小于最小計算值R=0.9kΩ的最接近的十進阻值R,該值為R=0.82kΩ;

2、計算所選電阻器的最小阻值如下:RMIN=(1-P-D)R=0.9(0.82)=0.738kΩ;

3、可變電阻器RP必須補償RMIN和1kΩ之差,所以RPMIN=1-0.738=0.262kΩ;

4、電位器的容差可能相當大,所以RP=RPMIN/(1-T)=0.262kΩ/(1-D-P)=0.262/0.8=0.328kΩ;

5、選擇RP=500Ω。

最終得到的阻值為:R=820Ω,RP=500Ω。有些工程師認為,最壞情況的設計程序太嚴格,而且要使用的電位器阻值較大,分辨率較低,電位器漂移誤差較大。有可能解決這一問題的一種方法是冒險降低電位器阻值,不過更好的解決方法是使用精度更高的部件。非比例電路必須考慮最大容差的偏移,因此,一個5%的購買容差會導致20%(±10%)的總容差。

比例計量電路

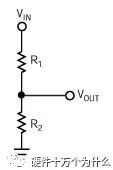

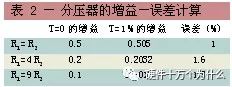

圖2和公式1中的分壓器是典型的比例計量電路。參照容差公式,你可以看到容差的某些部分在公式中相消。

圖2,比例電路可消去電阻器阻值的某些容差。

為了得到最大增益值,你要把R2的容差設定得大,而把R1的容差設定得小。由于R2的容差大,它就以(1+T)R2的形式出現在公式的各部分中。表2以四種電阻器比例列出了理想增益、最大增益和百分比誤差。要注意的是,當R1=R2時出現最小增益誤差,而且該增益誤差等于容差。該非比例電路必須取兩倍容差,即2T,而比例電路只取容差T。

當分壓器中兩只電阻器的容差同時很大或很小時,兩種容差就會相消。如果電阻器制造商保證在環境溫度變化時所有電阻器以相同方向按比例漂移,則溫度容差也會相消。

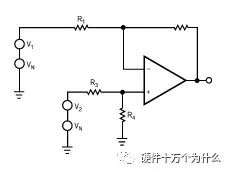

許多參考文獻說,你不可能用分立元件制作一個CMR(共模抑制)良好的精密差分放大器。差分放大器的容差分析說明了為什么這種說法是正確的。考慮圖3和公式2(參考文獻1)中的差分放大器電路,假設該放大器是理想的。

圖3,差分放大器利用比例電阻器來得到很高的CMR。

該電路的CMR是在無信號時測量的,所以V1=V2=0.0,公式2變成公式3:

當R1=R3和R2=R4時,增益為零,CMR為無窮大。實際上,電阻器容差和運算放大器誤差總是將CMR限制在大約100 dB以下。將公式3改寫為公式4,就使你的注意力集中到差分增益和電阻器容差上。公式4包含4個電阻器容差,因此有16個可能的誤差因子。如果你研究所有的可能性,就會看到誤差范圍從所有電阻器容差向同一方向變化時的零一直到2T/(1-T)。

當總容差為1%(對0.5%電阻器來說,為P+D)時,電阻器容差可以導致CMR的范圍從高達運算放大器極限值到低至-34.89dB。考慮到1%電阻器的購買容差和漂移容差,總的CMR可能低至-24.17 dB。你可以將這一誤差作為CMR誤差來計算,不過,在沒有共模電壓而有差分輸入信號的情況下,這一誤差就變成增益誤差。

采用分立元件的差分放大器是難以制作和微調的,所以大多數設計師都使用具有內置微調電阻器的IC差分放大器。廉價的IC差分放大器具有高達-86dB 的CMR。

你在分析電路以確保長期性能和可制造性時,要切記無源元件具有購買容差和漂移容差,而且漂移容差可能大于購買容差。你可以在制造過程結束時微調購買容差,但是,你或你的系統只能在進行測量之前調節漂移容差。非比例電路要取兩倍的電阻器容差,而比例電路可以將誤差降低到容差值。精確的差分放大器難以用分立器件制造,但是具有電阻器微調和匹配功能的IC通常可以得到-90 dB的CMR。

-

電阻器

+關注

關注

21文章

3779瀏覽量

62114 -

電路設計

+關注

關注

6673文章

2451瀏覽量

204158 -

元件

+關注

關注

4文章

912瀏覽量

36689 -

容差

+關注

關注

0文章

12瀏覽量

9171 -

無源元件

+關注

關注

1文章

1279瀏覽量

16945

原文標題:如何考慮電路設計的元件容差

文章出處:【微信號:電子匯,微信公眾號:電子匯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

通信應用中差分電路設計技術

電路設計中要考慮的電阻問題

【轉帖】電路設計中要考慮的電阻問題

最壞情況的電路設計對元件容差的考慮 電子資料

元件選擇和電路設計技術

如何考慮電路設計的元件容差

如何考慮電路設計的元件容差

評論