編者按

人工智能視覺芯片是一種可以同時獲取圖像、處理圖像的半導體芯片,這種芯片可以將獲取的圖像數據進行并行處理,最終輸出處理結果。人工智能視覺芯片的目標是在傳感器內部實現復雜圖像處理,包括圖像識別和分類。

中國工程院羅毅院士研究團隊在中國工程院院刊《Engineering》2022年第7期發表《感存算一體化智能視覺芯片的展望》一文。文章總結了感存算一體化智能成像系統中使用的兩種不同類型的架構(即在傳感單元內或附近進行計算),然后討論了未來的發展方向(包括與算法匹配的架構、3D集成技術、新型材料和先進器件)。文章指出,感存算一體化智能成像系統的最終目標是實現更高效的AI硬件,該硬件系統具有低功耗、高速、高分辨率、高識別準確率和大規模集成的特點,同時具有可編程性。另外,為了將感存算一體化智能成像系統商業化,需要在物理學、材料學、計算機科學、電子學和生物學等領域進行更深入的研究。

近年來,人工智能(AI)的應用變得越來越廣泛,其發展也隨著生物學、數學的進步而日漸成熟。然而,AI的發展也對系統的計算能力和能量效率提出了更高的要求,因此迫切需要新的硬件架構來滿足AI的需求。AI的目標是使機器獲得類似人的智能,當前的硬件體系在執行計算時仍然基于傳統的馮·諾依曼架構。首先通過傳感器得到物理信號,然后將信號傳輸至計算中心結合算法進行感知,這種信息處理的模式與人腦完全不同。以視覺為例,人類的視覺系統(包含視覺皮層)是高度緊湊和高效的,其中,視網膜上的數億光敏神經元與預處理、控制神經元相連接,能夠實現感光和信號預處理(增強圖像、提取特征等)。一旦光敏神經元檢測到冗余信號,視覺系統會將其弱化,僅將關鍵信息傳輸至大腦皮層進行深度處理。

目前常用的人工成像硬件系統的功能并不像人類視覺系統那樣,如電荷耦合器件(CCD)陣列和互補金屬氧化物半導體(CMOS)陣列,這類傳感器通過總線將圖像數據串行傳輸至存儲器和處理單元進行交互運算(即馮·諾依曼架構)。

盡管當前的成像硬件系統在傳感單元密度、響應時間和波長范圍方面優于人類視覺系統,但在執行復雜AI任務時,它們的功耗和延時變成了不可忽略的問題。在大多數圖像處理任務中,超過90%的圖像數據是冗余且無用的,隨著像素數量的快速增長,數據冗余量顯著增加,給模數轉換(ADC)和數據傳輸帶來了嚴重負擔,并限制了實時圖像處理技術的發展。因此,AI的發展會迅速消耗硬件資源,并產生對新型硬件系統的強烈需求。

受人類視覺系統的啟發,部分研究嘗試將一些處理任務轉移至圖像傳感器內,從而實現原位計算,并且減少數據傳輸。

在20世紀90年代,加州理工學院的Mead和Mahowald提出了人工智能視覺芯片,他們構想了一種可以同時獲取圖像、處理圖像的半導體芯片,這種芯片可以將獲取的圖像數據進行并行處理,最終輸出處理結果。早期的視覺芯片旨在模仿視網膜的預處理功能,但只能實現簡單圖像處理,如圖像濾波和邊緣檢測,而后逐漸提出在傳感器內部實現復雜圖像處理,包括圖像識別和分類,這也成為了人工智能視覺芯片的目標。此外,在2006年提出視覺芯片需要具備可編程功能,從而通過軟件控制靈活地處理各種應用場景。在2021年,Liao等總結了生物視網膜的原理,并討論了基于新興器件的智能視覺傳感器發展。Wan等概述了用于神經擬態傳感計算的電子、光學以及混合光電計算技術。

目前有兩種主要的智能視覺芯片架構。

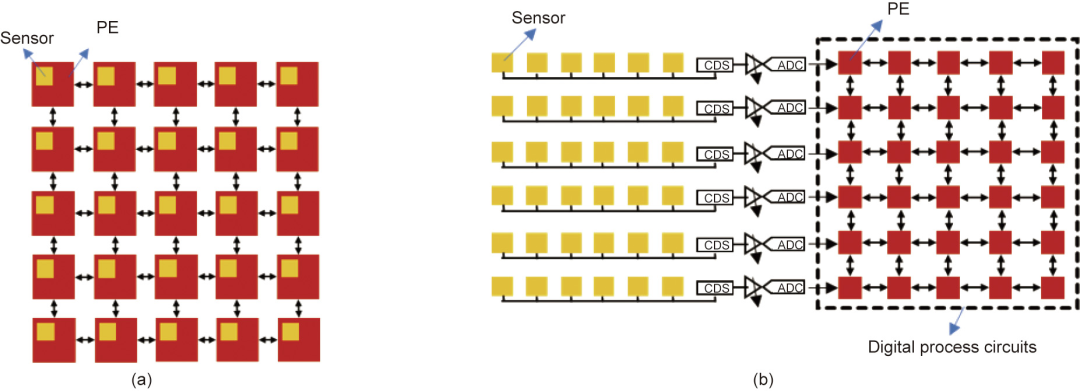

(1)架構一:傳感單元內部計算。這種架構的光電探測器被置于模擬存儲器和計算單元中,以組成處理元件(PE),然后利用PE電路來實現原位傳感功能,并處理傳感器獲得的模擬信號。這種架構如圖1(a)所示,其優勢在于具有高度并行處理速度。然而,模擬存儲器和計算單元占用了較大的面積,使得PE電路比傳統傳感單元大得多,這導致像素填充因子較低,并限制了成像分辨率。

(2)架構二:傳感單元附近計算。由于較低的填充因子,視覺芯片難以采用原位傳感和計算相結合的架構。相反,將像素陣列和處理電路物理分離,但仍然保持片上并行連接,這使得二者可以根據系統要求進行獨立設計和優化。這種架構如圖1(b)所示,首先通過總線從像素陣列中獲取傳感數據(模擬),并轉換成數字信號,然后在附近的處理單元內進行計算。這種架構具有廣域圖像處理、高分辨率和大規模并行處理的優勢,并且可以在數字處理電路中結合現有的AI算法(包括人工神經網絡等)。

目前,視覺芯片的神經元規模只有102~103個,遠少于視網膜和皮層(1010個),因此,感存算一體化智能視覺芯片需要更大規模的集成。其中一種方法是通過片上光學卷積神經網絡(CNN)和光學脈沖神經網絡(SNN)實現大規模高并行運算,以顯著提高計算效率。另一種方法是采用三維(3D)集成技術,使用硅通孔(TSV)垂直集成空間中的功能層(傳感器、存儲器、計算、通信等)。在2017年,索尼提出了一種3D集成視覺芯片,像素分辨率為1296×976,處理速度達到1000 fps。部分研究人員認為,3D集成芯片已經成為一種必然趨勢,但在架構設計和引線互連等方面仍然需要更深入的研究。研究證明,雖然短互連可以降低功耗和延遲,但由于層間距離較短可能會導致散熱難題。因此,解決3D集成的可靠性問題和提高性能至關重要。

圖1. 視覺芯片架構。(a)傳感單元內部計算;(b)傳感單元附近計算。CDS:雙精度采樣。

近些年來,在AI發展需求的驅動下,涉及新型材料和先進器件的技術不斷涌現,也為感存算一體化智能成像系統提供了新方案。

(1)具有探測和記憶功能的材料(DAM)。

光電突觸器件被視為構建感存算一體化智能成像系統的一種方式,并有望促進視網膜仿生技術的發展。研究發現,一些金屬氧化物(氧化物半導體、二元氧化物等)、氧化物異質結和二維(2D)材料在實現光電突觸器件方面有巨大的潛力。光電突觸具有臨時記憶能力和突觸可塑性,如短時程可塑性(STP)和長時程可塑性(LTP),可以通過光信號進行調制以完成實時圖像處理。這類器件有許多優點,它提供了一種非接觸式的寫入方法(光寫入),權重寫入過程具有高速并行的特點。

然而,這類器件仍然面臨一些挑戰,包括脈沖寫入下電導非線性變化和由于較大的照明強度而導致的高能耗。在寫入過程中,光刺激用于實現增強突觸活性,而電刺激用于抑制突觸活性。具體來說,器件的電導在光脈沖作用下逐漸增加,而在負電脈沖作用下則逐漸減小,這類似于生物突觸中的增強和抑制,器件的電導變化對應突觸的活性變化。此外,研究指出負光響應或者光刺激用于抑制突觸活性可以實現全光調制的復雜神經功能。目前大多數研究側重于在器件中模擬突觸行為[如興奮性突觸后電流(EPSC)、成對脈沖易化(PPF)、STP、LTP等],因為模仿人眼視網膜神經元仍然是一大挑戰。

為了模仿視網膜,光電突觸器件的大規模集成有待進一步研究。在DAM材料中,基于二元氧化物(如ZnO、HfO2、AlOx等)的器件具有結構簡單和CMOS兼容性的優點,這是大規模集成的關鍵因素。相反,與集成電路(IC)基礎結構不兼容的材料可以通過采用異質集成、異質外延、鍵合和三維異質集成等技術來實現。

(2)結合傳感器與存儲器的器件結構。

近些年來,隨著半導體器件的發展,部分研究提出采用先進器件代替PE電路,如新型存儲器件[如阻變存儲器(RRAM)和其他憶阻器等。例如,兩類器件通過串聯的方式來實現固有特性的結合,使傳感器陣列具有可編程性,并且將光學圖像轉變為易于識別的信息。

這種結構將單個像素的占地面積顯著降低到4F2的理論極限(F是工藝的特征尺寸),可以實現高填充因子的集成方式。然而,與CCD不同的是,該陣列不顯示破壞性讀出,也不顯示任何積分行為。在該陣列中,乘加運算(MAC)可以通過模擬域中的基爾霍夫定律直接實現。然而,大規模集成引起的串擾是一個亟待解決的問題。有研究報道了一種由單光子雪崩二極管(SPAD)和憶阻器組成的系統,用于處理脈沖事件形式的信息,從而完成實時成像識別。

隨著新型材料與器件的發展,感存算一體化智能成像系統也同樣需要新的架構和算法來適配其應用。

例如,深度學習算法(如DNN、CNN、SNN等)是目前較為成熟的圖像處理技術,而如何將其應用于感存算一體化智能成像系統是一個亟待解決的難題。SNN通過對時間并行編碼的神經信號進行編碼和處理,為提高計算效率提供了一種很有前景的解決方案。

本文總結了感存算一體化智能成像系統中使用的兩種不同類型的架構(即在傳感單元內或附近進行計算),然后討論了未來的發展方向(包括與算法匹配的架構、3D集成技術、新型材料和先進器件)。總之,感存算一體化智能成像系統的最終目標是實現更高效的AI硬件,該硬件系統具有低功耗、高速、高分辨率、高識別準確率和大規模集成的特點,同時具有可編程性。為了將感存算一體化智能成像系統商業化,需要在物理學、材料學、計算機科學、電子學和生物學等領域進行更深入的研究。

審核編輯:劉清

-

傳感器

+關注

關注

2557文章

51758瀏覽量

758935 -

CMOS

+關注

關注

58文章

5827瀏覽量

236750 -

圖像識別

+關注

關注

9文章

524瀏覽量

38559 -

人工智能

+關注

關注

1800文章

48107瀏覽量

242255 -

視覺芯片

+關注

關注

1文章

45瀏覽量

11552

原文標題:感存算一體化智能視覺芯片的展望

文章出處:【微信號:信息與電子工程前沿FITEE,微信公眾號:信息與電子工程前沿FITEE】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

到底什么是“通感一體化”?

【云智易申請】一體化機柜監控設計

什么是機電一體化

機電一體化系統

基于RISC-V開放架構的存算一體化芯片解決方案

曙光存儲一體化存力方案發布

什么是通感算一體化?通感算一體化的應用場景

感存算一體化智能成像系統中使用的兩種不同類型的架構總結

感存算一體化智能成像系統中使用的兩種不同類型的架構總結

評論