雖然很多轉換器具有三態輸出/輸入,但這些寄存器仍然在芯片上。它們使數據引腳信號能夠耦合到敏感區域,因而隔離緩沖區依然是一種良好的設計方式。

某些情況下,甚至需要在模擬接地層上緊靠轉換器輸出提供額外的數據緩沖器,以提供更好的隔離。

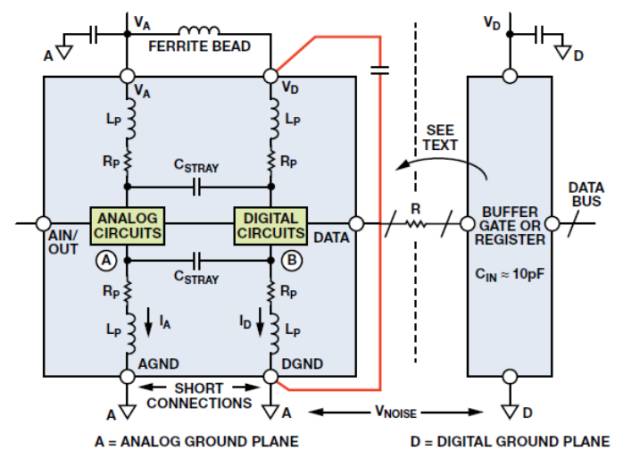

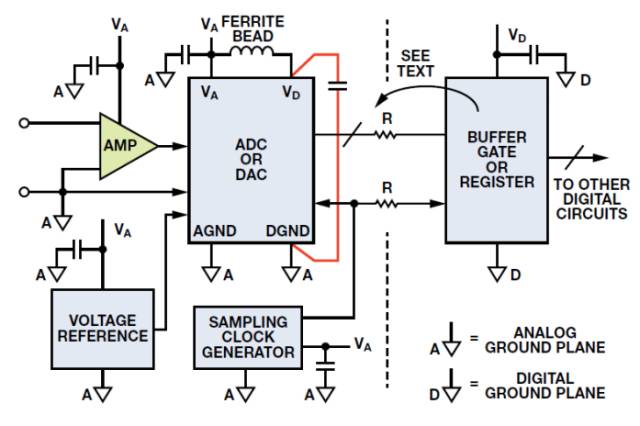

將數據緩沖器放置在轉換器旁不失為好辦法,可將數字輸出與數據總線噪聲隔離開(如圖 1 所示)。

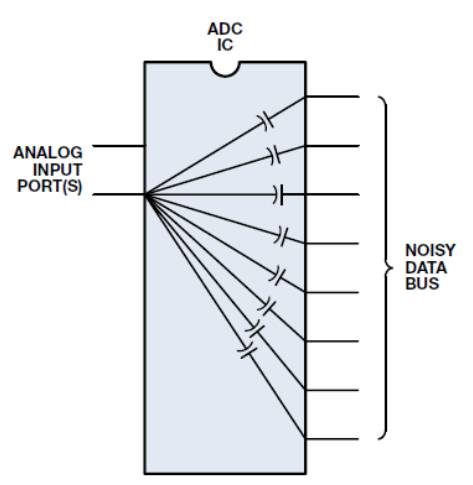

數據緩沖器也有助于將轉換器數字輸出上的負載降至最低,同時提供數字輸出與數據總線間的法拉第屏蔽(如圖 2 所示)。

圖 1.具有低內部數字電流的混合信號IC 的正確接地

圖 2. 在輸出端使用緩沖器/鎖存器的高速 ADC 具有對數字數據總線噪聲的增強抗擾度

ADC 輸出與緩沖寄存器輸入間的串聯電阻(圖 1 中標示為“R”)有助于將數字瞬態電流降至最低,這些電流可能影響轉換器性能。

電阻可將數字輸出驅動器與緩沖寄存器輸入的電容隔離開。此外,由串聯電阻和緩沖寄存器輸入電容構成的RC網絡用作低通濾波器,以減緩快速邊沿。

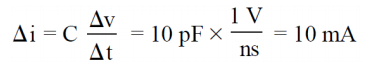

典型 CMOS 柵極與PCB走線和通孔結合在一起,將產生約 10 pF 的負載。如果無隔離電阻,1 V/ns的邏輯輸出壓擺率將產生10 mA的動態電流:

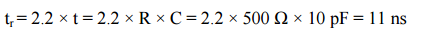

驅動10 pF 的寄存器輸入電容時,500 ? 串聯電阻可將瞬態輸出電流降至最低,并產生約 11 ns的上升和下降時間:

由于TTL寄存器具有較高輸入電容,可明顯增加動態開關電流,因此應避免使用。

緩沖寄存器和其他數字電路應接地并去耦至 PC 板的數字接地層。請注意,模擬與數字接地層間的任何噪聲均可降低轉換器數字接口上的噪聲裕量。

由于數字噪聲抗擾度在數百或數千毫伏水平,因此一般不太可能有問題。模擬接地層噪聲通常不高,但如果數字接地層上的噪聲(相對于模擬接地層)超過數百毫伏,則應采取措施減小數字接地層阻抗,以將數字噪聲裕量保持在可接受的水平。

任何情況下,兩個接地層之間的電壓不得超過 300mV,否則 IC可能受損。

最好提供針對模擬電路和數字電路的獨立電源。模擬電源應當用于為轉換器供電。

如果轉換器具有指定的數字電源引腳(VD),應采用獨立模擬電源供電,或者如圖 3 所示進行濾波。所有轉換器電源引腳應去耦至模擬接地層,所有邏輯電路電源引腳應去耦至數字接地層,如圖 3 所示。

如果數字電源相對安靜,則可以使用它為模擬電路供電,但要特別小心。

圖 3. 接地和去耦點

某些情況下,不可能將 VD連接到模擬電源。一些高速IC 可能采用+5 V電源為其模擬電路供電,而采用+3.3 V或更小電源為數字接口供電,以便與外部邏輯接口。

這種情況下,IC 的 +3.3 V引腳應直接去耦至模擬接地層。另外建議將鐵氧體磁珠與電源走線串聯,以便將引腳連接到+3.3 V數字邏輯電源。

采樣時鐘產生電路應與模擬電路同樣對待,也接地并深度去耦至模擬接地層。

針對高頻工作的接地

針對高頻工作的接地

一般提倡電源和信號電流最好通過“接地層”返回,而且該層還可為轉換器、基準電壓源和其它子電路提供參考節點。但是,即便廣泛使用接地層也不能保證交流電路具有高質量接地參考。

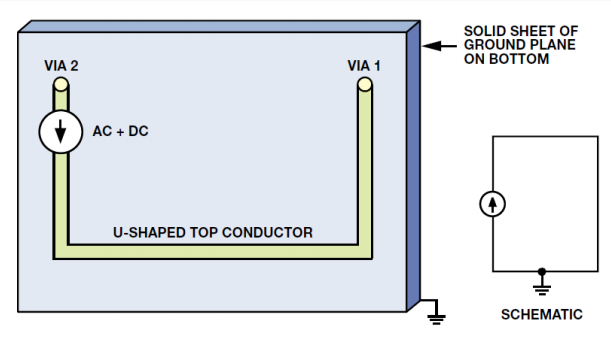

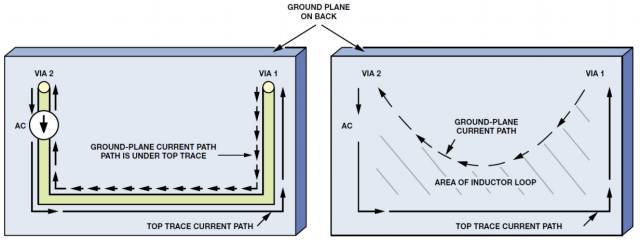

圖 4 所示的簡單電路采用兩層印刷電路板制造,頂層上有一個交直流電流源,其一端連到過孔 1,另一端通過一條 U 形銅走 線連到過孔2。

兩個過孔均穿過電路板并連到接地層。理想情況下,頂端連接器以及過孔 1 和過孔2之間的接地回路中的阻抗為零,電流源上的電壓為零。

圖4. 電流源的原理圖和布局,PCB 上布設 U 形走線, 通過接地層返回

這個簡單原理圖很難顯示出內在的微妙之處,但了解電流如何在接地層中從過孔1流到過孔2,將有助于我們看清實際問題所在,并找到消除高頻布局接地噪聲的方法。

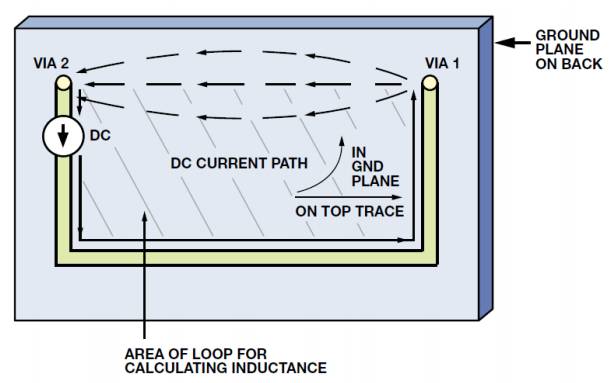

圖 5. 圖 4 所示 PCB 的直流電流的流動

圖 5 所示的直流電流的流動方式,選取了接地層中從過孔 1 至過孔 2 的電阻最小的路徑。雖然會發生一些電流擴散,但基本上不會有電流實質性偏離這條路徑。

相反,交流電流則選取阻抗最小的路徑,而這要取決于電感。

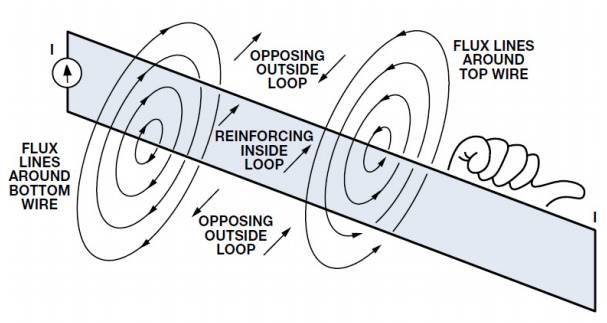

電感與電流環路的面積成比例,二者之間的關系可以用圖 6 所示的右手法則和磁場來說明。環路之內,沿著環路所有部分流動的電流所產生的磁場相互增強。

環路之外,不同部分所產生的磁場相互削弱。因此,磁場原則上被限制在環路以內。環路越大則電感越大,這意味著:對于給定的電流水平,它儲存的磁能(Li2)更多,阻抗更高(XL = jωL),因而將在給定頻率產生更大電壓。

圖 6. 磁力線和感性環路(右手法則)

電流將在接地層中選取哪一條路徑呢?自然是阻抗最低的路徑。考慮 U 形表面引線和接地層所形成的環路,并忽略電阻,則高頻交流電流將沿著阻抗最低,即所圍面積最小的路徑流動。

在圖中所示的例子中,面積最小的環路顯然是由 U 形頂部走線與其正下方的接地層部分所形成的環路。

圖 5 顯示了直流電 流路徑,圖 7 則顯示了大多數交流電流在接地層中選取的路徑,它所圍成的面積最小,位于 U 形頂部走線正下方。

實際應用中,接地層電阻會導致低中頻電流流向直接返回路徑與頂部導線正下方之間的某處。不過,即使頻率低至 1 MHz 或 2 MHz,返回路徑也是接近頂部走線的下方。

圖 7. 接地層中不含電阻(左圖)和含電阻(右圖)的交流電流路徑

采樣時鐘考量

采樣時鐘考量

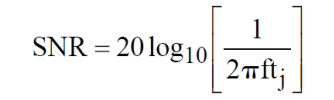

在高性能采樣數據系統中,應使用低相位噪聲晶體振蕩器產生 ADC(或 DAC)采樣時鐘,因為采樣時鐘抖動會調制模擬輸入/輸出信號,并提高噪聲和失真底。

采樣時鐘發生器應與高噪聲數字電路隔離開,同時接地并去耦至模擬接地層,與處理運算放大器和 ADC 一樣。

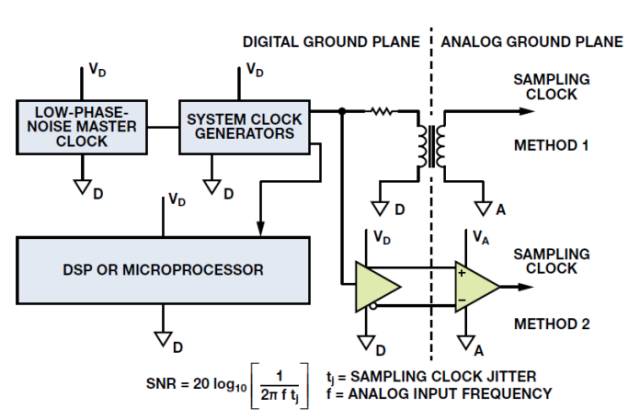

采樣時鐘抖動對ADC信噪比(SNR)的影響可用以下公式近似計算:

其中,f 為模擬輸入頻率,SNR 為完美無限分辨率 ADC 的 SNR,此時唯一的噪聲源來自 rms 采樣時鐘抖動 tj。

通過簡單示例可知,如果 tj = 50 ps (rms),f = 100 kHz,則 SNR = 90 dB,相當于約 15 位的動態范圍。

應注意,以上示例中的 tj 實際上是外部時鐘抖動和內部 ADC 時鐘抖動(稱為孔徑抖動)的方和根(rss)值。不過,在大多數高性能 ADC 中,內部孔徑抖動與采樣時鐘上的抖動相比可以忽略。

由于信噪比(SNR)降低主要是由于外部時鐘抖動導致的,因而必須采取措施,使采樣時鐘盡量無噪聲,僅具有可能最低的相位抖動。

這就要求必須使用晶體振蕩器。有多家制造商提供小型晶體振蕩器,可產生低抖動(小于 5 ps rms)的 CMOS 兼容輸出。

理想情況下,采樣時鐘晶體振蕩器應參考分離接地系統中的模擬接地層。但是,系統限制可能導致這一點無法實現。

許多情況下,采樣時鐘必須從數字接地層上產生的更高頻率、多用途系統時鐘獲得,接著必須從數字接地層上的原點傳遞至模擬接地層上的ADC。

兩層之間的接地噪聲直接添加到時鐘信號,并產生過度抖動。抖動可造成信噪比降低,還會產生干擾諧波。

通過使用小型射頻變壓器(如圖8所示)或高速差分驅動器和接收機,將采樣時鐘信號作為差分信號傳輸,可在一定程度上解決這個問題。

如果使用后者,應該選擇ECL來最大程度地減小相位抖動。在單個+5 V電源系統中,ECL邏輯可在地面和+5 V(PECL)之間連接,輸出端交流耦合到ADC采樣時鐘輸入。

不管是哪種情況,原始主系統時鐘必須從低相位噪聲晶體振蕩器產生。

圖 8. 從數模接地層進行采樣時鐘分配

-

寄存器

+關注

關注

31文章

5361瀏覽量

120876 -

adc

+關注

關注

99文章

6528瀏覽量

545341 -

數據緩沖器

+關注

關注

1文章

6瀏覽量

1860

原文標題:排坑指南:ADC的輸出處理

文章出處:【微信號:ZGDZGCS,微信公眾號:電子萬花筒】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ADC12J2700EVM和ADC12J1600EVM用戶指南

AMC1306的輸出數據是以曼徹斯特碼的形式輸出,處理曼徹斯特碼的時候應該以什么原則處理?

ADC高速采樣電路設計詳解之STM32踩坑

adc參數解析及選擇指南

TLV320aic33進行ADC的使用時,為什么沒有輸出?ADC使用時有什么要注意的地方嗎?

adc濾波運放輸出電壓的三個作用

硬件篇---電路設計之ADC采樣

排坑指南之ADC的輸出處理

排坑指南之ADC的輸出處理

評論