ADA4817 FastFET?運算放大器可實現1 GHz帶寬,輸入噪聲僅為4 nV/√Hz,是同類產品中速度最快、噪聲最低的放大器。雖然ADA4817單位增益穩定,但高頻極點的增益帶寬積從高增益時的410 MHz增加到單位增益時的1 GHz。不幸的是,該極點會降低相位裕量,導致頻率響應中出現不必要的峰值和階躍響應中的振鈴。在放大器的同相輸入端增加一個分立式RLC陷波濾波器可保持高帶寬和輸入阻抗,同時顯著降低峰值、提高增益平坦度并減少過沖。

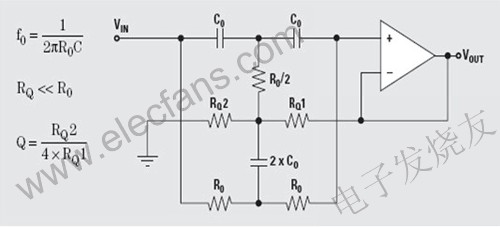

圖1所示的RLC陷波濾波器利用放大器的輸入特性來產生所需的結果。R與串聯LC并聯形成的陷波可以整形,以補償放大器和寄生電容產生的峰值。結果是帶寬為 1 GHz (?3 dB)、250 MHz 增益平坦度 (0.1 dB) 和小于 1 dB 的峰值,增益等于 1。

圖1.RLC陷波濾波器。

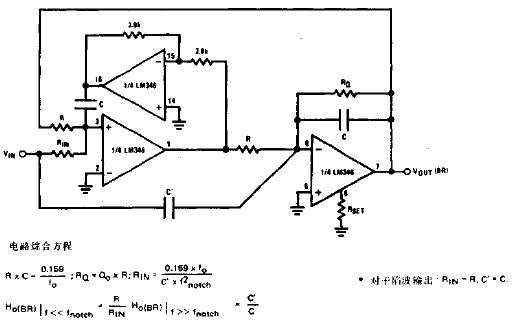

電阻、電容和電感的選擇至關重要。ADA4817的輸入阻抗類似于1.4 pF接地電容。圖2顯示了具有放大器輸入阻抗的RLC電路。將深入分析該電路以生成傳遞函數

圖2.陷波濾波器和放大器輸入阻抗。

其中 C1是放大器的輸入阻抗,ω = 2πf。圖3顯示了使用公式2和C的幅度響應1=1.4 pF.L 和 C 的值決定了傳遞函數與 0 dB 交叉的位置。R 的值決定了缺口的深度。

圖3.各種RLC槽口。

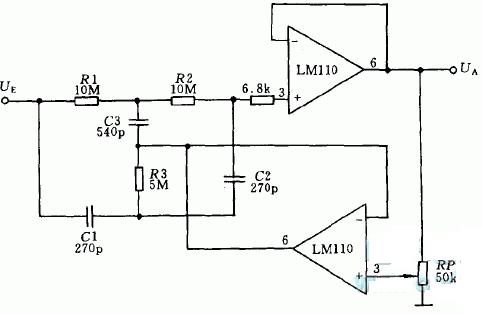

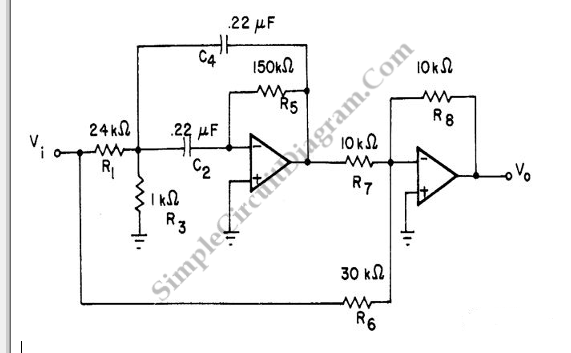

為了補償放大器的峰值,將放大器和濾波器的各個頻率響應相加,調整R、L和C以獲得最平坦的整體響應。這可以使用Excel或大多數電路仿真軟件來完成。凹口的形狀可以減少峰值,增加平坦度并減少過沖。圖4顯示了整體設計,其中陷波連接到同相輸入。

圖4.整體電路。

FET輸入ADA4817最重要的特性可能是其極低的輸入偏置電流。陷波電路保持了這一特性,同時保持了放大器的低失真和低噪聲。圖5顯示了帶陷波濾波器和不帶陷波濾波器的ADA4817的頻率響應。請注意,在保持平坦度的同時保持帶寬,并降低峰值。

圖5.有和沒有RLC。

圖6顯示了采用和不帶RLC電路的ADA4817的階躍響應。相同的設計也可用于塑造其他FET輸入放大器的頻率響應。這種設計保持了FET輸入的高輸入阻抗,但RLC接地可以與放大器一起使用,因為不需要這樣做。

圖6.帶或不帶RLC的脈沖響應。

結論

在ADA4817 FET輸入運算放大器前面增加一個分立式RLC陷波濾波器可顯著提高其性能。這種新穎而簡單的技術可降低峰值,提高增益平坦度并減少過沖,同時保持原始的1 GHz帶寬(–3 dB)。這種穩健、廉價的解決方案增加了三個新組件,但如果平坦的頻率響應、更低的過沖和增強的性能很重要,那么額外的成本可能是值得的。

審核編輯:郭婷

-

放大器

+關注

關注

145文章

14150瀏覽量

217504 -

濾波器

+關注

關注

162文章

8150瀏覽量

182211 -

運算放大器

+關注

關注

217文章

5719瀏覽量

176799

發布評論請先 登錄

OptiSystem應用:增益平坦濾波器優化

具有陷波電路結構的P波段低溫低噪聲放大器

LFCN-2500+ & PGA-105+ 濾波器&放大器

OPA642是寬帶、低失真、低增益運算放大器

濾波放大器如何降低功耗

高速陷波濾波器低功耗無線應用

雙T陷波濾波器拓撲結構圖

采用RLC陷波濾波器可降低放大器的頻率響應峰值與提高增益平坦度

評論