在 2022 年 12 月的 IEDM 會議上,Imec 展示了“Semi-damascene Integration of a 2-layer MOL VHV Scaling Booster to Enable 4-track Standard Cells”,我不僅有機會閱讀這篇論文并看到它的展示,而且采訪其中一位作者 Zsolt Tokie。

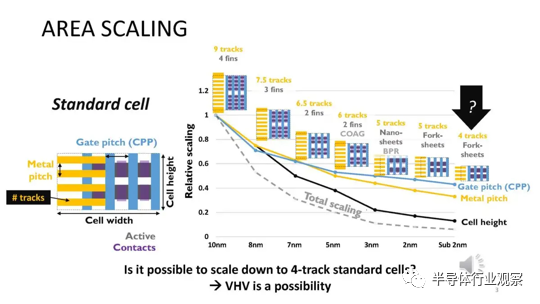

邏輯設計由標準單元構建,例如反相器、與非門、掃描觸發器和其他單元。標準單元的寬度是一定數量的接觸多晶硅間距 (CPP),具體取決于單元類型以及單元是否具有單擴散中斷或雙擴散中斷,例如,對于單擴散中斷,2 輸入 NAND 門的寬度為 3CPP,并且4CPP 寬,用于雙擴散斷裂。標準單元的高度的特征在于金屬 2 間距 (M2P) 乘以軌道(M2P 的數量)。

由于擴展 CPP 和 M2P 變得越來越困難,設計技術協同優化 (DTCO) 在使用減少軌道等技術進行擴展時變得越來越重要。目前最小單元一般為6軌,也出現了一些5軌單元格。在本文中,Imec 討論了實現 4 軌道單元的路由技術。

圖 1. 展示了 Imec 從 9 軌到 4 軌的路線圖。

在進入這里描述的路由技術之前,我想簡單地談談單元高度縮放的其他要求,簡單地談論 M2P 和軌道忽略底層設備結構。單元高度必須適合 n 和 p FET、n 到 p 間距和邊界寬度。從 FinFET 到水平納米片 (HNS) 的過渡通過從占據水平空間的多個鰭片切換到垂直方向的納米片堆疊來提供 n 和 p FET 的縮放。

Forksheets (FS) 和埋入式電源軌 (BPR) 等技術是 Imec 正在開發的用于解決器件高度問題的其他選項,例如 BPR 可以用基板中的高薄電源軌代替寬金屬 2 電源軌,從而減少邊界寬度,和 forksheets 可以減少 n-to-p 間距。

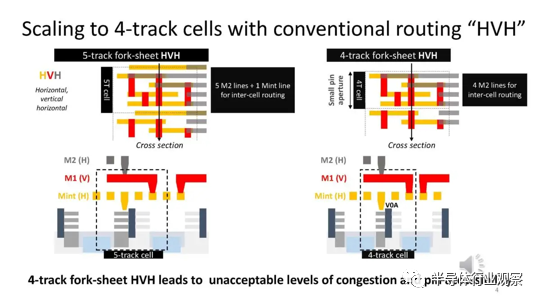

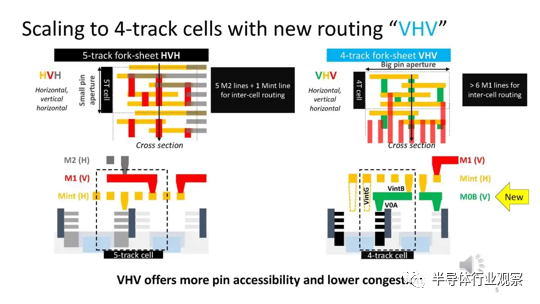

前沿工藝已經在 metal-1 層下引入了中間互連層,這些附加層在 Imec 的術語中通常稱為 Metal 0 (M0) 或 Mint。要獲得 4 軌道單元,單個 M0 層不足以互連設備。在這項工作中,M0A 和 M0B 添加到 Mint 下方,并且在一種新穎的工藝架構中,Mint 用作掩模以在 M0B 中執行尖端到尖端的切割。

Mint 通過 VintB 向下連接到 M0B,并通過 VintG 向下連接到柵極觸點。M0B 通過 Via V0A 向下連接到 M0A 的源極漏極。

圖 2 說明了具有 Mint 的 4 軌道單元中的擁塞,圖 3 說明了添加 M0B 和 M0A。

圖 2. 僅包含 Mint 的擁塞單元格。

圖 3. 通過添加 M0B 和 M0A 解決擁塞問題。

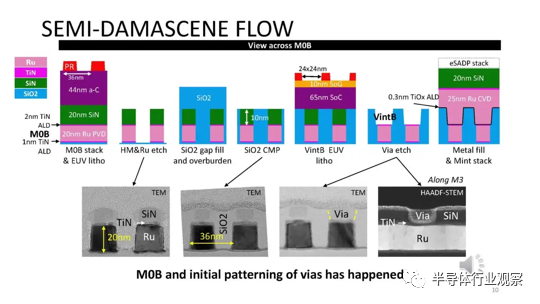

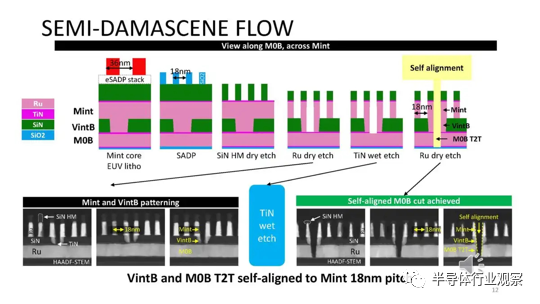

為了實現所需的尖端到尖端的緊密間距,M0B 使用自對準切割,其中 Mint 作為掩模,這需要減法金屬化工藝。這里使用的金屬化層是使用半鑲嵌技術沉積的釕(與銅不同,釕可以干法蝕刻),見圖 4。

圖 4. 半鑲嵌。

自對準 M0B 切割如圖 5 所示。

圖 5. M0B 自對齊切割。

通過添加兩層并使用自對準切割和 4 軌道單元可以互連。如果底層器件結構也可以實現所需的縮放,則此互連方案提供了通往 4 軌道單元和繼續縮放的路徑。

imec用四張圖,展示芯片未來發展路線圖

上個月中,SEMICON West 2022于舊金山的 Moscone 中心隆重舉行。展會前,Imec 在Moscone 中心附近的Marriott Marquee 舉辦了一場技術論壇。近年來,Imec 論壇已經從我介紹的工藝技術轉向更多的系統和應用論壇,但仍有一些工藝內容。

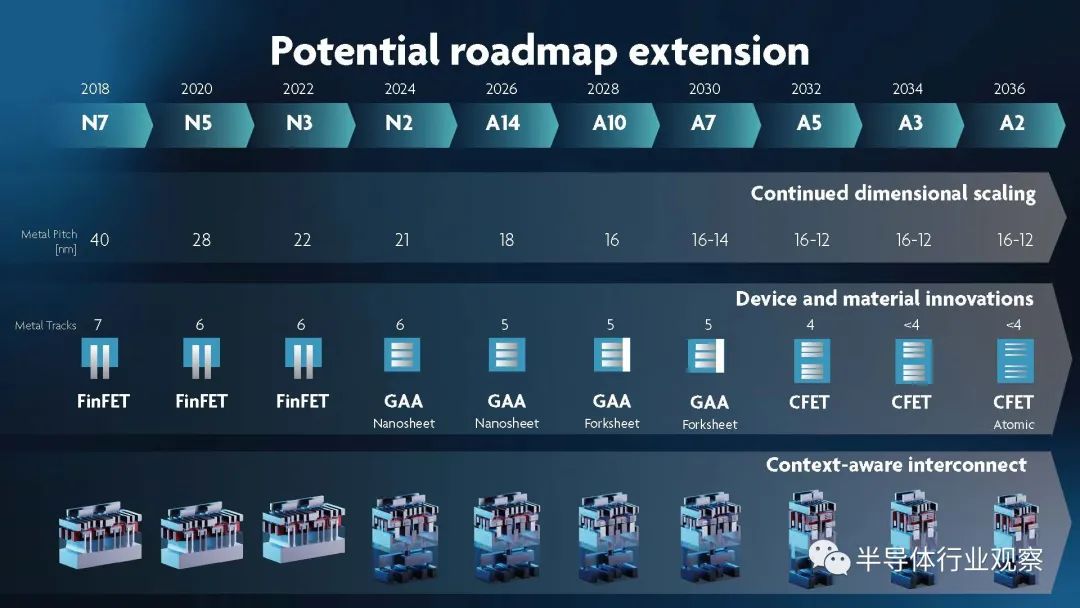

在 Luc Van den hove 的演講中,他展示了如圖 1 所示的路線圖幻燈片。

圖 1. Imec 路線圖

對于某些圈子里關于摩爾定律死亡的所有討論,Imec 路線圖展示了十多年的持續邏輯擴展。

在 N2 節點上,Imec 展示了向 Gate-All-Around (GAA) 納米片的過渡,三星正在為其 3nm 節點引入 GAA 納米片,英特爾和臺積電宣布用于 2nm(英特爾 20A)的 GAA 納米片。經過兩代納米片后,Imec 過渡到了 Forksheets。這是納米片的一種變體,可降低cell的軌道高度。

目前,我不清楚 Imec 的 Forkseheet 提案在設備制造商中的吸引力有多大,因為我真的沒有看到除Imec 之外的 供應商在Forksheets 上做任何的工作。在 Forksheet 的兩代之后,Imec 開始引入 CFET。供應商們在 CFET 方面做了大量工作,尤其是英特爾和臺積電。上一代 CFET 引入了原子級薄片。

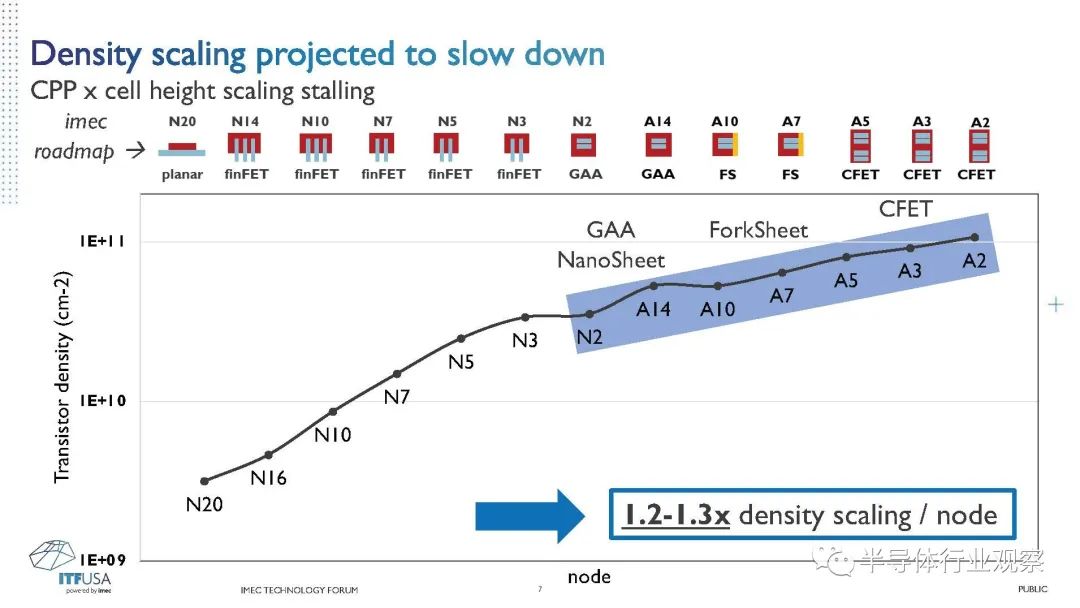

在 Geert Van der Plas 的演講中,關于潛在路線圖的更多細節被提出。

圖 2. Imec 路線圖晶體管密度

從圖 2 中可以看出,盡管密度繼續增加,但速率下降到每個節點的 1.2 倍至 1.3 倍。

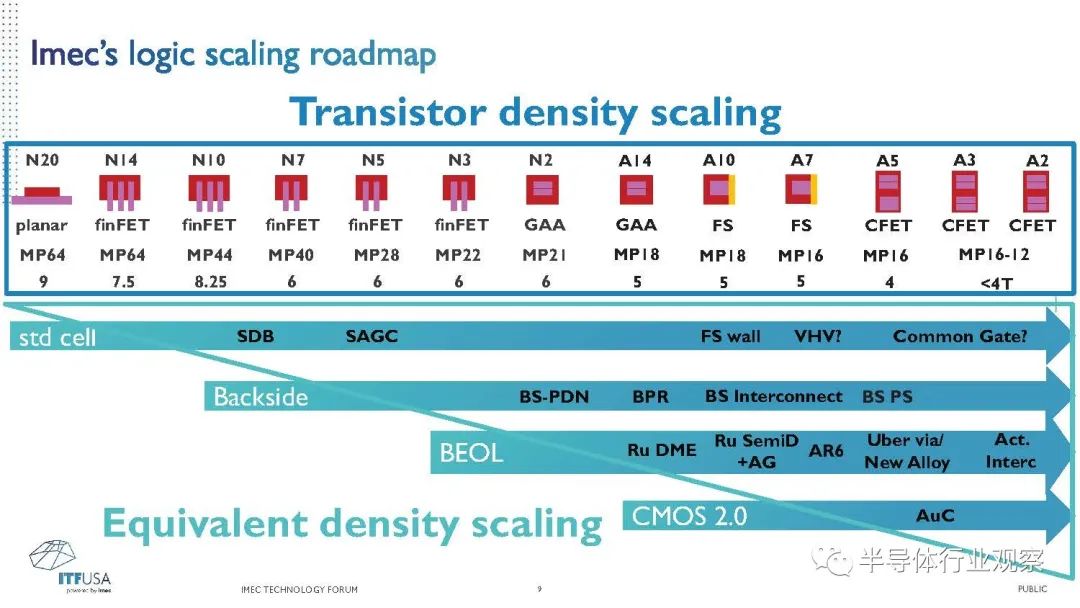

圖 3 顯示了標準單元、背面、生產線后端和 CMOS 2.0 創新的擴展路線圖的一些額外細節。標準單元微縮越來越受到設計-技術-協同優化 (DTCO) 的推動,例如單擴散中斷(single diffusion break)、有源柵極上的接觸(contact over active gate)、叉板墻(forksheet wall)等。晶圓背面正成為通過背面功率傳輸進行微縮的關鍵部分。BEOL 將需要新的材料和圖案化技術來支持更密集的設備。

圖 3. 晶體管縮放創新

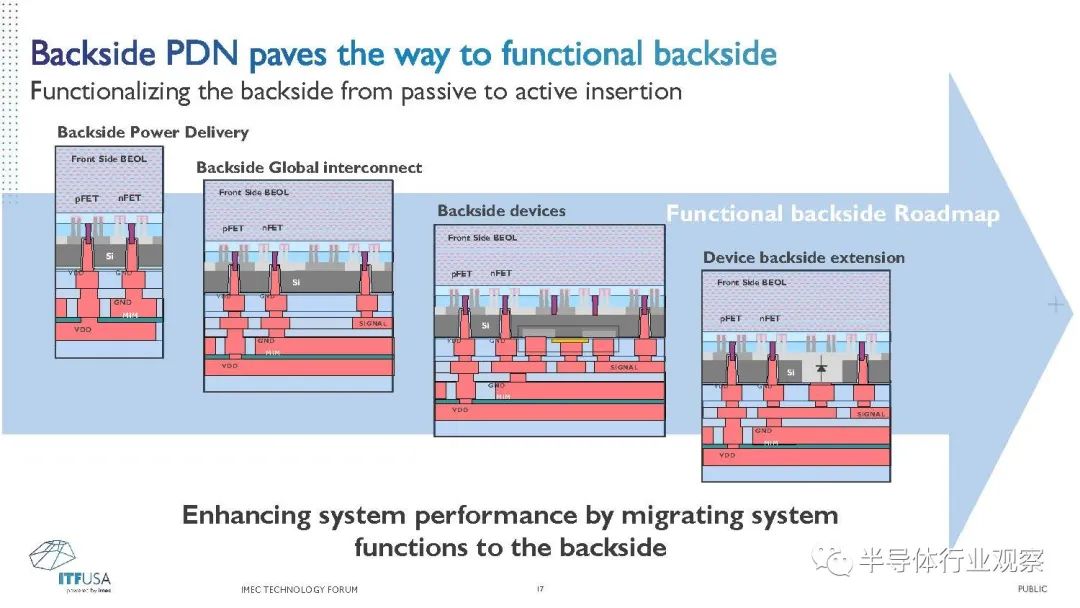

圖 4 展示了晶圓背面的一些選項,不僅提供背面功率傳輸,還可能包含有源器件。

圖 4. 背面選項

之后,我參加了由 Linx Consulting 主持的“與制造 3D 設備和結構相關的獨特挑戰,包括 GAA、3D DRAM 和 3D NAND”技術講座。

三星的演講者 Nabil Mistkawi 表示,在 7nm 及以下的drying 可能需要五個步驟來防止圖案塌陷(pattern collapse),這確實說明了前沿技術帶來的制造困難.

Screen 的 Ian Brown 更詳細地介紹了前沿的圖案塌陷以及cleaning 和drying挑戰。

對于邏輯器件,淺溝槽隔離/鰭的形成和多晶硅后蝕刻是關鍵步驟。納米片增加了很多表面,其中一些是隱藏的,水平納米片釋放非常關鍵。3D NAND 氮化硅去除需要一個快速的過程,但您必須避免二氧化硅沉淀。DRAM 有源和電容器的形成非常關鍵。

拉普拉斯壓力和表面張力會導致 3D 結構坍塌。Spin dryers已被 IPA dryers取代,但它們對表面狀態很敏感。今天,在干燥前修改親水表面使其具有疏水性是最先進的邏輯。

在工業早期,顆粒通過在其下方蝕刻去除,然后過渡到兆聲波(megasonics),但在 65nm 以下存在損壞問題。今天使用spin cleaners ,但如果壓力過高,它們會造成損壞。目前可用的最佳drying技術是超臨界二氧化碳,但由于設備成本的原因,它速度慢且成本高。

最后,應用材料公司的 Aviram Tam 討論了檢測和計量挑戰。3D 結構需要一種可以查看結構的技術。高能電子束能夠觀察結構并表征結構尺寸與深度的關系。隨著 EUV 光學覆蓋的出現不再足夠準確,這里也正在研究 eBeam。

未來二十年,芯片要到這些墻

近日,在 SEMICON West 開始之前,imec 舉辦了年度國際技術論壇 (ITF)。會上,imec 總裁兼首席執行官 Luc Van den hove 介紹了他對 20 年技術路線圖的看法,他表示,該路線圖比該行業過去幾十年取得的成就更加激進。而imec將利用我們的核心半導體專業知識,通過在半導體技術層面、系統和應用層面的共同創新。

Luc Van den hove首先表示,半導體行業長期以來一直遵循傳統的Dennard 縮放推動行業發展,它希望以更低的功耗和更低的成本提供更高的性能和更高的密度。“但這個一維版本的路線圖在未來可能已經不夠用了,”Luc Van den hove說。“我們將不得不針對特定應用調整我們的設備。”

傳統的擴展在功率、性能、擴展和成本方面遇到了多重障礙。而只是基于光刻的微縮也變得越來越難。“它并沒有停止,而是變得越來越難。我們習慣于從節點到節點的單個晶體管的性能改進一直在放緩。這就是我們必須進行大規模并行化的原因。”Luc Van den hove強調。

系統性能越來越受到核心處理器和內存之間的數據路徑限制的支配,這造成了數據處理限制,尤其是在 AI 應用程序中。“這就是我們所說的記憶墻。內存峰值帶寬無法跟上處理器峰值吞吐量,”Van den hove 接著說。

另一面墻是電源墻。“將所有功率輸入我們的芯片變得越來越難,而且從每個芯片中提取熱量也變得越來越難。因此,我們需要新的冷卻技術,”Van den hove 表示。

成本也在爆炸式增長,這是芯片未來面臨的另一堵墻,這個問題則需要通過復雜性增加來彌補。

“傳統的縮放顯然正在擊中許多這樣的墻,我們將不得不開發技術解決方案來真正拆除這些墻,以使摩爾定律得以延續,”Van den hove 說。

對于這種墻壁拆除,需要多種方法,包括尺寸縮小、新開關/晶體管的開發、第三維度的增加使用以及設計優化的系統級方法。

而按照Van den hove的說法,我們3 年內需要High NA EUV***

Imec 主持了一些關于 EUV 的最早工作,Van den hove 表示,隨著 EUV 進入大批量制造,光刻路線圖最近經歷了“驚人的推動”。“這發生在5納米節點。這比最初預期的要難得多。這要花更長的時間,但要感謝 ASML 和蔡司等公司的非凡奉獻和承諾,”他說。“我們相信當前版本的 EUV 可以擴展到2納米甚至更遠的節點,但要超越這一點,我們將需要下一個版本的 EUV。” 這將需要開發更大的鏡頭和新的系統平臺。光學器件必須符合驚人的規格,直徑為 1 米的鏡頭,其精度將超過 20 皮米。“如果我們將其推斷為地球的大小,這意味著我們必須以人類頭發粗細的精度來打磨地球。這令人難以置信,令人難以置信,”Van den hove說。“我們預計第一臺機器將在明年準備就緒。”

High NA EUV 的引入也將在工藝方面帶來許多挑戰。“為了以積極主動的方式解決這些問題,我們正在與 ASML 一起建立一個聯合High NA 實驗室,該實驗室圍繞第一臺原型機建造,將與 TEL 軌道連接,并配備最先進的計量能力。我們這樣做是因為及時引入High NA EUV 的挑戰將是巨大的,”Van den hove 說。“從第一臺 EUV 掃描儀到投入大批量生產,我們花了大約 10 年的時間。對于High NA,我們將有更少的時間,只有三年。為了避免在制造中引入這種情況,我們正在建立一個非常密集的計劃,以開發所有關鍵的支持構建模塊,例如掩模技術和使用濕式或干式紫外線抗蝕劑的材料。”

與此同時,Van den hove 還談了一些設備的創新

Van den hove 描述了幾項針對破壞性晶體管架構提出的創新,以實現進一步的擴展,包括由納米片堆疊構成的環柵設計(gate-all-around),以及一種稱為叉片(forksheet )器件的新晶體管概念,其中 N 和 P溝道晶體管靠得更近。“這種forksheet 設備,我們將其視為標準納米片概念的延伸,我們相信它將在相當于一納米一代的情況下推出,”Van den hove 說。他還描述了一種將 N 和 P 溝道晶體管堆疊在彼此頂部的選項,稱為互補 FET (CFET) 器件。

“很明顯,您可以在縮小單元尺寸方面實現另一個非常重要的步驟,但顯然是以更復雜的接觸方案來接觸源極和漏極區域為代價的。但我們相信,我們已經找到了開發的集成方案,可以通過優化外延工藝、圖案化工藝以及利用非常復雜的沉積工藝來實現接觸結構,從而實現這種晶體管,”Van den hove 說。

其他創新包括減少硅溝道的厚度以減少通道長度。這可以通過使用新材料來實現,如用二維材料、原子平坦的單層(例如,鎢或鉬的硫化物或硒化物)代替硅。“我們最近展示了使用 300 毫米設備制造的第一批設備,”他說。

Van den hove 表示,持續的尺寸縮放、新的晶體管架構、新材料的引入以及創新的互連架構(埋入式電源軌)相結合將是成功的秘訣。他說:“我們相信,我們可以為未來 8 到 10 代芯片提出路線圖——以 2 到 2 年半的節奏推出——這將為我們帶來未來 20 年的路線圖。

審核編輯:劉清

-

反相器

+關注

關注

6文章

311瀏覽量

43355 -

FET

+關注

關注

3文章

634瀏覽量

62983 -

觸發器

+關注

關注

14文章

2000瀏覽量

61185 -

MBPR

+關注

關注

0文章

2瀏覽量

1490 -

cpp

+關注

關注

0文章

10瀏覽量

2116

原文標題:關于芯片微縮,imec的新方法

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

光耦技術助力軌道交通智慧化建設

基于4G工業路由器的信息發布系統物聯網應用方案

遠程戶外監控組網方案,工業4G路由器ZR2000

告別繁瑣設置,輕松實現4G插卡路由器的快速設置

4G插卡路由器使用指南

4G插卡路由器:便攜式網絡解決方案的優勢與選擇

4G路由器的應用場景有哪些

告別傳統路由!4G路由器讓你輕松上網

4G路由器設置技巧,輕松實現高速暢游互聯網

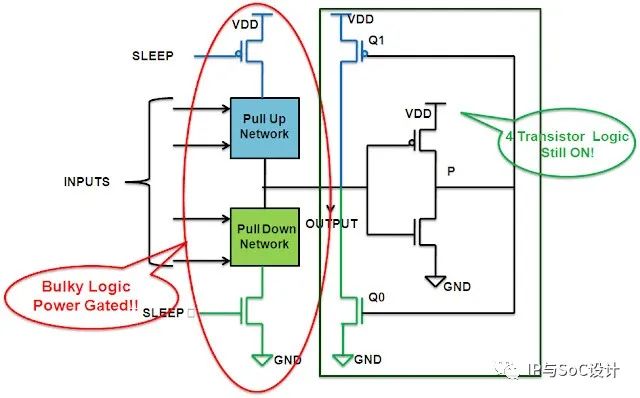

電源門控單元的實現原理

討論實現4軌道單元的路由技術

討論實現4軌道單元的路由技術

評論