1、引言

以交換機(jī)設(shè)計(jì)為例。在交換機(jī)設(shè)計(jì)前期,轉(zhuǎn)發(fā)表項(xiàng)是固化在交換機(jī)內(nèi)部的(給FPGA片內(nèi)BRAM初始值),但是在測(cè)試過程中,往往需要對(duì)表項(xiàng)進(jìn)行修改,如果直接修改BRAM的coe文件,則需要重新綜合、實(shí)現(xiàn)、生成bit文件,其中,綜合與實(shí)現(xiàn)耗時(shí)十分嚴(yán)重,設(shè)計(jì)規(guī)模越大,消耗的時(shí)間越長,而生成bit文件消耗的時(shí)間則相對(duì)固定。

針對(duì)上述問題,本文探究一種避免綜合與實(shí)現(xiàn),直接修改BRAM初始化值的方法,可以避免綜合、實(shí)現(xiàn)兩個(gè)步驟,修改BRAM初始值后,直接生成bit文件,可節(jié)約大量的時(shí)間。

2、 操作方法

(1) 完成初始設(shè)計(jì),綜合、實(shí)現(xiàn)(但是不生成bit文件) ;

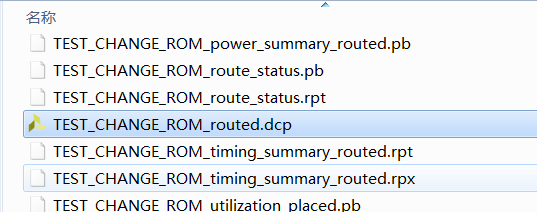

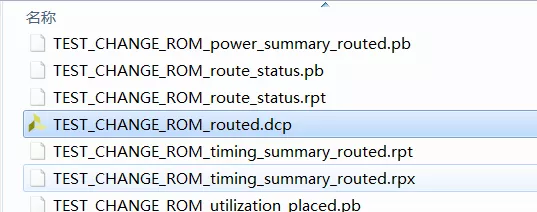

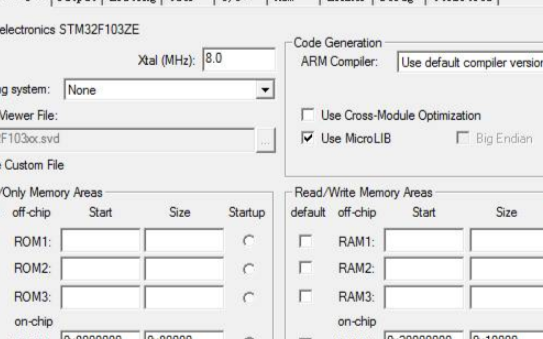

(2) 打開布線后的dcp文件(使用Vivado直接打開),如下圖所示:

(3) 找到想修改的目標(biāo)BRAM:

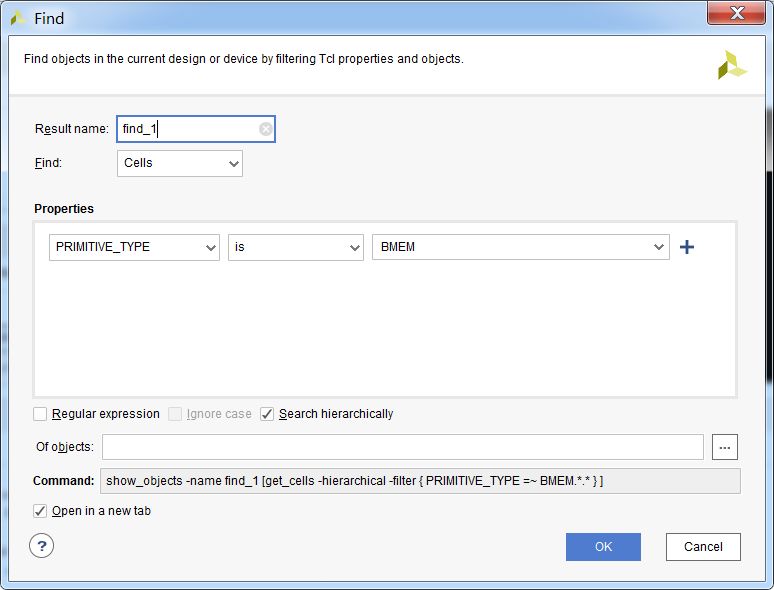

<3.1> ctrl+f ;

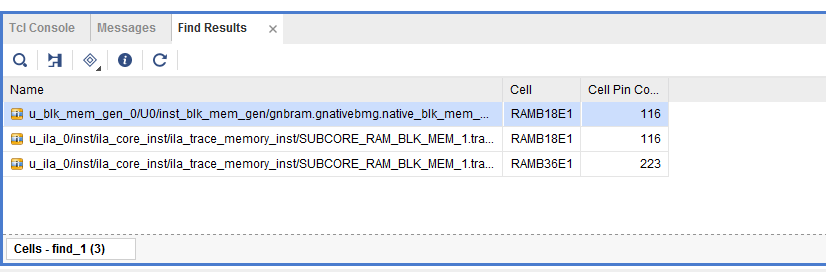

<3.2> 選擇需要修改的BRAM ;

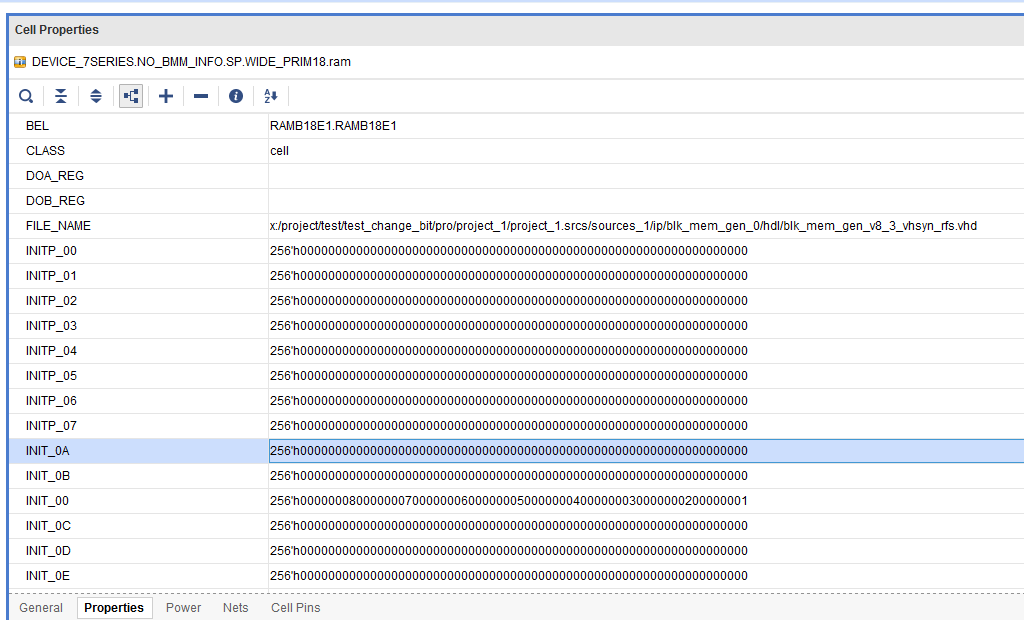

<3.3> 在properties界面,可以直接修改初始化文件(需要熟悉原語,其初始化方式與RAMB18E1相同);

<3.4>保存,退出;

<3.5>在主工程中打開實(shí)現(xiàn)設(shè)計(jì),按照相同的方式可以找到對(duì)應(yīng)的RAM與初始化值,可以發(fā)現(xiàn)初始化值已經(jīng)改變了 ;

<3.6> 生成bitstream文件。

3、 上板實(shí)測(cè)

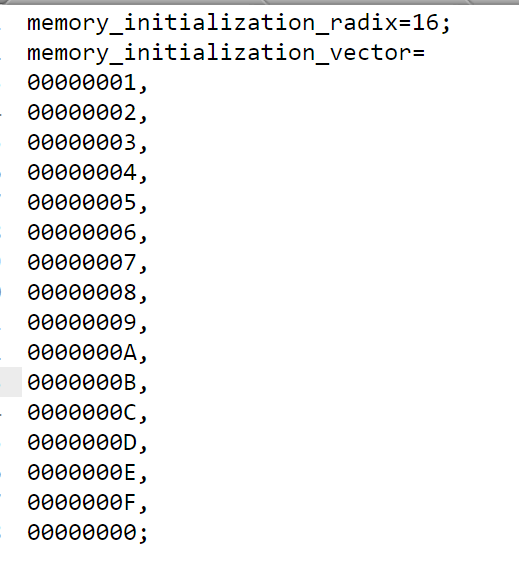

(1) coe文件:

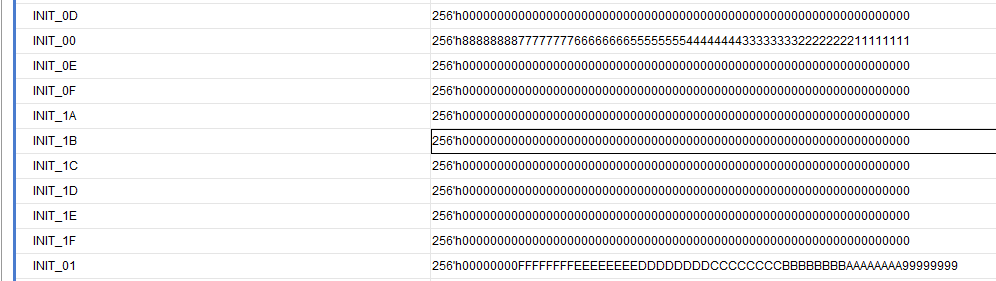

(2) 修改后的RAM初始化值

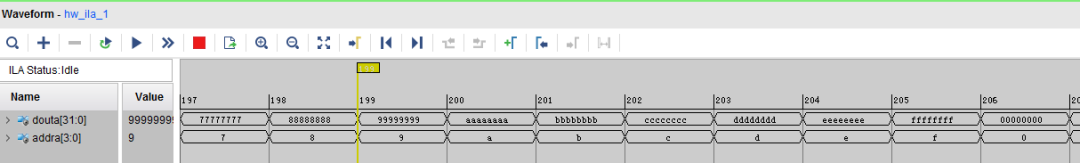

(3) 上板實(shí)測(cè)結(jié)果:

4、 結(jié)論

在僅修改BRAM初始化值的場(chǎng)景下,該方法可以大大減小從修改BRAM初始值到重新生成bitstream的時(shí)間,在交換機(jī)調(diào)試過程中,具有一定實(shí)用價(jià)值。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603017 -

交換機(jī)

+關(guān)注

關(guān)注

21文章

2637瀏覽量

99537 -

DCP

+關(guān)注

關(guān)注

0文章

30瀏覽量

17229 -

BRAM

+關(guān)注

關(guān)注

0文章

41瀏覽量

10956

原文標(biāo)題:Vivado 直接修改RAM初始化文件,避免重新綜合、實(shí)現(xiàn)的方法

文章出處:【微信號(hào):HXSLH1010101010,微信公眾號(hào):FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

有沒有一種方法最佳的方法實(shí)現(xiàn)初始化I/O引腳

初始化BRAM警告coe文件不存在

請(qǐng)問初始化BRAM后怎么顯示BRAM數(shù)據(jù)?

如何避免Spartan默認(rèn)初始化BRAM?

初始化BRAM primitaves出現(xiàn)錯(cuò)誤和循環(huán)漏洞的原因?

如何去編寫一種PWM初始化函數(shù)?

基于粒子群算法的同步時(shí)序電路初始化

一種多類原型模糊聚類的初始化方法

基于WRED協(xié)議的TCP連接初始化的優(yōu)化方法

修改BRAM初始化值的避免綜合與實(shí)現(xiàn)

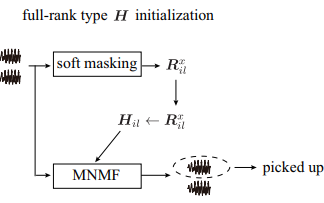

如何使用精確估計(jì)滿秩空間相關(guān)矩陣實(shí)現(xiàn)MNMF穩(wěn)定初始化的方法

探究一種避免綜合與實(shí)現(xiàn)直接修改BRAM初始化值的方法

探究一種避免綜合與實(shí)現(xiàn)直接修改BRAM初始化值的方法

評(píng)論