單顆芯片上集成的晶體管數量,已經超過全球人口總數,且還在提升過程中。雖然晶體管不像人這樣復雜,但將數十上百億顆晶體管在方寸之間安置好,顯然不是一個輕松的工作,而在先進工藝節點做開發的芯片設計公司,每日面對的就是各種“十億(Billion)”級別的工作,集成的晶體管以十億個起步,研發成本在十億元(人民幣)級別,面向的市場規模至少10億美元起。這樣浩大的工程,往往容不得出大的差錯,因為大的差錯通常不能通過軟件來繞開,需要改版,改版很可能就趕不上市場窗口期,趕不上市場窗口這個項目很可能將顆粒無收......

驗證難度在不斷增加

減少差錯,離不開驗證。芯片驗證的目的,就是利用各種語言、工具和方法來保證芯片設計的正確性,確保設計的功能指標符合規格書要求,且設計中的風險與缺陷(bug)已經得到有效控制,只有完成驗證的設計,才能進行流片,準備生產。驗證是一種防患于未然的手段,有了完備的驗證工作,才能保證研發投入的安全。

隨著集成度的增加,完成驗證所需要探索的空間和范圍不斷延伸,驗證正在變得越來越有挑戰。數十上百億個晶體管構成的模塊成千上萬,雖然通過設計重用和IP化開發可以大幅減少設計的工作量,但每個模塊之間的互連都會增加驗證的工作量,要遍歷設計中的風險與bug越來越難,不亞于“大海撈針”。驗證工作量在芯片開發工作中的比重不斷攀升,根據市場研究機構 Wilson Research Group的統計,2020年,在一個典型的ASIC項目中,驗證成本占研發總成本比例約為60%至80%,而在十五年前,驗證占研發成本的比例還不超過50%。此外,值得注意的是,當前約有68%的芯片項目,落后于規定時間,其中驗證工作難以按時完成是導致項目延誤的主要原因之一。

圖片來源:gsaglobal.org

當前,在大數據、物聯網等新興產業的帶動下,數據持續爆炸式增長,因而對算力、帶寬和存儲能力的需求持續增加,帶動芯片集成度與復雜度持續提升,但芯片開發周期并未得到相應的拉長,所以驗證工程師面臨最大的問題就是如何用更少的時間來完成更多的驗證工作,以保證驗證的效率和覆蓋率。

要實現這一點,就離不開新工具和新驗證方法學的引入。其中,基于機器學習(ML)和人工智能(AI)的新驗證方法學,頗有前景。近年來,機器學習與人工智能在EDA領域已經取得了諸多進展,例如,可以通過人工智能與機器學習,讓EDA工具自主搜索在設計空間中的最佳設計結果,傳統的設計空間優化一直是勞動密集型工作,往往需要數月工程時間,引入人工智能技術后,可以大幅加快開發進度。一個例子就是三星電子已在多個項目中采用新思科技的DSO.ai,不僅實現了更優的性能、功耗和面積(PPA),而且大幅降低了芯片的整體功耗,最重要的是,還為三星節省了數周的人工設計工作,從而明顯提升了開發效率,有效降低了開發成本。

同樣的,機器學習與人工智能在驗證空間檢索、覆蓋率收斂計算等方面比人工有較大優勢。通過使用基于AI/ML技術的驗證工具,工程師可以不必再花大量的時間去編寫數千個測試腳本以完成覆蓋率收斂,而是通過AI技術進行激勵分布診斷和根本原因分析,快速全面地將激勵反饋納入覆蓋范圍,從而加快覆蓋率收斂,極大縮短回歸周期。AI/ML技術還能檢出更多bug,包括測試平臺中的潛在問題,待測件(DUT)中的問題等。

圖片來源:semiengineering.com

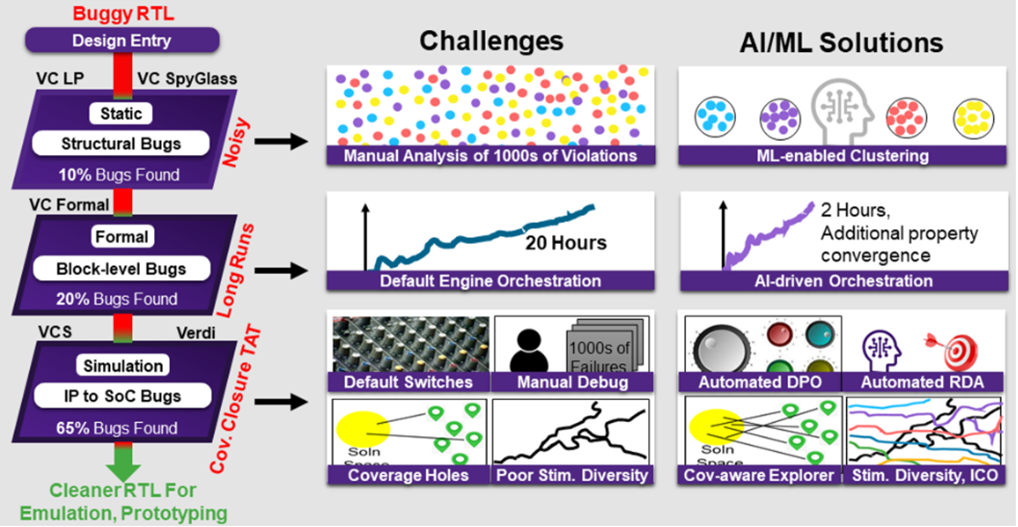

在靜態驗證、形式化驗證、仿真和調試等環節,都可以通過引入人工智能/機器學習技術而大幅受益。

人工智能在芯片驗證上的應用

靜態驗證是把時序驗證和邏輯功能驗證分開來做,不需要加激勵。當前的靜態解決方案主要包含跨時鐘域檢查(CDC)、跨復位域檢查(RDC)和低功耗設計結構檢查,靜態驗證階段可以檢測到常規項目約10%的錯誤。靜態驗證工具可以檢出數千個違規情況,這些違規情況的鑒別與處理往往耗時耗力,通過機器學習,可以對具有共性特征的違規情況(可能有數十上百條)合并到一個集群中,從而為工程師節省大量的時間和精力。

新思科技VC SpyGlass 平臺和新思科技 VC LP 綜合性靜態低功耗驗證解決方案能夠提供所有靜態驗證所需的功能,SmartGroup 技術可執行高級聚類,大幅減少需檢查的違規行為數量,而 RCA 則可以加速每個集群的調試。以ML技術為基礎的違規行為聚類與RCA相結合,可將常規芯片項目靜態驗證的調試效率提升近 10 倍。

形式化驗證可提供針對一組屬性的設計綜合分析,也不需要激勵。分析過程會考慮所有可能的合法輸入序列。形式化驗證可以檢測出在仿真過程中難以觸發的深層錯誤,形式化驗證檢出的錯誤占項目總體錯誤比例通常約為20%。形式化驗證工具通常有數十個求解器,以處理設計中需要驗證的成百上千個屬性,在過去20年,形式化驗證技術已經取得了很大進步,而人工智能技術又在提高收斂性和優化結果方面,讓形式化驗證更進一步。新思科技的VC Formal是業內首個在求解器編排、回歸和調試中利用到機器學習技術的形式化驗證工具,借助機器學習,VC Formal RMA可將運行速度提升2至5倍。

仿真是芯片驗證的核心,一個大型SoC的仿真可能包含數千個測試,且每天都在機器上跑仿真。在仿真過程中檢測出的錯誤,約占項目總數的65%。在仿真過程中,檢測出問題后需要對設計進行修改,然后再次仿真,這就是回歸測試,修改可能會造成新的問題,所以頻繁的回歸測試在驗證中是常態,這也是影響仿真效率的主要因素。通過引入AI技術,可以加速回歸測試的速度。

在進行仿真和回歸測試時,EDA仿真器大量的選項和開關對設計的性能有重大影響,驗證者需要有時間和專業度,才能把特定設計和測試平臺的仿真器設置做好,而不停地回歸測試很可能會造成誤操作,通過機器學習來維護仿真器的選項和開關設置,可以極大地提高回歸性能和效率。

新思科技 VCS仿真器中的動態性能優化 (DPO) 技術就是利用 AI 來改進仿真性能,與手動進行仿真器設置相比,DPO可使仿真運行速度提高 1.3 - 2 倍。此外,通過基于機器學習的智能覆蓋率優化(ICO),可以優化受約束的隨機激勵的統計質量,并提供影響覆蓋率的測試問題分析結果,ICO可以將覆蓋率的收斂速度提高2-3倍。

為實現目標覆蓋率,工程師要運行無數次仿真回歸,每次回歸失敗時,團隊都需要修復錯誤以重新測試,如果全部手動處理,則將給工程項目帶來巨大負擔。借助人工智能技術,可以解決調試難題。新思科技Verdi 自動調試系統中的回歸調試自動化 (RDA) 功能可自動分箱、探查并發現回歸失敗的根本原因。RDA 利用人工智能算法對回歸失敗進行分類和分析,并確定設計和測試平臺中失敗的根本原因,該技術縮短了RCA時間,并將整體調試效率提高了2倍。

總結

驗證已經成為大型SoC開發過程中工作量最大的部分,驗證負責人經常被問到兩個靈魂問題:什么時候能測完?還有沒有嚴重的bug?

要回答這兩個問題并不容易,但回答不了這兩個問題,往往意味著難以流片。在人工智能和機器學習技術加持下,驗證效率和結果持續得到優化,對驗證人力的需求得到了緩解,任務的增量不再那么可怕,以技術的手段來解決遇到的技術難題,這就是工程師們的使命吧。

審核編輯:劉清

-

asic

+關注

關注

34文章

1204瀏覽量

120544 -

EDA工具

+關注

關注

4文章

268瀏覽量

31823 -

晶體管

+關注

關注

77文章

9702瀏覽量

138430 -

機器學習

+關注

關注

66文章

8423瀏覽量

132752 -

PPA

+關注

關注

0文章

21瀏覽量

7498

原文標題:AI/ML助力,SoC驗證按期完工不再可望不可及

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何設計和驗證SoC

SoC設計與驗證整合

SoC驗證平臺的FPGA綜合怎么實現?

SoC驗證未來將朝什么方向發展?

X-CUBE-AI和NanoEdge AI Studio在ML和AI開發環境中的區別是什么?

如何在STM32上開始使用ML &AI的選項?

SoC芯片驗證技術的研究

基于FPGA的驗證平臺及有效的SoC驗證過程和方法

統一AI/ML解決方案加速驗證曲線收斂

BG24采用CSP小型封裝助互聯醫療設備引入AI/ML功能

超低功耗 Wi-Fi + AI/ML方案成為AIoT 串連云端的天作之合

Supermicro推新AI存儲方案,助力AI和ML應用加速

是德科技推出AI數據中心測試平臺旨在加速AI/ML網絡驗證和優化的創新

AI/ML助力SoC驗證按期完工

AI/ML助力SoC驗證按期完工

評論