數字門級電路可分為兩大類:組合邏輯和時序邏輯。鎖存器是組合邏輯和時序邏輯的一個交叉點,在后面會作為單獨的主題處理。

組合邏輯描述了門級電路,其中邏輯塊的輸出直接反映到該塊的輸入值的組合,例如,雙輸入AND門的輸出是兩個輸入的邏輯與。如果輸入值發生變化,輸出值將反映這一變化,組合邏輯的RTL模型需要反映這種門級行為,這意味著邏輯塊的輸出必須始終反映該邏輯塊當前輸入值的組合。

SystemVerilog有三種在可綜合RTL級別表示組合邏輯的方法:連續賦值語句、always程序塊和函數。接下來幾篇文章將探討每種編碼風格,并推薦最佳實踐編碼風格。

always和always_ff

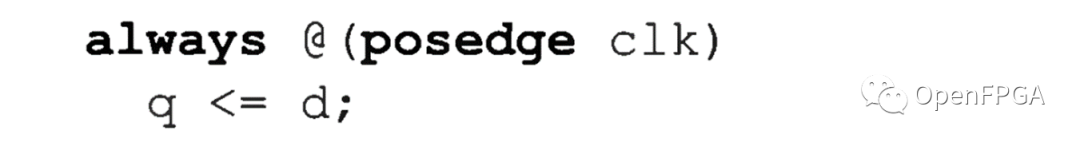

通用的always程序可以用來為任何類型的邏輯建模,包括組合邏輯、時序邏輯(觸發器)和電平感應的時序邏輯(鎖存器)。為了讓通用的always程序對觸發器行為進行建模,always關鍵字后面必須緊跟一個敏感度列表,指定時鐘信號的posedge或negedge,如:。

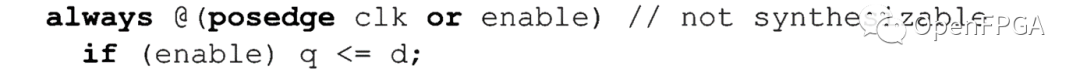

盡管這個例子在功能上是準確的,但是通用的always程序并不要求也不強制執行前面一節中列出的任何綜合要求。下一個例子在語法上是合法的,但是不可綜合。

這個例子可以在仿真中編譯和運行,沒有任何警告或錯誤提示,但是綜合編譯器在試圖編譯這個例子時,會報告一個錯誤。它不符合要求,即除了時鐘和異步置位或復位的邊沿之外,其他信號都不能包含在靈敏度列表中。對RTL仿真的仔細驗證會發現,即使在沒有發生時鐘觸發的情況下,觸發器的狀態也會在每次enable改變值時更新其內部存儲。門級的觸發器沒有這個功能。

always_ff過程也需要一個敏感度列表,指定一個時鐘的posedge或negedge,但是always_ff也執行上一節中列出的許多綜合要求。SystemVerilog標準要求所有軟件工具在以下情況下報告錯誤。

過程的主體包含#,wait,或者@時間控制延遲時,將阻止過程的執行,直到要求的仿真時間。

在程序中,有一個對任務的調用(因為任務可以包含延遲)。

任何其他存儲過程、連續賦值或輸入端口的賦值與always_ff存儲過程的變量相同。

IEEE標準還建議(但不要求)軟件工具檢查其他綜合限制,如不正確的靈敏度列表。設計工程工具,如綜合編譯器和lint檢查器(檢查編碼風格)執行這些可選的檢查,但大多數仿真器不對always_ff程序執行額外的檢查。這些錯誤和可選的額外檢查有助于確保具有時序邏輯的RTL模型既能正確仿真,又能正確綜合(仿真和綜合后功能相同)。

always_ff過程之后必須有一個符合綜合要求的敏感性列表。靈敏度列表不能像always_comb可以推斷靈敏度列表那樣從程序的主體中推斷出來。原因很簡單:時鐘信號在always_ff過程的主體中沒有命名。時鐘的名稱,以及時鐘的哪個邊沿觸發了存儲過程,必須由設計工程師在靈敏度列表中明確指定。

| 最佳實踐指南8-1 |

|---|

| 使用SystemVerilog always_ff RTL專用存儲過程來模擬RTL時序邏輯。請不要使用通用的always過程。 |

always_ff RTL專用程序強制執行上一篇文章中所要求的綜合風格,以正確模擬時序邏輯行為。

審核編輯:劉清

-

鎖存器

+關注

關注

8文章

906瀏覽量

41550 -

RTL

+關注

關注

1文章

385瀏覽量

59849 -

Verilog語言

+關注

關注

0文章

113瀏覽量

8277 -

門級電路

+關注

關注

0文章

15瀏覽量

1995

原文標題:數字硬件建模SystemVerilog-時序邏輯建模(2)always和always_ff

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

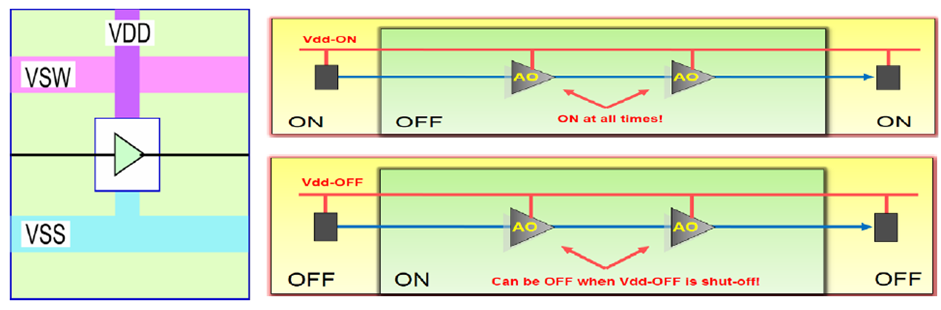

什么是always on buffer?什么情況下需要插always on buffer?

什么是AO/DI (Always On-line/Dynam

initial和always兩者的關系分析

你們知道always,assign和always@(*)之間的區別嗎

assign組合邏輯和always@(*)組合邏輯的區別

數字硬件建模SystemVerilog篇OpenFPGA介紹

SystemVerilog中的always語句塊

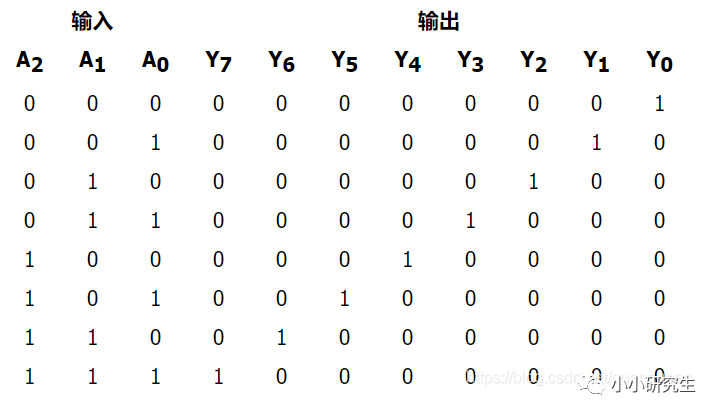

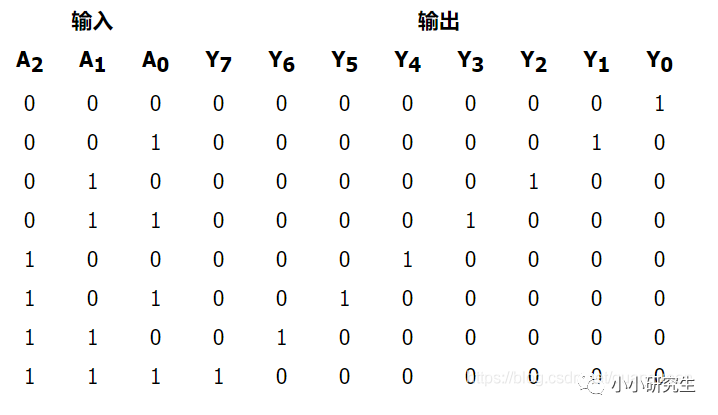

FPGA設計:always組合邏輯塊的講解和譯碼器的實現

always組合邏輯塊的講解和譯碼器的實現

SystemVerilog相比于Verilog的優勢

探討always和always_ff的編碼風格

探討always和always_ff的編碼風格

評論