大家知道,為實現低相位噪聲性能,尤其是超低相位噪聲性能,必須使用低噪聲電源才能達到最佳性能。但文獻上沒有詳細說明如何通過一種系統化方法來量化電源噪聲電壓電平對相位噪聲的影響。本文旨在改變這種狀況。

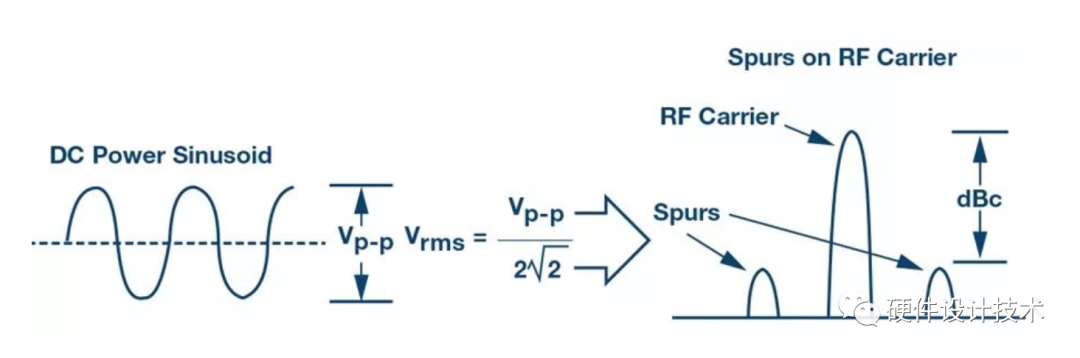

本文提出了電源調制比(PSMR)理論,用來衡量電源缺陷如何被調制到RF載波上。通過電源噪聲對RF放大器相位噪聲的貢獻來驗證這一理論;測量結果表明,可以計算并且相當準確地預測該貢獻。基于此結果,本文還討論了描述電源特性的系統化方法。

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

電壓電平

+關注

關注

0文章

25瀏覽量

7506 -

PSRR

+關注

關注

0文章

153瀏覽量

39324 -

電源噪聲

+關注

關注

3文章

151瀏覽量

17474 -

RF放大器

+關注

關注

0文章

29瀏覽量

3503

原文標題:PSMR與PSRR不同之處

文章出處:【微信號:硬件設計技術,微信公眾號:硬件設計技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DAC相位噪聲性能改進包含殘余相位噪聲測量方法和最佳穩壓器選擇

在于,在測試設置中需要額外的DAC。但是,優點是可以應用于系統級分析預算,作為DAC相位噪聲貢獻的一種非常好的指標。 圖4a. 使用鑒相器方法

發表于 03-19 22:09

一種更通用的方法來監測處理器中的電壓噪聲

的是,這種專門的電路還不是大多數高端Arm系統的標準功能。在我們最近與塞浦路斯大學的合作研究中,我們成功地開發了一種更通用的方法來監測處理器中的電壓

發表于 11-01 14:48

一種改進的相位噪聲抑制方法

隨著衛星數傳容量急劇增加,高階調制解調方式在實際中被廣泛采用,衛星通信系統的性能有了更高的要求。針對這一現狀,給出一種基于最小均方根的相位噪聲

發表于 01-04 17:13

?14次下載

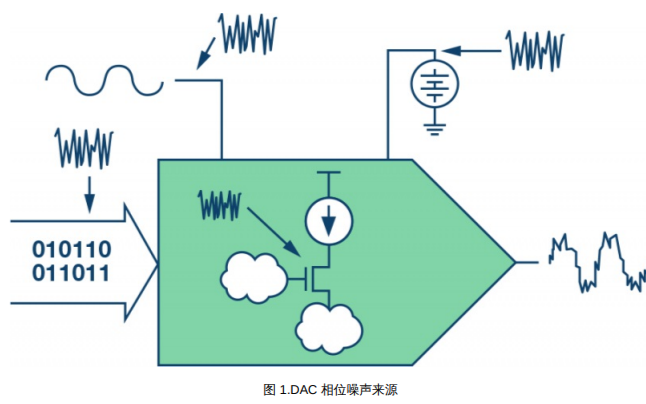

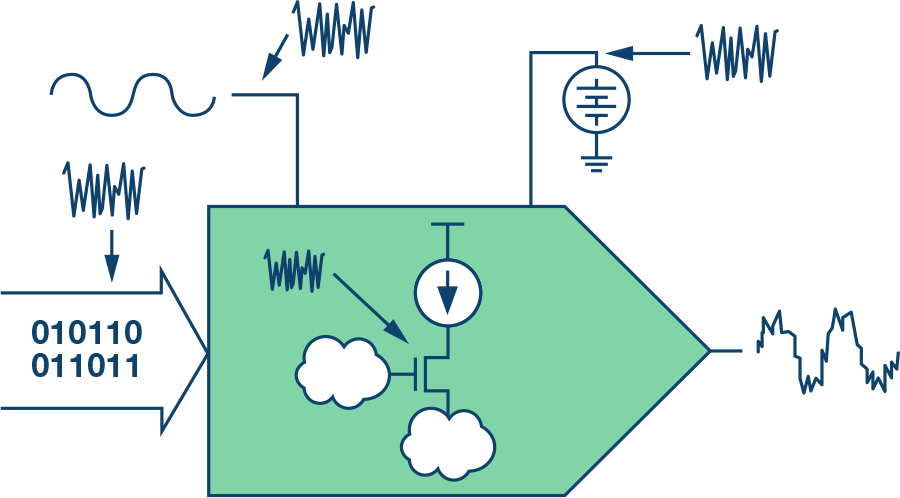

電源噪聲和時鐘抖動對高速DAC相位噪聲的影響

在所有器件特性中,噪聲可能是一個特別具有挑戰性、難以掌握的設計課題。這些挑戰常常導致一些道聽途說的設計規則,并且開發中要反復試錯。本文將解決相位噪聲

發表于 03-08 11:37

?10次下載

電源噪聲和時鐘抖動對高速DAC相位噪聲有什么樣的影響

在所有器件特性中,噪聲可能是一個特別具有挑戰性、難以掌握的設計課題。這些挑戰常常導致一些道聽途說的設計規則,并且開發中要反復試錯。本文將解決相位噪聲

發表于 11-19 15:35

?12次下載

如何通過一種系統化方法來量化電源噪聲電壓電平對相位噪聲的影響?

許多雷達系統要求低相位噪聲以最大限度抑制雜波。高性能雷達需要特別關注相位噪聲,導致在降低頻率合成器的相位

電源噪聲和時鐘抖動對高速DAC相位噪聲的影響的分析及管理

在所有器件特性中,噪聲可能是一個特別具有挑戰性、難以掌握的設計課題。這些挑戰常常導致一些道聽途說的設計規則,并且開發中要反復試錯。本文將解決相位噪聲

如何通過一種系統化方法來量化電源噪聲電壓電平對相位噪聲的影響

如何通過一種系統化方法來量化電源噪聲電壓電平對相位噪聲的影響

評論