晶振輸出波形可分為方波和正弦波;也可以分為單端輸出和差分輸出。

在選擇合適的波形時(shí),凱擎小妹建議您結(jié)合波形特點(diǎn)和應(yīng)用領(lǐng)域,權(quán)衡利弊后再選擇。

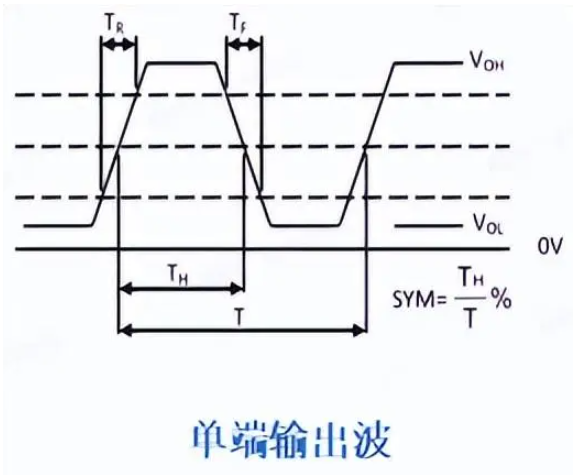

單端輸出

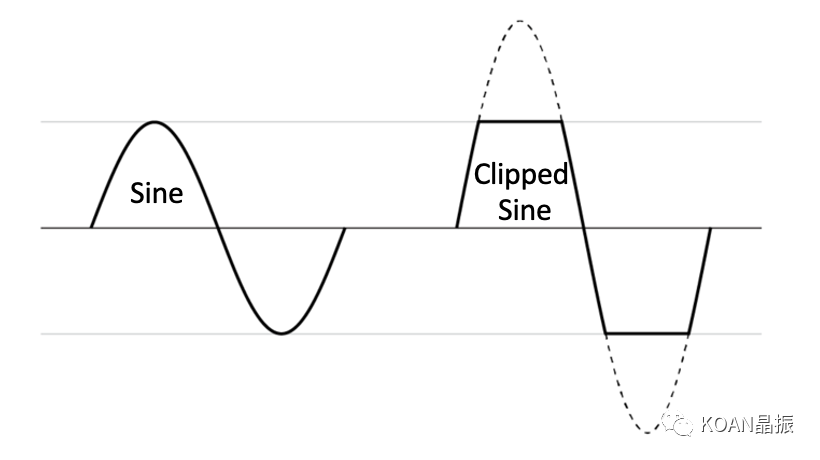

Sine/Clipped Sine

所有的無源晶振都是正弦波輸出,也是晶振的默認(rèn)輸出波形。正弦波僅包含一個(gè)基頻,不存在諧波,非常適合對(duì)低相噪有要求的應(yīng)用。

削峰正弦波是通過限制信號(hào)的輸出來防止到達(dá)最高點(diǎn)或最低點(diǎn)。

CMOS/HCMOS/LVCMOS

CMOS輸出適合于較短走線長(zhǎng)度和較低頻率的時(shí)鐘源(低于200MHz)。低阻值串聯(lián)電阻可以有效的減少反射并保持可靠的信號(hào)。另外有高速HCMOS和低壓LVCMOS滿足您的特定需求。

差分輸出

隨著科技的發(fā)展,我們傳輸?shù)臄?shù)據(jù)變大,傳輸?shù)木嚯x變長(zhǎng),對(duì)頻率穩(wěn)定度的要求變高。以下是差分輸出波形:

ECL/PECL/LVPECL

ECL主要作為TTL的替代波形而引入的。ECL電路可以滿足非常高速的數(shù)據(jù)傳輸需求。缺點(diǎn)是需要高功耗才可以運(yùn)行,并且ECL在使用中需要使用負(fù)電源。

PECL經(jīng)常用于高速領(lǐng)域內(nèi)的一個(gè)非常重要的邏輯電路,電路速度快,驅(qū)動(dòng)能力小,噪聲小,高頻。高功耗是PECL輸出的主要缺點(diǎn),且不同電平不能驅(qū)動(dòng)。如果使用低電壓3.3V/2.5V,則被稱為L(zhǎng)VPECL,即Low Voltage PECL。

LVDS

LVDS信號(hào)傳輸速度比CMOS快,但輸出功耗比LVPECL低,具有較小的電壓擺幅。通常用于高速數(shù)據(jù)傳輸?shù)膽?yīng)用,更高的數(shù)據(jù)速率。其噪聲低,傳輸距離遠(yuǎn)且準(zhǔn)確。

HCSL

相較于LVPECL, HCSL的優(yōu)勢(shì)為高阻抗輸出和快速切換時(shí)間。開關(guān)速度快,平均功耗介于LVDS和LVPECL之間,具有良好的相位噪聲性能。

審核編輯:劉清

-

CMOS

+關(guān)注

關(guān)注

58文章

5710瀏覽量

235420 -

正弦波

+關(guān)注

關(guān)注

11文章

642瀏覽量

55341 -

lvds

+關(guān)注

關(guān)注

2文章

1043瀏覽量

65793

原文標(biāo)題:?jiǎn)味溯敵龊筒罘州敵霾ㄐ?/p>

文章出處:【微信號(hào):koan-xtal,微信公眾號(hào):KOAN晶振】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

差分輸出與單端輸出的差別

有沒有合適的帶寬能達(dá)到20M,滿足差分輸入單端輸出的運(yùn)放呢?

TLV320AIC3101有單端輸出和差分輸出,單端輸出已經(jīng)用掉了,怎么利用差分輸出轉(zhuǎn)成單端輸出?

差分放大電路單端輸出相關(guān)問題

音頻差分轉(zhuǎn)單端輸出

應(yīng)用于電機(jī)驅(qū)動(dòng)的隔離運(yùn)放單端和差分輸出對(duì)采樣性能的影響

差分晶振的輸出波形解析

將差分輸出(隔離式)放大器連接到單端輸入ADC

如何選擇單端輸出和差分輸出波形呢?

如何選擇單端輸出和差分輸出波形呢?

評(píng)論