為了利用USB4?(或Thunderbolt? 4)的完整數據速率,通常在超高速數據線上使用重定時器或轉接驅動器設備。這對ESD保護方法有影響,這可能并不完全明顯。典型的USB3.2系統的走線長度可能超過100 mm。重定時器或轉接驅動器器件的放置將導致走線長度顯著縮短,從而對信號走線電感產生積極影響。根據經驗,10 mm走線長度大約相當于3-3.5 nH的電感。雖然從信號完整性的角度來看,降低走線電感肯定是可取的,但降低ESD保護和受保護系統之間的電感也會增加受保護系統看到的峰值電壓。

ESD失效機制和走線長度

受保護IC有兩種主要的ESD故障機制。一種是由流入IC的剩余電流引起的熱故障。在準靜態情況下,該電流取決于進入IC的路徑的導通電阻比與通過ESD保護的接地路徑的導通電阻比。

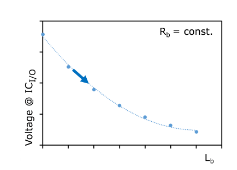

第二種ESD故障機制超過了受保護系統收發器中柵極氧化物上的最大電場強度。為了降低電場強度,應將受保護芯片看到的峰值鉗位電壓降至最低。這種動態效應不能通過準靜態考慮來捕捉。減小信號走線長度可減小電路板電感Lb在外部ESD保護和受保護芯片之間。對于其他不變的系統,這將增加危險的ESD峰值電壓。

確定峰值抑制性能

為了應對這種影響,Nexperia剛剛發布了首款采用最新TrEOS技術的產品,這些產品針對峰值電壓降低進行了優化。但是,如何發現哪種保護設備適合保護哪種系統呢?為支持設計工程師為其系統選擇合適的保護器件,Nexperia為其高速ESD器件提供了全動態系統高效ESD設計(SEED)仿真模型。與準靜態模型相反,全動態 SEED 模型還允許對峰值電壓抑制進行系統級仿真。

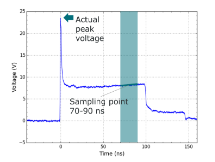

確定ESD保護器件的峰值抑制性能并不像人們想象的那么簡單。ESD槍設計用于測試完整系統的魯棒性,但缺乏顯示敏感收發器系統中峰值電壓的精度。即使在未更改的系統中的兩次測量之間,差異也可能很大。與ESD噴槍測量相比,傳輸線脈沖(TLP)測量可以顯示出顯著更高的再現性。但是,數據手冊通常僅顯示保護器件導通時采樣的標準TLP I(V)曲線。選擇100 ns脈沖長度來評估IEC61000-4-2 ESD脈沖的熱故障模式。

為了評估峰值電壓,需要進行非常快速的TLP(vfTLP)測量。這是對脈沖開始時發生的短過電壓的最準確測量,可以在第一個納秒內研究超過瞬態觸發效應。

重新定時器在運行

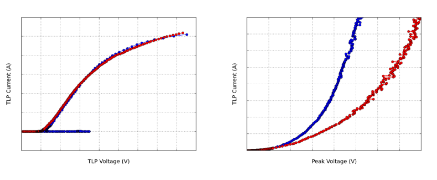

為了舉一個實際的例子,我們比較了兩個具有相當電容的ESD保護器件的鉗位。雖然兩個器件的標準TLP鉗位電壓相當,因此ESD脈沖的第二個峰值的能量抑制,但我們直觀地假設紅色器件比藍色器件具有更好的峰值電壓抑制。上升時間選擇為600 ps,以表示IEC61000-4-2脈沖的第一個快速峰值。

a) 100 ms TLP I(V) 測量和 b) 0.6 / 5 ns VFTLP I(V) 測量

在第一種情況下,盡管TLP觸發電壓更高VT1藍色曲線表示,同一器件在保護范圍內提供較低的vfTLP峰值電壓,從而導致IC上的峰值電壓較低。另一個好處是,藍色器件的反向關斷電壓更高 VRWM允許在 USB 類型 C? 環境中直接放置在連接器后面。這樣做的好處是在保護和IC之間增加了更多的電感,從而進一步降低了峰值電壓。在白皮書《為 USB4 選擇 ESD 保護器件》中,我們討論了 USB Type-C 可以將具有更高電壓規格限制的 USB3.2 系統連接到 USB4 系統。因此,USB4 的保護器件應該向后兼容 USB3.2 關于 VRWM當放置在連接器的正后方時。在此位置,它還為交流耦合電容提供保護。

提供實用的解決方案

在USB4環境中使用重定時器或轉接驅動器器件將縮短ESD保護和受保護IC之間的信號走線,從而降低電路板走線電感Lb.雖然較短的走線肯定有利于信號完整性,但在比較其他不變的系統時,其較低的電感會增加峰值ESD電壓。為了應對這種影響,Nexperia可以提供采用最新TrEOS技術的器件,這些器件針對峰值電壓抑制進行了優化。

審核編輯:郭婷

-

ESD

+關注

關注

48文章

2029瀏覽量

172929 -

驅動器

+關注

關注

52文章

8226瀏覽量

146253 -

定時器

+關注

關注

23文章

3246瀏覽量

114719

發布評論請先 登錄

相關推薦

基于FPGA的超高速FFT硬件實現

安捷倫科技宣布發布USB 3.0超高速物理層一致性測試解決方

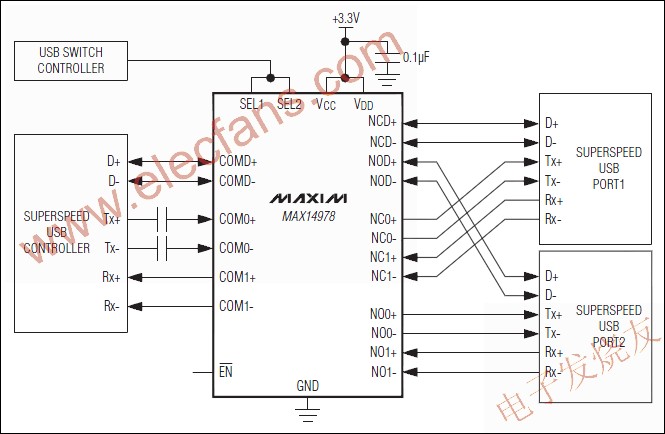

MAX14978 超高速USB模擬開關

安捷倫與NTS攜手推進超高速USB 3.0測試

Mouser帶來最新USB 3.0技術: 賽普拉斯FX3和恩智浦USB 3.0超高速轉接驅動器

超高速USB3.0主機和設備控制器接口應用方案

如何檢測復雜的超高速調制光信號?

TPDxEUSB30用于超高速USB 3.0接口的2、4通道ESD保護數據表

將USB4重新驅動到超高速

將USB4重新驅動到超高速

評論