COT控制模式系列:

- COT控制模式簡述part1

- COT控制模式簡述part2

- COT控制模式簡述part3

- COT控制模式簡述part4

- COT控制模式簡述part5

- COT控制模式簡述part6

在上一期中,有朋友問12V哪里來的? 在數據中心場合或者服務器等48V和12V的母線都是比較常見的。據我熟知的而言,48V仍然要轉換成12V的bus,作為母線電壓輸入。因此,這是一個比較常見的例子。

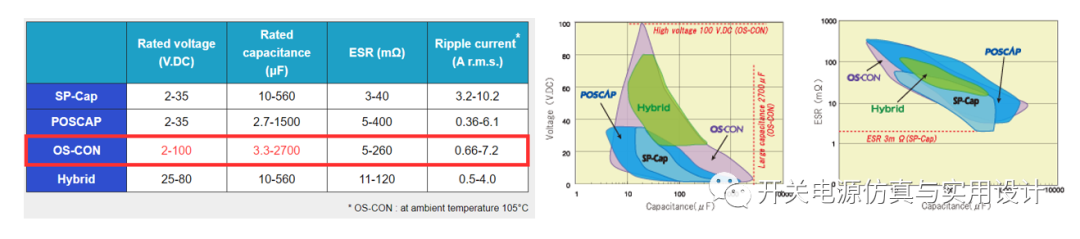

被我忽略的一點是,電容的RMS電流,流入電容的電流會引起電容溫升,有些電容制作商會給出RMS電流和溫升的關系曲線,更利于計算和選擇。比較推薦使用的是X6S或者X7R這種溫度范圍較寬的陶瓷電容。

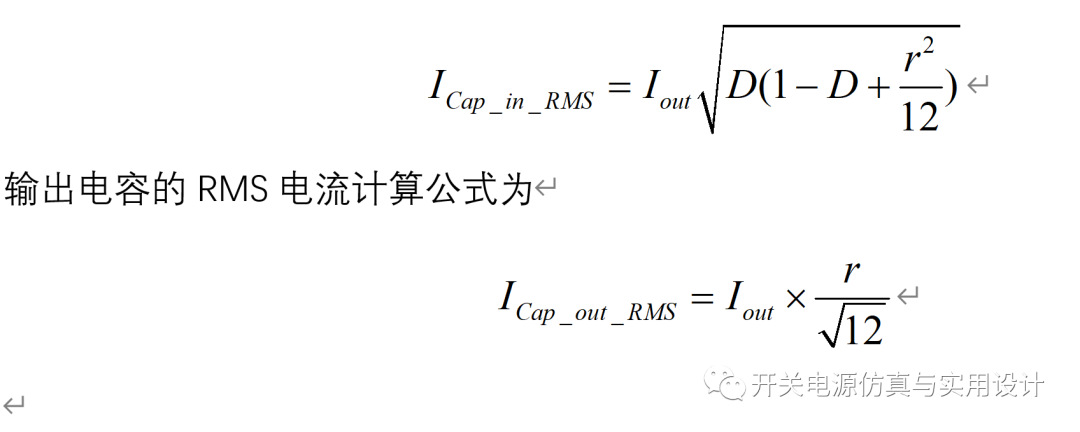

輸入電容的RMS電流計算公式為

暫時拋出兩個計算式以做補充。接下來,就可以搭一個簡單的SIMetrix/SIMPLIS仿真模型。根據之前幾期的介紹,首先需要搭建一個恒定導通定時器,當然,都是基于行為模型,精度僅夠學習觀摩使用,各位模擬設計的大佬,多多擔待。

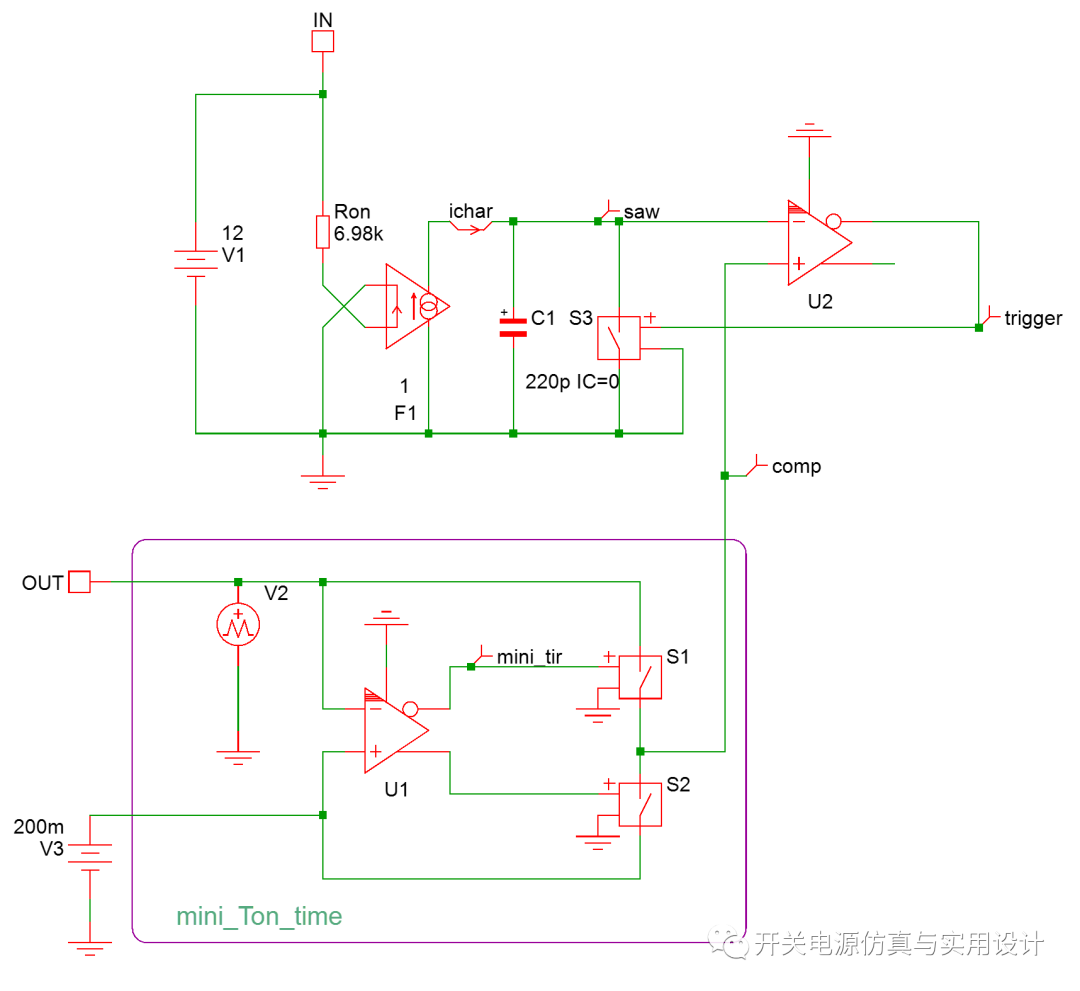

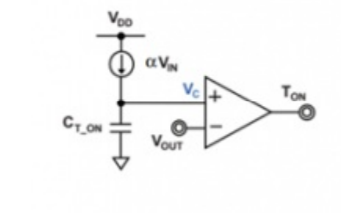

圖27 恒定導通時間定時器

首先,需要獲得與Vin成正比的電流源,可以使用壓控流源直接轉換成電容充電電流ichar,也可以使用如圖所示的流控流源,它將輸入電壓/Ron的電流轉換成電容充電電流ichar。后者這種情況更接近于實際底層的設計,因此姑且采用這種形式。ichar是一個與Vin成正比的可控恒流源,電容電壓將會線性上升,被送入比較器的負端。比較器的正端接了一個模擬啟動過程的電路,當系統剛啟動時,輸出電壓為0,此時將電容電壓vsaw無法與輸出電壓比較,比較器完全失去功效。在輸出電壓建立之前,使用一個200mV的內部基準做為比較器的正端輸入,這也對應著Ton的最小導通時間;當輸出電壓大于200mV時,再切換至輸出電壓做為比較器的正端輸入,就可以完成Ton與輸出電壓成正比的要求。

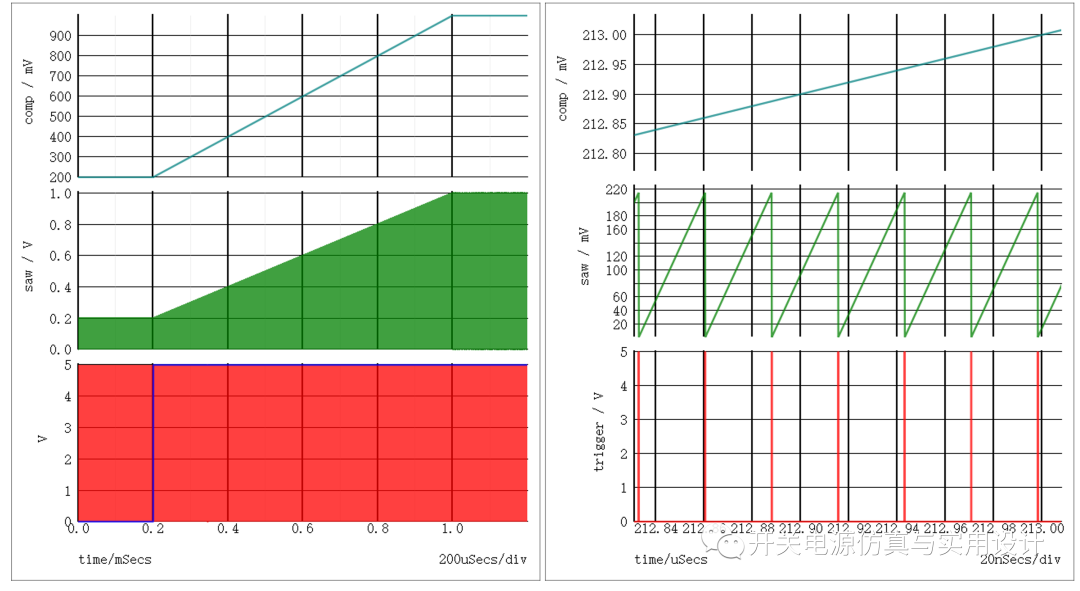

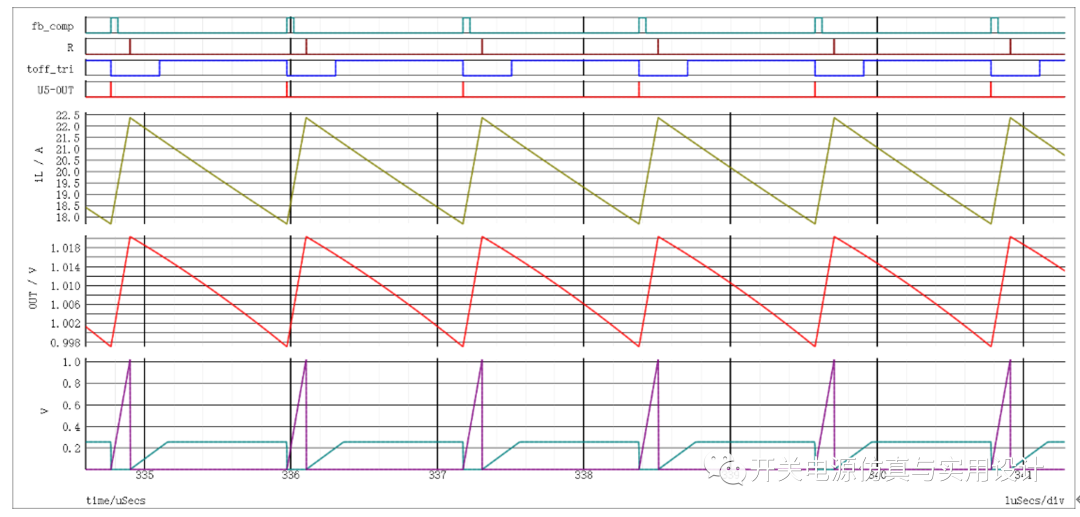

圖29 COT定時器的模擬波形

S3是一個理想的Switch,用來對電容電壓放電,從而形成鋸齒波的下降沿,它的觸發信號在COT控制模式中是由驅動脈沖結束的信號控制,此處僅作定時器的驗證,使用比較器的反向輸出信號做為觸發信號。電壓源V2設置成一個從0開始的ramp信號,升到1V時保持。用于模擬輸出電壓軟啟動的過程。

從仿真波形上看,完全和設想的一致,比較器的正端在先由200mV開始,達到比較器觸發點時,斜坡上升,最后保持在1V。相應的,Ton定時器的鋸齒波信號的幅值跟隨變化,由于比較器的斜率固定,Ton的時間一直會也會跟隨變化。

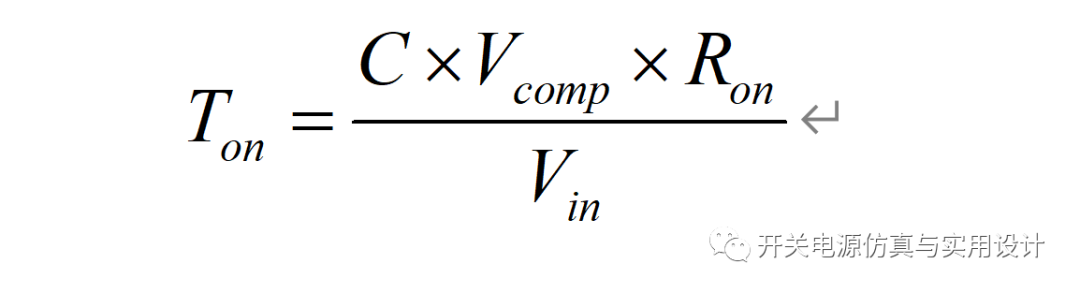

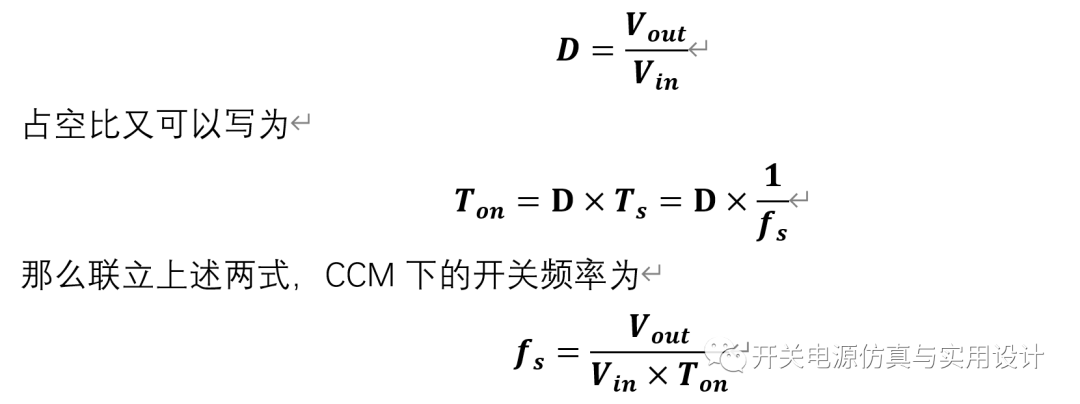

Ton時間可以計算為

調整電容C1和Ron就可以獲得需要的Ton值,按照圖的參數計算Ton=128ns,Ton_min=26ns。

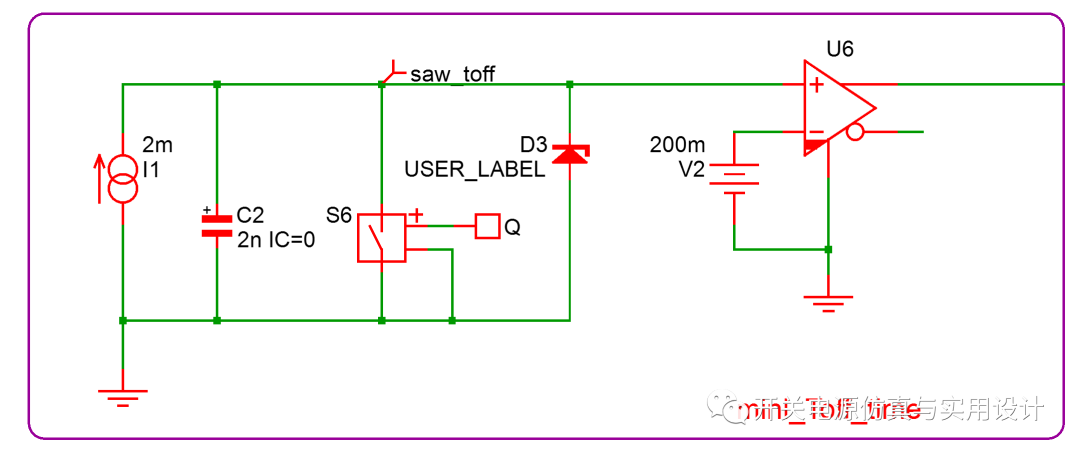

圖30 COTToff min定時器

同樣地,最小關斷時間的定時器可以如法炮制,此時可以使用一個簡單的恒流源給電容充電,需要注意的是,當Toff_min時間結束的時候,電容C2的正端電壓vsaw_toff會大于200mV,比較器輸出電平為高,而這個高信號需要一直保持住,直到下一個Ton的脈沖上升沿到來,才對電容進行放電,以釋放這個狀態。而電容電壓又不可一直充電,否則充電電壓會很高,所以使用一個鉗位穩壓管使得穩壓值略大于200mV即可。

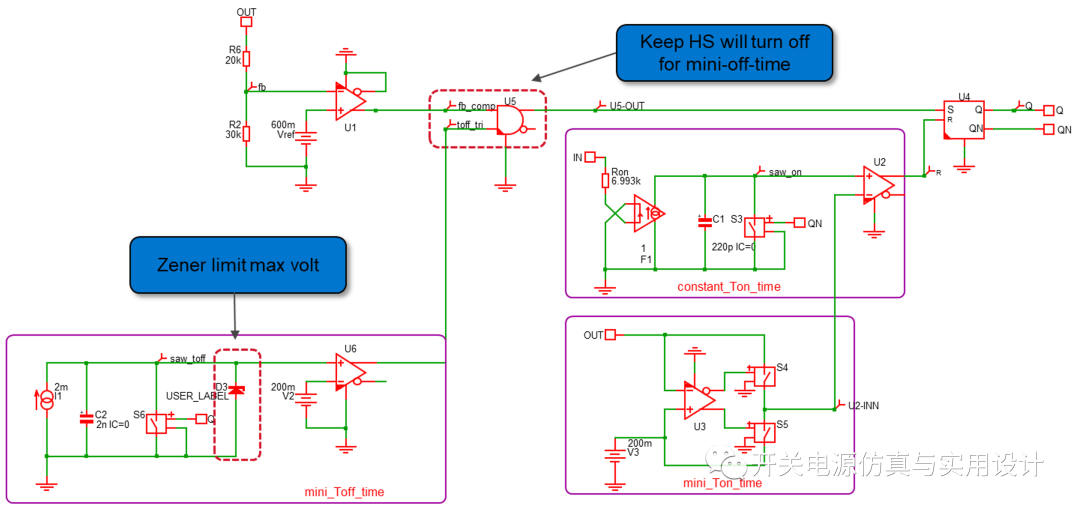

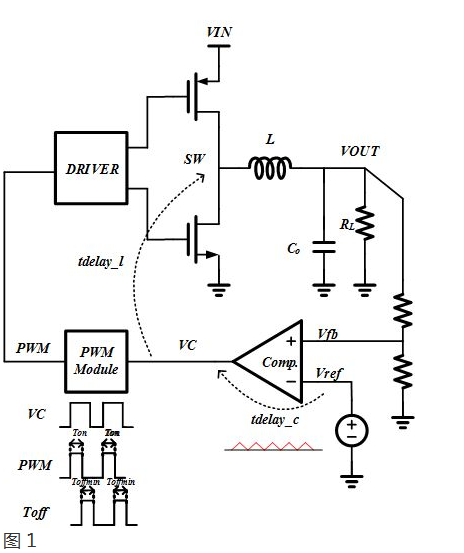

圖31 基本的COT控制模式的框圖

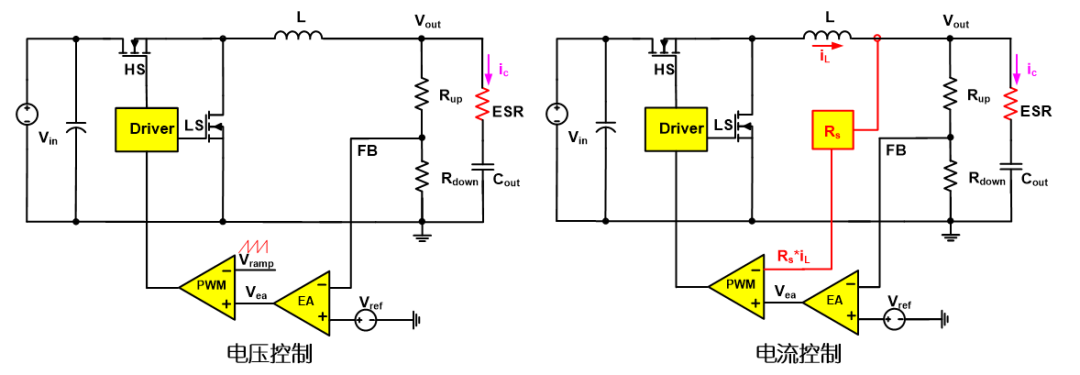

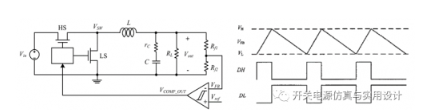

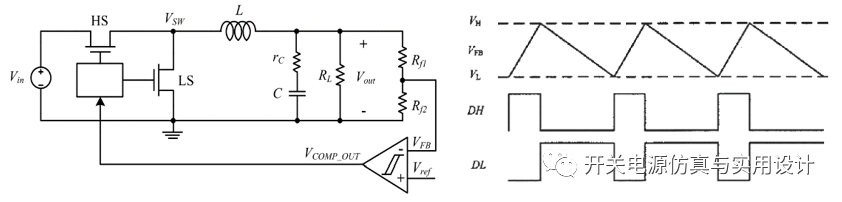

我們來說下它的具體的控制邏輯,設定的輸出電容的ESR較大于臨界值。

利用分壓電阻采樣輸出電壓,獲得反饋電壓vfb信號,與基準電壓600mV比較,當vfb低于600mV時,比較器U1輸出高電平,而此時的Toff_min定時器的輸出跟上述的那樣保持高電平的狀態。

那么與門U5的兩個輸入全為高電平,其輸出信號U5-OUT為高電平。這個信號輸入RS latch的S端,置位Q信號,Q此時拉高,若忽略死區時間,Q即作為上管的原始驅動信號,QN則為下管的原始驅動信號。此時上管開通,電感電流線性上升,對應的輸出電壓的ESR紋波也會線性上升,反饋電壓vfb的紋波電壓也在線性上升。

此時,Q拉高還會開通switchS6,將Toff_min定時器電容上的電壓放電,也即將Toff_min定時器的輸出拉低,也即是將U5-OUT信號拉低,這保證了RS latch的邏輯不會同時出現高的情況,其S上只會出現一個短暫脈沖。

圖32 COT控制模式基本邏輯和主要波形

此時,Q拉高,意味著QN拉低,QN拉低斷開了switch S3,此時Ton定時器就開始從0開始充電,當電容C1的電壓大于Vout(或者200mV的基準電壓),比較器U2的輸出發生翻轉拉高,此時RS latch的R端為高電平,S端為低電平,輸出信號Q拉低,結束Ton時間的驅動脈沖信號,QN則拉高,使得switch S3閉合,Ton定時器電容C1放電到0,比較器U2的輸出再次翻轉拉低。因此,也保證了RS latch的邏輯,其R上只會出現一個短暫脈沖。

當Q拉低時,同時關斷了switchS6,啟動了Toff_min定時器。Toff定時器電容C6電壓一直上升,超過200mV時,比較器U6會一直拉高,直到下一個開關周期來臨。

講到這里,基本的邏輯思路已經很清晰了。但是有一個疑問,怎么保證Toff_min的確可以在瞬態響應中完成了關斷上管Toff_min時間呢?當負載電流增加時,輸出電壓會產生undershoot,此時反饋電壓vfb會持續小于基準電壓600mV,可能會保持幾個周期。也就說,比較器U1的輸出會一直拉高,保持幾個周期。當系統開通第一個Ton時間后,Q信號啟動Toff_min定時器,當比較器U6拉高時,與門U5的兩個輸入信號全為高電平,又啟動了下一個Ton時間。因而,可以證明,在vfb一直小于基準電壓時,上管的確可以完成Toff_min時間的關斷。

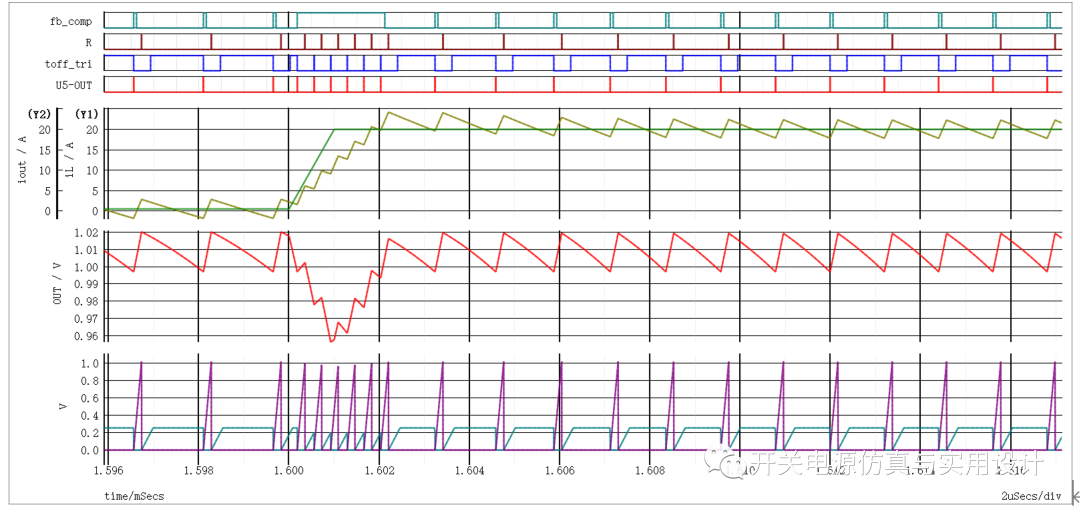

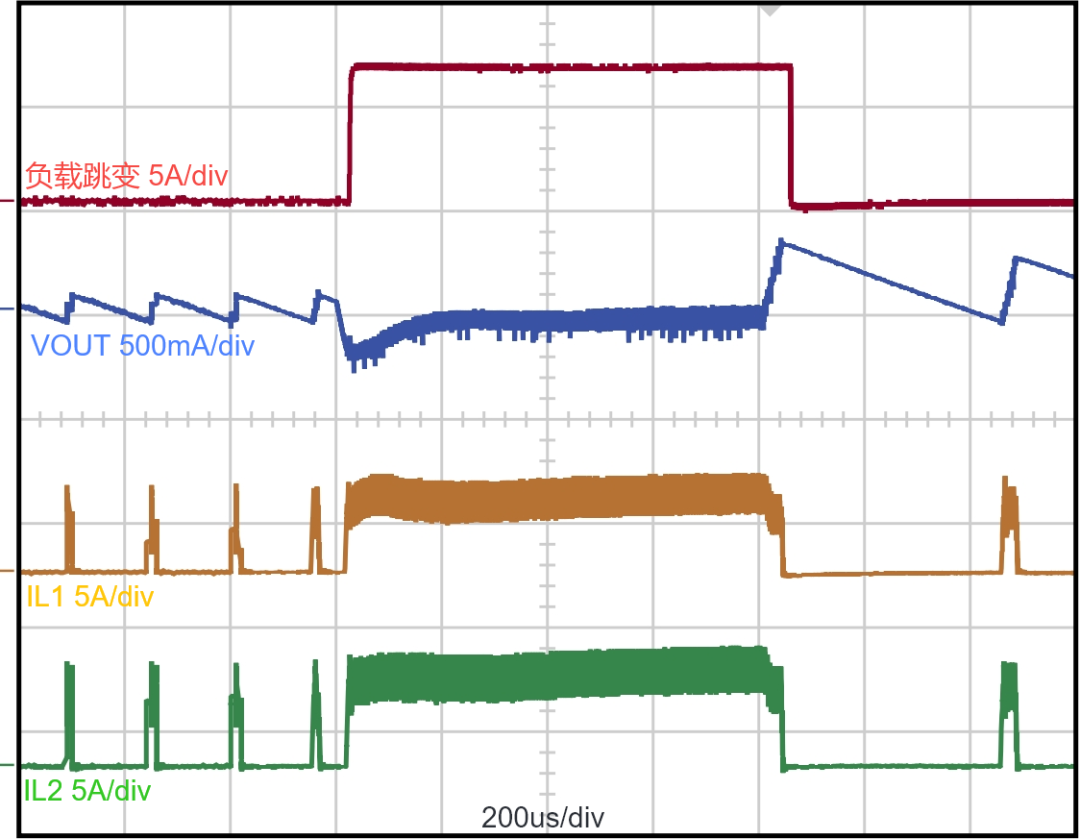

圖33 undershoot瞬態下Toff_min的驗證

根據上述的邏輯,跑一次undershoot的瞬態,可以看出底部淺綠色Toff_min的波形,在動態時刻僅以三角波形式出現,而在其他時刻以梯形波出現。因此的確,如上述邏輯所述那樣。

順便提一點,仿真模型僅僅是為了提高一個更直觀的理解,加深對系統思想的理解,也作為個人邏輯思想的驗證工具,千萬不要為了仿真而仿真。如果你想獲得和實際中一毛一樣的仿真模型,那需要深入到更底層的半導體物理和CMOS模擬電路設計領域,還要考慮雜散參數等問題。這對于Simplis工具來說是不適用的,也偏離了建立Simplis模型的初衷。

這種仿真模型對模擬IC設計者而言,就像一個已經不適合成年人玩耍的兒童玩具,顯得有些拙劣。如果能為系統設計者或者電源應用設計者提供一些微小的幫助,筆者已經頗感欣慰了。

-

電容

+關注

關注

100文章

6038瀏覽量

150277 -

陶瓷電容

+關注

關注

3文章

435瀏覽量

23912 -

RMS

+關注

關注

2文章

138瀏覽量

35791

發布評論請先 登錄

相關推薦

開關電源變換器工作模式--COT固定開通時間模式

[轉帖]開關電源變換器工作模式–COT固定開通時間模式

淺談COT控制BuckBuck為什么是天然穩定的?穩定條件是什么?

COT控制模式的詳細資料說明

COT控制模式簡述-2

COT控制模式簡述-7

COT控制模式簡述-7

評論