本次操作包括:工程的版本遷移,板級測試時信號的抓取。

如何使用新版本的vivado去打開舊版本的vivado工程

如何使用新版本的vivado去打開舊版本的vivado工程。

對于舊版本的vivado工程或者是ise工程,更新到新版本的vivado環境下有兩種方法:

1、直接用新版本vivado打開原有工程文件,進行IP核更新; 2、拷貝原有工程設計文件、約束文件、IP核文件夾至新建新版本vivado空白工程文件下,進行更新。

1、在舊版本vivado基礎上直接升級

我們先來介紹一下如何直接使用新版本打開舊版本工程并且進行升級。

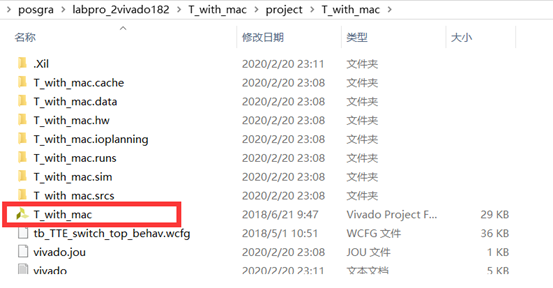

直接使用新版本vivado打開vivado的工程文件。

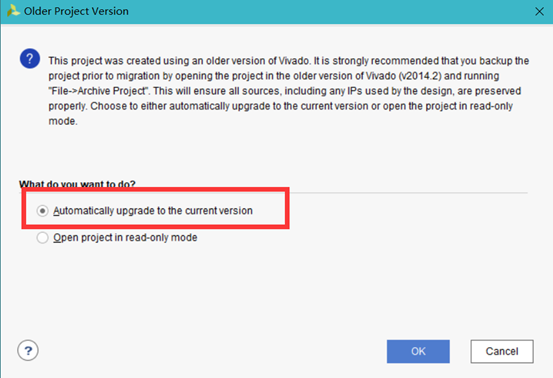

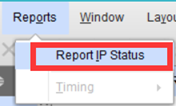

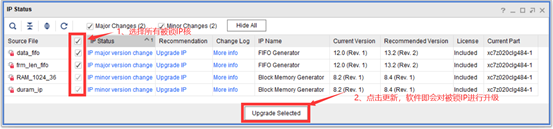

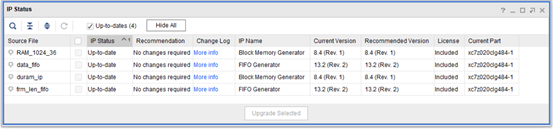

對于新版本vivado一般在打開舊版本工程時都會自動進行更新默認自動更新就好。 打開工程之后,需要對舊版本工程的IP核進行升級操作。點擊Reports->Report IP Status查看IP核被鎖狀態進行升級。

選中所有IP核進行升級。

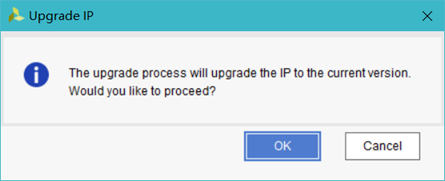

點擊確定。

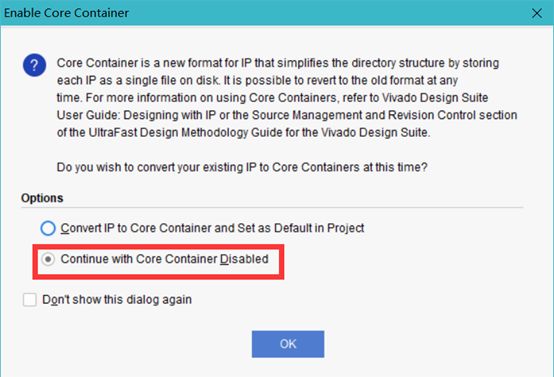

保持默認不使用核容器,(Core Container沒有用過,我都是默認不使用)。

升級完成之后的界面如圖所示。

如何使用新版本的vivado去打開舊版本的vivado工程

debug步驟:

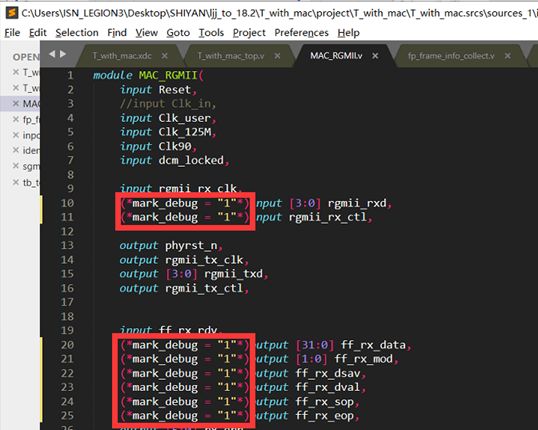

在需要debug的輸入輸出端口列表前加 (* mark_debug = “true” *)。

在編譯通過后,進行綜合生成網表等文件,點setup debug進行添加。

保存,xdc中應該有約束了,原理圖里也有ila_core 模塊,直接進行實現即布局布線。

在線調試:生成比特后下載,run trigger。

注意:在有多個debug端口時,會引入1個以上ila_core,每一個ila_core 的時鐘域都是獨立的,且在每一個ila_core中各個端口的時鐘域是一樣的。

1、設置信號抓取標記

將需要測試的端口前標記上(*mark_debug = “1”*)或者(*mark_debug = “true”*)

注意:這里最好將需要測試的端口信號打一拍再進行測試,因為輸入輸出端口的驅動單元類型往往是不一樣的,比如兩個紅框之間的rgmii_txd信號它的驅動單元類型就是ODDR,這將影響布線到此處的邏輯分析儀ila的探針的連接,具體的我也不清楚應該是驅動能力不匹配之類的,反正最好實現的時候會報錯。如果不打拍則在后續設置setup debug的時候就要注意去除不符合驅動類型的信號。

2、建立debug文件

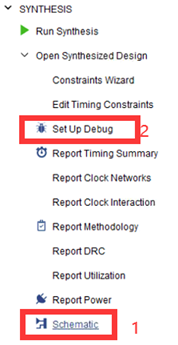

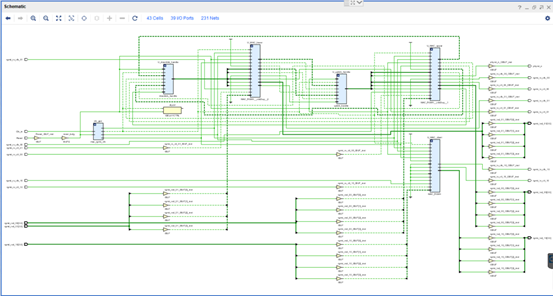

添加完debug標記后,進行編譯、綜合,沒有問題則可以查看當前原理圖(其實也可以不用看,這里只是為了對比ila模塊)然后點擊Set Up Debug對剛剛添加的信號進行設置。

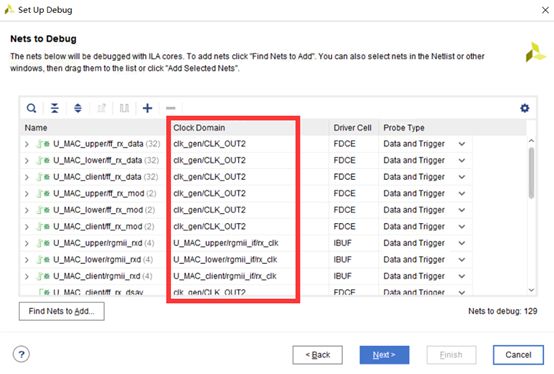

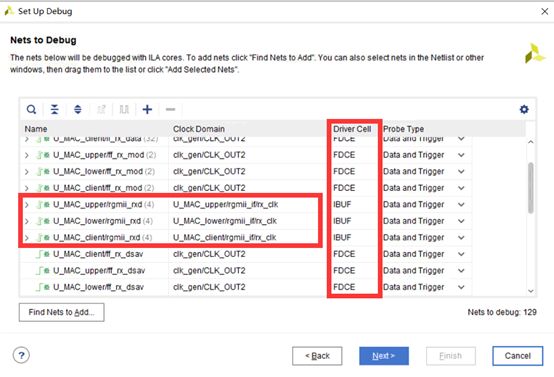

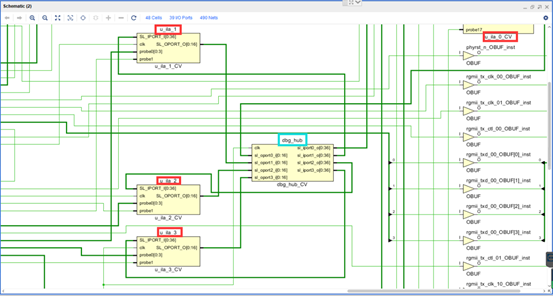

設置的信號有幾個需要注意的地方:

1、關于時鐘域的選擇,如圖紅框部分,這些時鐘需要選擇free clock,所謂free clock(按照我自己的理解,也可能不準確)就是系統一上電就能運行的時鐘,并且不會因為復位以外的條件停振,比如有些時鐘為了節省功耗,僅在需要進行數據交換時振動,在其他時刻保持低電平,但是這種時鐘就不是free clock。

2、注意選擇具有符合標準驅動單元的信號,這里右側紅框中都是可以的,但是對于DDR型的驅動信號就會出錯。

3、同一個時鐘域的信號都在同一個ila模塊下,即有幾個時鐘域就會有幾個ila模塊。

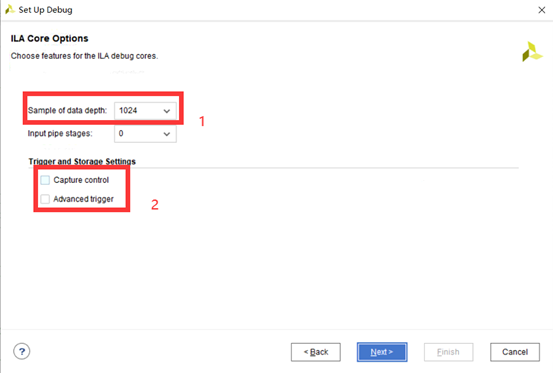

這里需要注意:

1、是選擇采樣深度,會占用一定的FPGA資源,所以如果設計系統簡單就可以選擇多一點,可以看到較長時鐘周期內存儲的信號變化。

2、選擇上后,可以進行高級設置操作(選了也沒用上==)。

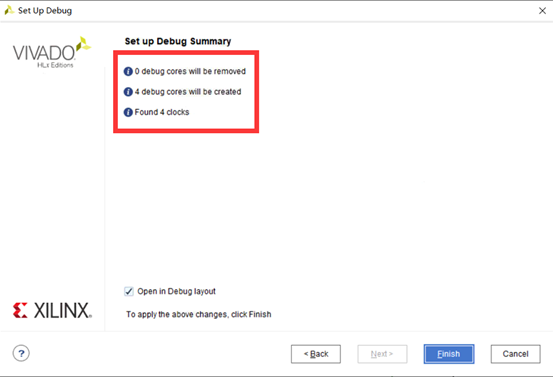

可以看到這里的summary是4個時鐘域和之前選擇一致。

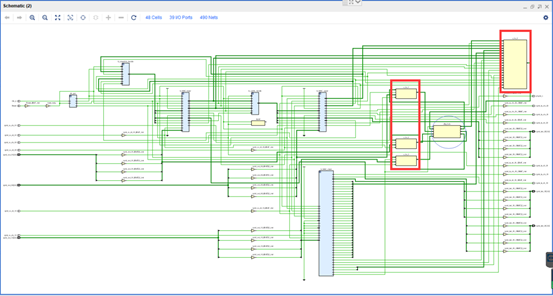

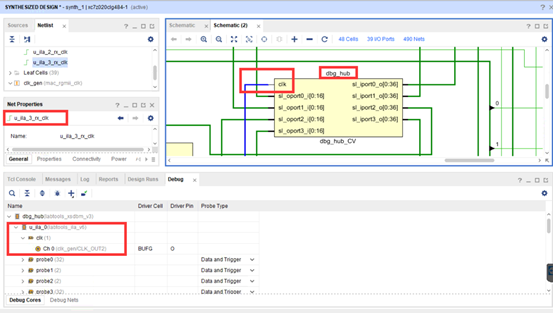

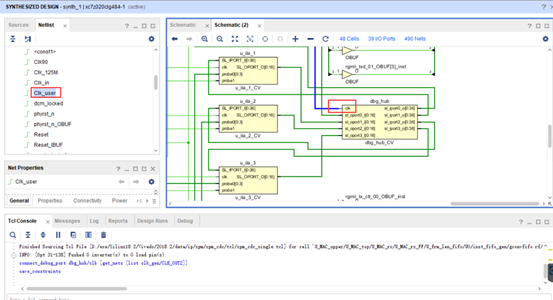

這是兩張原理圖,后者的紅框框部分是添加的4個ila模塊,中間藍色圓框部分是debug hub,即連接FPGA和jtag的部分。

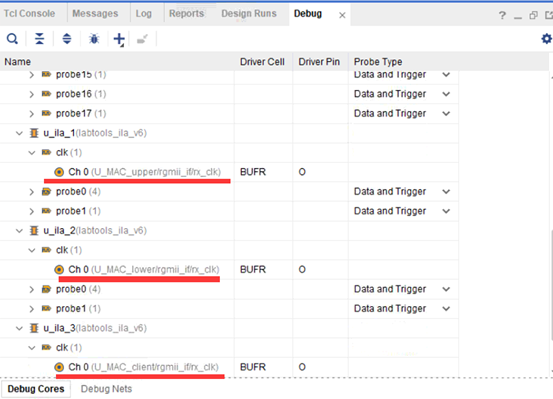

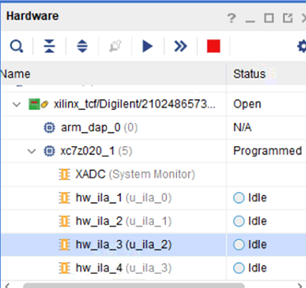

在底部Debug窗口可以看到各個ila模塊的時鐘選擇。

對于debug hub時鐘域的選擇查看可以通過tcl命令也可以點擊原理圖連線的方式,在左側會有連接顯示,這里看到是連接到了ila3模塊上,這樣不太好,因為如果ila3的時鐘沒選擇對就會導致整個debug hub在后面下載比特時無法被檢測到,就算其他ila的時鐘對了也白瞎。因為計算機是通過jtag返回數據的,而jtag又靠著debug hub 連接fpga的ila。

3、完善XDC文件,實現電路

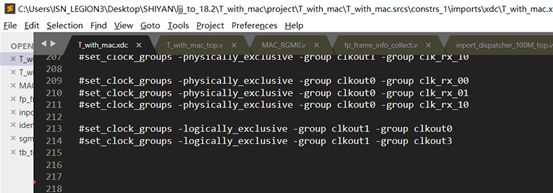

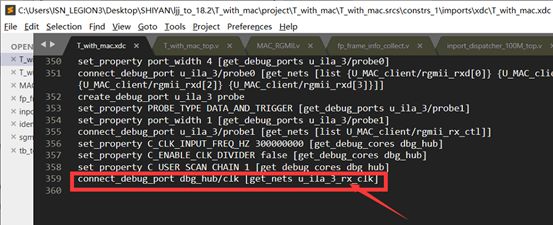

修改完成之后,依然需要保存修改,看到這里沒有保存約束文件在214行。

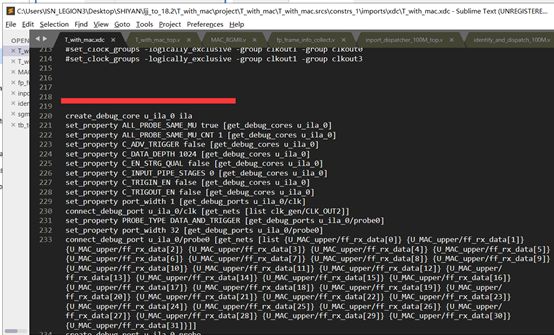

保存之后xdc增加了ila模塊的對應約束。

這里對應debug hub 的連接時鐘。

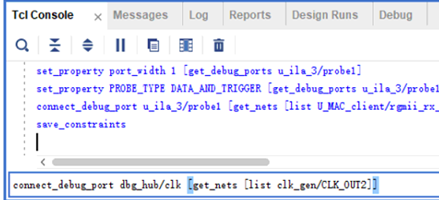

之前說了debug hub時鐘保持默認的缺點,這里通過tcl命令進行修改,通過查看ug908文檔可以知道推薦的debug hub時鐘在100Mhz左右,且至少在JTAG下載速率的2.5倍以上,采樣定理嘛,一般jtag速率默認15Mhz,查看代碼中時鐘生成部分,發現CLK_OUT2也就是mac的用戶側時鐘就是100Mhz,所以我們選擇debug hub時鐘為100Mhz。

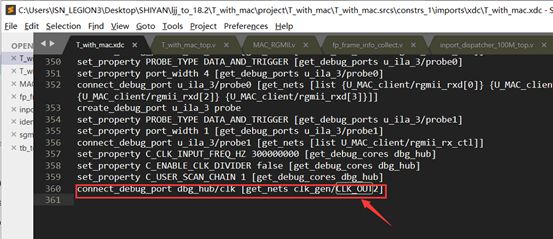

修改完成后,查看xdc確認已經修改了(其實也可以直接通過xdc

修改,但是直接修改xdc軟件可能會提示綜合過期,讓重新綜合,而通過tcl則可以直接進行后面的步驟)。

我們再次查看原理圖,可以看到debug hub的時鐘域已經修改。

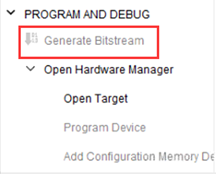

4、生成比特流文件,進行板級調試并抓取信號

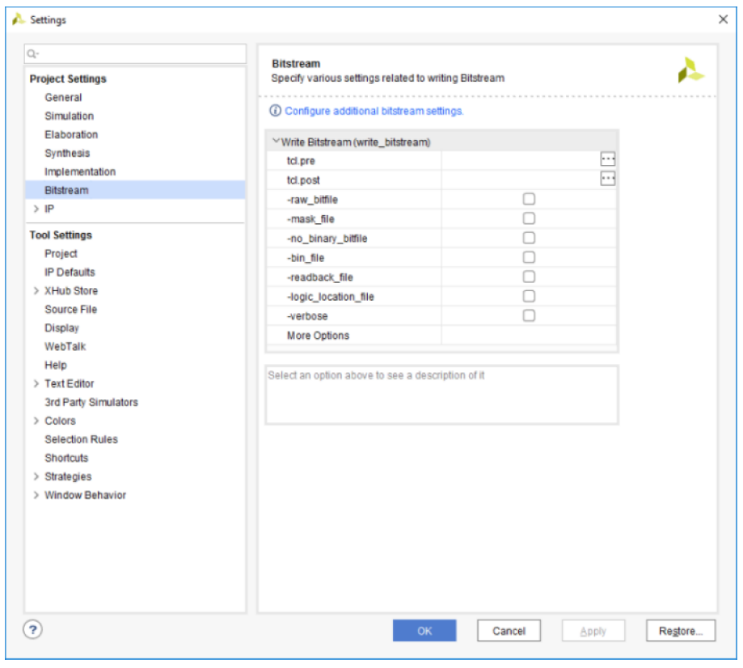

直接生成比特文件。

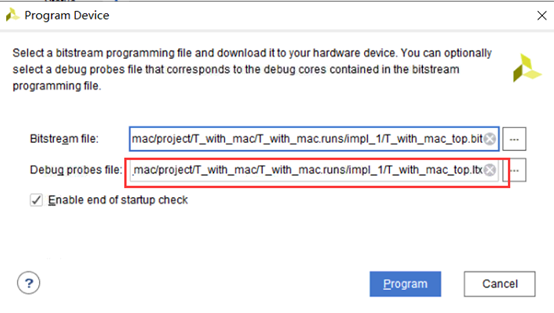

相比較之前的工程版本遷移時的下載界面,紅框部分多出了后綴為ltx的文件,即邏輯分析儀的探針文件。

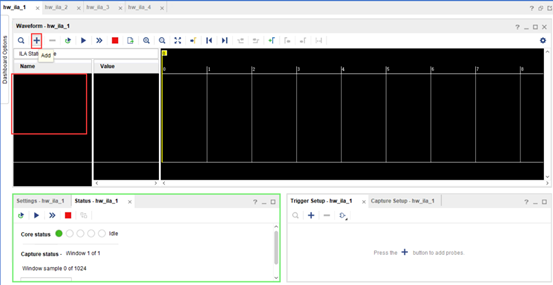

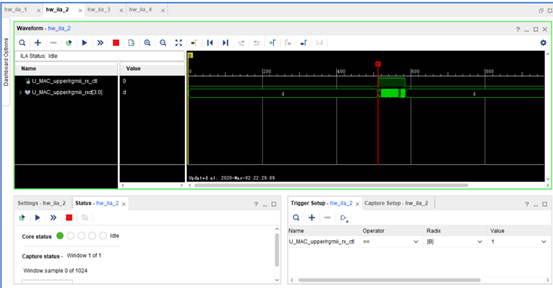

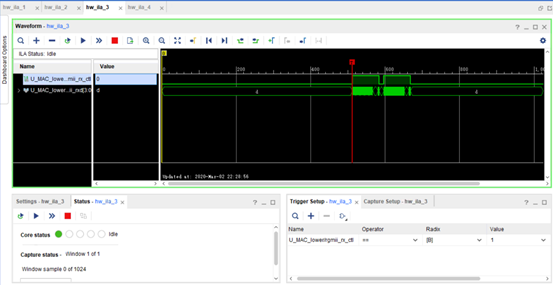

下載完成后會彈出4個dashboard對應著4個不同時鐘域的ila模塊,可是沒有信號,這時可以點擊+號進行添加。

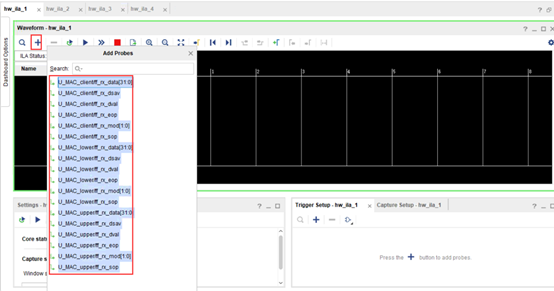

ctrl+a選中所有進行添加。

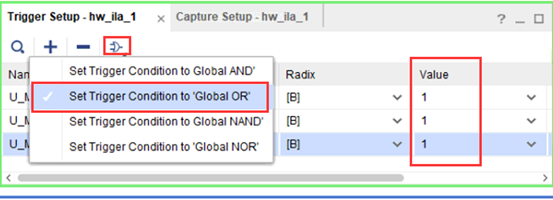

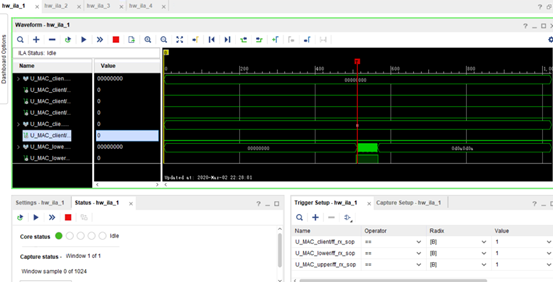

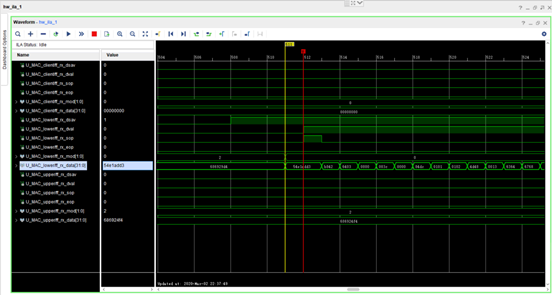

添加完信號后注意右下角的觸發條件設置,同樣點擊+號設置需要添加的信號,這里選則的是幀起始標志sop,并且選擇觸發條件的關系為或,同時觸發值設置為1’b1,之后再點擊三角型的 run trigger符號即可。

這里lower部分已經有波形了。

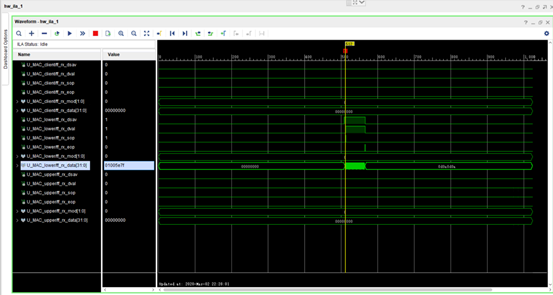

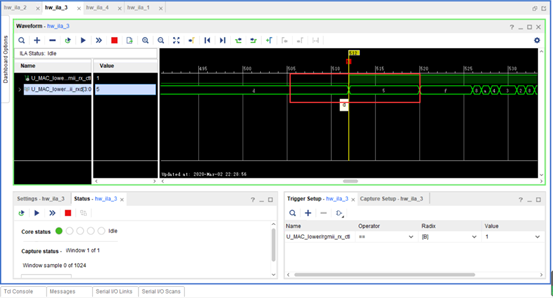

放大看所有的信號。

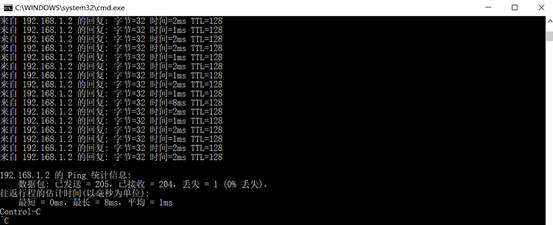

這里發現沒有前導碼是因為這里的4字節數據已經是進了mac之后經過了8轉32的數據了已經去掉了前導碼和CRC。但是upper client沒有數據,原來是沒有ping都沒有發怎么有?

結果發現ping了也沒有,好氣。

注意之前設置的觸發條件,是或關系,于是lower的sop信號在當前的1024個鐘內比其他的sop先觸發,而各個sop的間隔周期大于我們設置的采樣深度1024,所以無法同時顯示,刪除lower觸發條件后就有了,當然lower又沒有了。

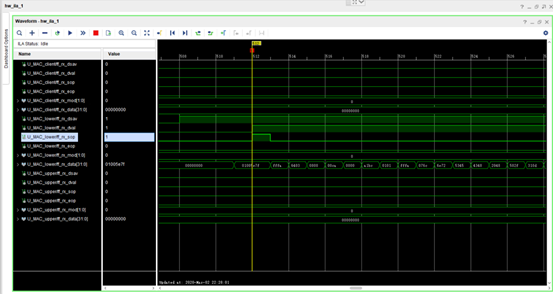

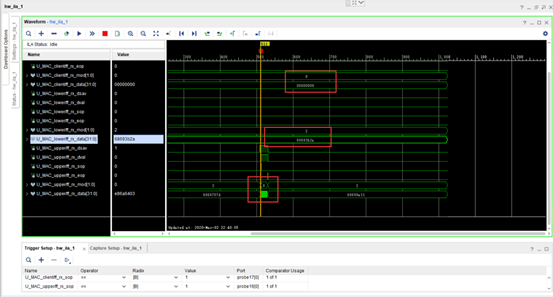

這邊按照同樣的步驟,添加觀察信號、添加設置觸發條件、點擊run trigger,就能看到波形了,注意放大后的紅框部分,有了前導碼,按單字節應該是 55 55 55 d5的順序而這里由于是rgmii只是半字節,所以是 5 5 5 5 5 5 5 d。

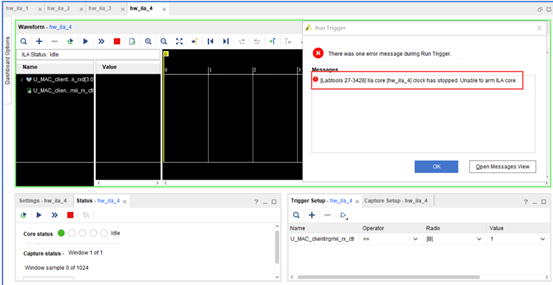

對ila3按同樣的步驟操作當我們點擊run trigger的時候會發現出現unable to arm ila core的錯誤,這就是時鐘域的問題,由于我們選擇的是rgmii_rx_clk這是由phy提供的,但是ila3即例化時的client對應的phy沒有插網線,所以也沒有時鐘,自然無法arm ila core。

這里特意為了對比不同時鐘域的選擇對于ila的影響,其實也可以將lower upper client的ila時鐘域都設置成用戶側即CLK_OUT2因為這個時鐘一直存在,這樣即使ila3對應的模塊的網口沒有插網線,在dashboard上顯示也會有全0 的數據,就和ila0 一樣,可以翻到前面去看看,這里的lower upper client的ff_rx_data[31: 0]來自三個獨立的例化模塊,但是也可以放到同一個時鐘域。表達的不太好實踐一下就能知道了。

審核編輯:湯梓紅

-

信號

+關注

關注

11文章

2790瀏覽量

76734 -

調試

+關注

關注

7文章

578瀏覽量

33924 -

文件

+關注

關注

1文章

565瀏覽量

24732 -

端口

+關注

關注

4文章

964瀏覽量

32058 -

Vivado

+關注

關注

19文章

812瀏覽量

66478

原文標題:Vivado工程升級及板級信號調試

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

vivado ILA在線調試求助

vivado在線調試

玩轉Zynq連載5——基于Vivado的在線板級調試概述

玩轉Zynq連載33——基于Vivado的在線邏輯分析儀板級調試

玩轉Zynq連載36——[ex55] 基于VIO在線板級調試的AXI GP總線讀寫實例

Vivado中綜合,實現,編程和調試工程可能會出現的問題及解決方案

Vivado中使用debug工具步驟與調試技巧

使用Vivado 2016.3中IBERT調試的好處及步驟

如何使用Vivado Logic Analyzer與邏輯調試IP進行交互

如何使用Vivado在設備啟動時進行調試

如何升級Vivado工程腳本

ISE工程升級到Vivado及板級信號調試

Vivado Design Suite用戶指南:編程和調試

Vivado Design Suite 用戶指南:編程和調試

Vivado工程升級及板級信號調試方案

Vivado工程升級及板級信號調試方案

評論