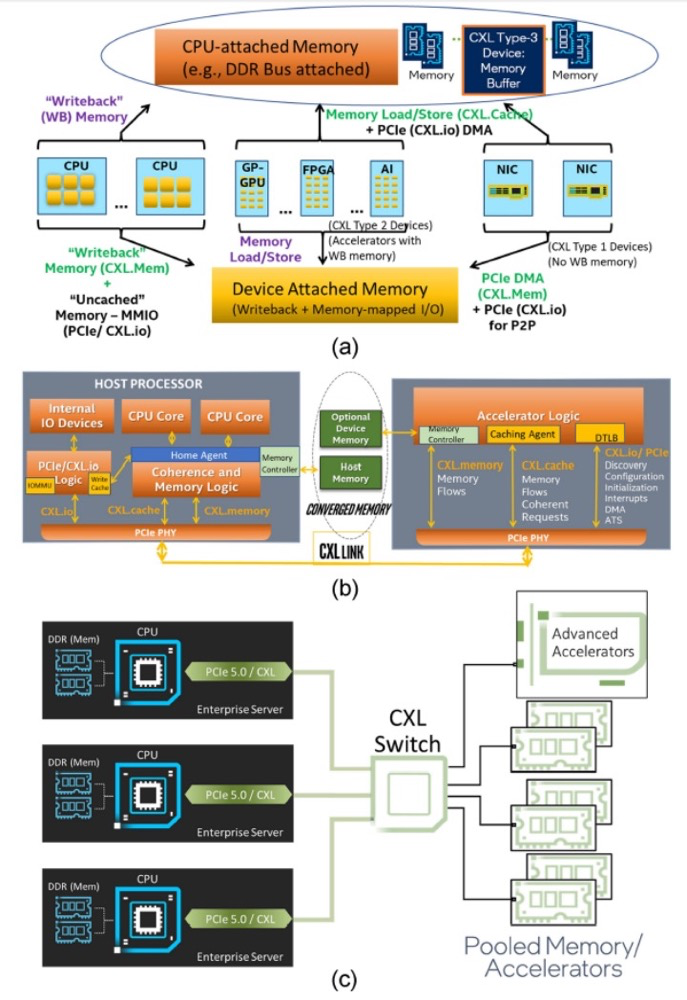

在《大內存時代,振奮人心的CXL技術(上)》中,我們對CXL技術是什么,解決了什么問題,以及CXL1.0/1.1、CXL2.0和CXL3.0技術進行了詳細闡述,并從存儲變革了解了CXL的未來意義。

CXL技術的出現帶來了一個全新的市場,本文將繼續對業界各大廠在CXL上的布局以及CXL技術依舊存在著較高延遲性進行闡述,希望有助于大家更進一步了解CXL現狀。

本文要點

CXL作為一項嶄新的技術,各大廠家都在搶先布局,目前大陸選手在CXL領域并未落后,部分廠家甚至表現出彩。

目前,CXL的內存延遲在170-250ns左右,與其他CPU的內存、緩存和寄存器仍然存在一定差距。隨著時間的推移,業界預計延遲問題會大大改善。

01

新技術搶先入,大廠布局如何?

CXL發展勢頭強勁,三星、SK海力士、Marvell、Rambus、三星、AMD等大廠們的布局也在不斷加速。

Microchip推出用于數據中心計算的新型CXL智能存儲控制器

2022年8月,Microchip宣布擴大旗下串行連接存儲控制器產品陣容,推出基于Compute Express Link(CXL)的新型SMC 2000系列智能存儲控制器,使CPU、GPU和SoC能夠利用CXL接口連接DDR4或DDR5存儲器。

據悉,該解決方案可為每個內核提供更大的存儲帶寬和更高的存儲容量,并使現代CPU能夠優化應用工作負載,從而降低數據中心的整體總擁有成本。

SK海力士:到2023年量產CXL內存產品

2022年10月,SK海力士成功開發行業首款將計算功能與CXL存儲器相結合的CMS(Computational Memory Solution)。據悉,該解決方案擬搭載于下一代服務器平臺上,有望提升系統性能和能源效率。

2022年11月,SK海力士宣布已經與AMD展開了密切的合作,為EPYC 9004系列服務器處理器提供了完全兼容的DDR5和CXL解決方案,并得到了AMD的驗證。此外,SK海力士還與AMD在第四代EPYC服務器處理器參考架構上測試PCIe 5.0連接的穩定性,以便未來提供高性能的PCIe 5.0NVMe解決方案,以響應當今AI和ML應用市場的需求。

在更早的8月,SK海力士推出首款CXL存儲器樣品。SK海力士DRAM產品規劃負責人Kang Uk-song在一份聲明中表示,SK海力士的目標是到2023年量產CXL內存產品。

美滿電子(Marvell)收購CXL開發商Tanzanite

美滿電子正在進行以數據中心為重點的投資來擴大潛在市場。2022年5月9日,美滿電子宣布將收購先進CXL技術領先開發商Tanzanite,加速實現完全可組合的云基礎架構的愿景。

Marvell存儲業務事業部執行副總裁Dan Christman表示:“我們相信CXL將成為實現下一代數據中心最佳資源利用的重大變革者,而收購Tanzanite將提高我們解決客戶最具挑戰性問題的能力。”

據了解,未來的云數據中心將建立在利用CXL技術的完全分解式架構上,基于連接處理器、加速器和內存的行業標準CXL的硅組件將促進具有顯著性能和效率優勢的新云數據中心架構。

Rambus開展CXL內存互連計劃

2021年6月,Rambus推出了CXL內存互連計劃,并宣布與包括云、系統和內存企業在內的生態體系達成合作,以加快CXL內存互連解決方案的開發和落地。當年10月,Rambus發布了CXL 2.0控制器。

除了新產品動態之外,Rambus在并購方面也有新進展。2021年6月,Rambus宣布完成對AnalogX和PLDA的收購,增強了公司在服務器內存接口芯片方面的領先地位,加速了為下一代數據中心提供創新CXL互連解決方案的路線圖。

2022年5月5日,Rambus宣布收購電子設計公司Hardent。據了解,Hardent擁有20年的半導體經驗,其世界一流的硅設計、驗證、壓縮和糾錯碼(ECC)專業知識為RambusCXL內存互連計劃提供了關鍵資源。

瀾起科技新品不斷

2022年5月6日,瀾起科技發布全球首款CXL內存擴展控制器芯片(MXC)。

官方資料顯示,這款MXC芯片是一款CXL DRAM內存控制器,屬于CXL協議所定義的第三種設備類型,按照CXL 2.0規范設計,支持PCIe 5.0規范速度,專為內存AIC擴展卡、背板及EDSFF內存模組而設計,可大幅擴展內存容量和帶寬,滿足高性能計算、人工智能等數據密集型應用日益增長的需求。

今年1月初,瀾起科技宣布,其PCIe 5.0/CXL 2.0 Retimer芯片成功實現量產。據悉,該芯片是瀾起科技現有PCIe 4.0 Retimer產品的升級,可為業界提供穩定可靠的高帶寬、低延遲PCIe 5.0/ CXL 2.0互連解決方案。

三星推出512GB CXL內存擴展器2.0

今年1月5日,在美國國際消費類電子產品展覽會(CES2023)上,三星電子展示了其512GB CXL內存擴展器。官方資料顯示,這款設備支持最新的CXL2.0接口,采用EDSFF(E3.S)封裝尺寸,配備專用集成電路(ASIC)CXL控制器,并采用當下主流的DDR5 DRAM作為存儲核心,從而實現極高的I/O接口帶寬。

三星512GB CXL內存擴展器擁有極佳的通用性和靈活的可擴展性,創新性地支持將服務器的存儲容量擴展到數TB以上,滿足大數據和AI/ML工作負載的處理需求,尤其適合下一代大容量企業級服務器和數據中心應用。值得一提的是,三星這次推出的這款內存模組CXL內存擴展控制器芯片正是由上述提到的瀾起科技提供。

AMD預計將于2023年推出支持CXL1.1接口的新品

AMD的EPYC Genoa支持DDR5、PCIe 5.0以及CXL1.1接口。并且,其另一產品Bergamo擁有更高的電源效率和每插槽性能,它將會和Genoa采用相同的CPU接口,所以PCIe5.0和DDR5以及CXL1.1都是支持的,預計將會在2023年推出。

總體而言,CXL技術入市不久,目前各大廠家發展進度差別并不大,大家都站在同一起跑線上競爭。大陸廠商如瀾起科技近期動態頻頻,成果也是獲得了業界的認可。未來,依舊可以在這個市場上繼續發力。

02

CXL依舊面臨著延遲問題

內存離CPU越遠,延遲就越高,這就是內存DIMM通常盡可能靠近插槽的原因。最大限度的降低延遲是業界一直致力于解決的問題,因此,大家對于這項嶄新的CXL技術也是抱有較高期待。

由于與CPU的距離較遠,業界對于PCI-Express以及CXL的延遲性會寬容一些,而對于SRAM、DRAM等則十分嚴格。按照上文所述,SRAM響應時間通常在納秒級,DRAM則一般為100納秒量級,NAND Flash則高達100微秒級。

作為一個分布式內存,盡管CXL主打的是低延遲,但其與CPU的內存、緩存和寄存器比起來,延遲仍然有著一定差距的。在此前的Hot Chips上,CXL聯盟就給出了CXL在延遲上的具體數字。獨立于CPU外的CXL內存延遲在170-250ns左右,高過獨立于CPU的NVM、網絡連接的解構內存、SSD和HDD等。

CXL總裁Siamak Tavallaei在SC22上表示,CXL實際上包含三種協議,但并非所有協議都是延遲的靈丹妙藥。CXL.io(運行在PCIe總線的物理層上)仍然具有與以往相同類型的延遲,但其他兩個協議,CXL.cache和CXL.mem采用了更快的路徑,減少了延遲。

Tavallaei解釋說,大多數CXL內存控制器會增加大約200納秒的延遲,額外的重定時器會增加或花費幾十納秒,具體取決于設備與CPU的距離。這與其他CXL早期采用者所看到的一致。但是GigaIO首席執行官Alan Benjamin對外表示,它所見過的大多數CXL內存擴展模塊的延遲都接近250納秒,而不是170納秒。

另外值得一提的是,來自Meta和AMD的兩位專家提出了一個概念,也就是對內存進行分層,分為用于實時分析等關鍵任務的“熱”內存、訪問不那么頻繁的“暖”內存和用于龐大數據的“冷”內存。“熱”內存頁面放在原生DDR內存里,而“冷”內存頁面則交給CXL內存。

但是當前的軟件應用可能無法有效區分“熱”內存和“冷”內存。在原生內存用完后,就會去占用CXL內存。如此一來原本作為“冷”內存的CXL,也開始變成“熱”內存。所以目前最大的挑戰就是在操作系統和軟件層面,如何檢測到“冷”內存頁面,將其主動轉入CXL內存里,為原生內存留出空間。Meta和AMD的兩位專家表示,他們已經在開發相應的軟硬件技術。

就現在服務器市場情況看,低核心數的CPU依然會繼續使用原生DDR通道來配置DIMM內存。而只有高核心數CPU上,再根據系統成本、容量、功耗和帶寬等參數來靈活應用CXL內存,因為這才是CXL的核心優勢,

目前,CXL生態系統才剛剛起步。許多企業還處于找相應的廠商的拿工程樣品搭建環境進行開發測試的階段。隨著時間的推移,業界預計延遲問題會大大改善。

結語

隨著各大廠家對CXL技術布局的愈發完善,一幅關于未來服務器行業的發展圖景也愈發清晰。

我們在思考這項新技術時,也正期待著它無限的可能性,距離產品的落地時間愈發接近,其后續表現如何,我們拭目以待。

審核編輯 :李倩

-

寄存器

+關注

關注

31文章

5357瀏覽量

120632 -

存儲器

+關注

關注

38文章

7513瀏覽量

163987 -

SK海力士

+關注

關注

0文章

968瀏覽量

38569

原文標題:大內存時代振奮人心的CXL技術(下)

文章出處:【微信號:TRENDFORCE,微信公眾號:TrendForce集邦】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CES Asia 2025多方成果斐然

拓展AI數據中心內存,第二代AMD Versal Premium系列自適應SoC,首發支持CXL 3.1、 PCIe Gen6

研華科技推出SQRAM CXL 2.0 Type 3內存模塊SQR-CX5N

如何利用CXL協議實現高效能的計算架構

三星電子突破瓶頸,HBM3e內存芯片獲英偉達質量認證

三星半導體新帥激勵員工,共克AI時代挑戰

TLB成功開發出CXL內存模塊PCB,并向三星和SK海力士提供首批樣品

業界首創512GB CXL AIC內存擴展卡,江波龍革新AI與高性能計算領域內存技術

FORESEE CXL 2.0內存拓展模塊

三星研發CXL混合存儲模組,實現閃存與CPU數據直傳

站群服務器需要多大內存

利用CXL技術重構基于RDMA的內存解耦合

大內存時代振奮人心的CXL技術(下)

大內存時代振奮人心的CXL技術(下)

評論