數(shù)字硬件建模SystemVerilog(一)-RTL和門級建模

接下來系列文章會有很多在Verilog中知識點有被提及,關(guān)于這兩者關(guān)系,請查看《談?wù)刅erilog和SystemVerilog簡史,FPGA設(shè)計是否需要學(xué)習(xí)SystemVerilog》。

本文定義了通常用于描述使用SystemVerilog對硬件功能進行建模的詳細(xì)級別的術(shù)語。

抽象

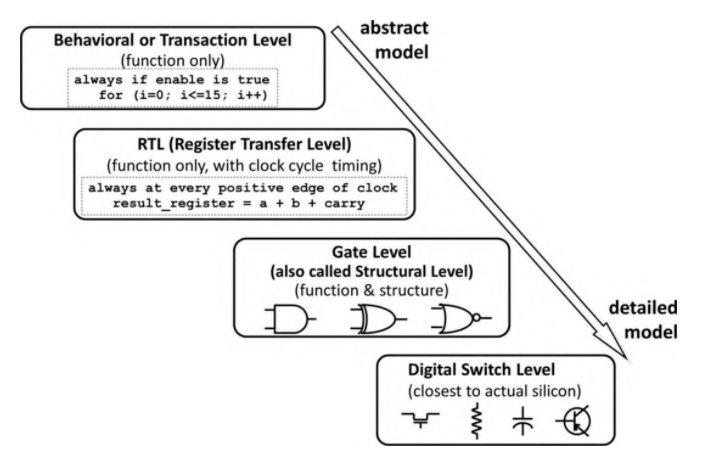

SystemVerilog能夠在許多不同的細(xì)節(jié)級別(稱為“抽象級別”)對數(shù)字邏輯進行建模。抽象意味著缺乏細(xì)節(jié)。數(shù)字模型越抽象,它所代表的硬件的細(xì)節(jié)就越少。

圖1-3顯示了SystemVerilog中可用的建模抽象的主要級別的詳細(xì)模型

圖1-3:SystemVerilog建模抽象級別

門級建模

SystemVerilog支持使用門級原語對數(shù)字邏輯進行建模。數(shù)字邏輯門是一個非常接近硅(silicon)實現(xiàn)的詳細(xì)模型。

SystemVerilog提供了幾個內(nèi)置的門級原語,并允許工程師定義其他原語,這些原語是指用戶定義的原語(UDP)。SystemVerilog中的內(nèi)置原語列在表1-1中:

表1-1:SystemVerilog門級原語

| 原語 | 描述 |

|---|---|

| 與and | 具有2個或更多輸入和1輸出的與門 |

| 與非門nand | 具有2個或更多輸入和1輸出的與非門 |

| 或or | 具有2個或更多輸入和1個輸出的或門 |

| 或非門nor | 具有2個或更多輸入和1輸出的或非門 |

| 異或門xor | 具有2個或更多輸入和1輸出的異或門 |

| 異或非門是xnor | 具有2個或更多輸入和1輸出的異或非門 |

| 緩沖器buf | 具有1個輸入和1或更多輸出的緩沖門 |

| 反向門not | 具有1輸入和1或更多輸出的反向門 |

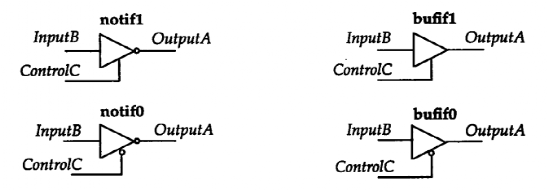

| buffif0 | 三態(tài)緩沖門,帶“1輸入*1輸出”和1個激活低啟用 |

| bufif1 | 具有1輸入、1輸出和1激活高啟用的三態(tài)緩沖門 |

| notif0 | 帶1輸入、1輸出和1低激活的三態(tài)反向緩沖門 |

| notif1 | 帶1輸入、1輸出和1高激活的三態(tài)反向緩沖門 |

SystemVerilog還為ASIC和FPGA庫開發(fā)人員提供了通過定義用戶定義原語(UDP)添加到內(nèi)置原語集的方法。UDP以表格格式定義,表格中的每一行列出一組輸入值和結(jié)果輸出值。組合邏輯和順序邏輯(如觸發(fā)器)原語都可以定義。

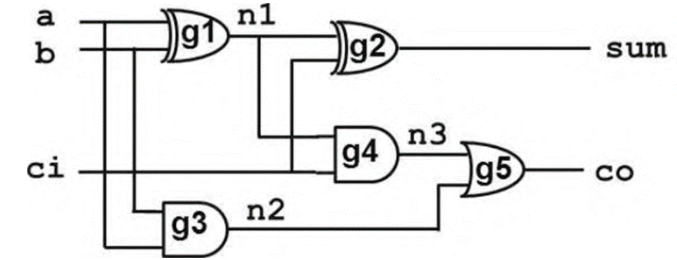

圖1-4顯示了帶進位的1位加法器的門級電路。示例1-1顯示了“使用原語對電路建模的SystemVerilog代碼”。

圖1-4:帶進位的1位加法器,用邏輯門表示示例1-1;帶進位的1位加法器的SystemVerilog門級模型

`begin_keywords

"1800-2012"

modulegate_adder

(inputwirea,b,ci,

outputwiresum,co

);

timeunit1ns;timeprecision100ps;

wiren1,n2,n3;

xorg1(n1,a,b);

xor

#1.3g2(sum,n1,ci);

andg3(n2,a,b);

andg4(n3,n1,ci);

or

#(1.5,1.8)g5(co,n2,n3);

endmodule:gate_adder

`end_keywords

門級原語的語法非常簡單:

<>

type

>〈instancename>(,);

許多門級原語可以具有可變數(shù)量的輸入。例如,and原語可以表示2輸入、3輸入或4輸入與門,如下所示:

and i1{o1,a,b);//2-輸入與門

and i2(o2,a,b,c};//3-輸入與門

and i3{o3,a,b,c,d);//4-輸入與門

原語的實例名稱雖然是可選的,但它是良好的代碼注釋,它使維護代碼和將SystemVerilog源代碼與示意圖或設(shè)計的其他表示形式聯(lián)系起來變得容易。實例名稱是用戶定義的,可以是任何合法的SystemVerilog名稱。

門級原語可以用傳播延遲來建模。如果未指定延遲,則門輸入上的更改將立即反映在門輸出上。延遲是一個表達式,可以是一個簡單的值,如示例1-1中的實例g2,也可以是一個更復(fù)雜的表達式,如實例g5。上述代碼中的柵極g2的傳播延遲為13ns,這意味著當(dāng)其中一個柵極輸入上發(fā)生轉(zhuǎn)換時,在柵極輸出sum改變之前,這個時間是13ns。門g5將傳播延遲分為不同的延遲,用于輸出上的上升和下降躍遷。如果co值從0轉(zhuǎn)換為l,延遲為1ns。如果co正在從1轉(zhuǎn)換為0,更改延遲為1.8ns。

門級模型能夠以高精度表示實際硅的傳播延遲。邏輯門的功能反映了將在硅中使用的晶體管組合的功能,并且門延遲可以反映通過這些晶體管的傳播延遲。ASIC和FPGA供應(yīng)商使用這種精度對特定設(shè)備的詳細(xì)行為進行建模。

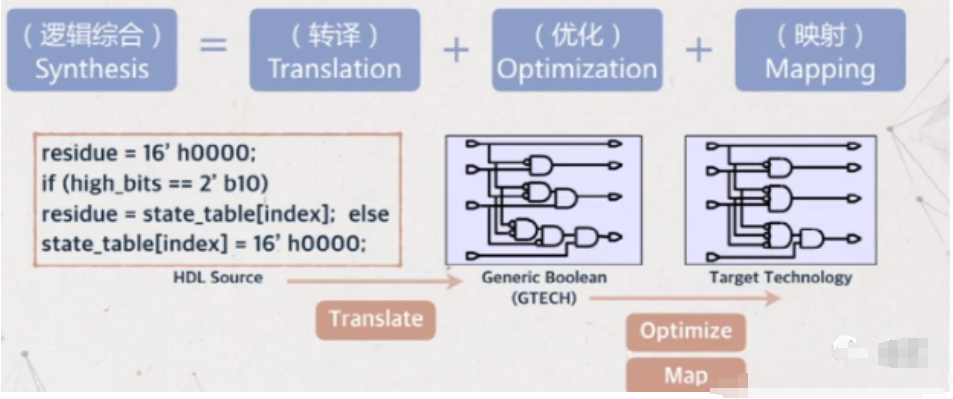

門級模型通常由軟件工具或?qū)iT從事庫開發(fā)的工程師生成。在RTL級別設(shè)計的設(shè)計工程師很少(如果有的話)使用門級原語建模。相反,RTL設(shè)計者使用門級模型的網(wǎng)表,其中網(wǎng)表是通過合成RTL模型生成的。網(wǎng)表級模型由目標(biāo)ASIC或FPGA設(shè)備的供應(yīng)商提供。關(guān)于門級建模的內(nèi)容比本文中介紹的要多得多。

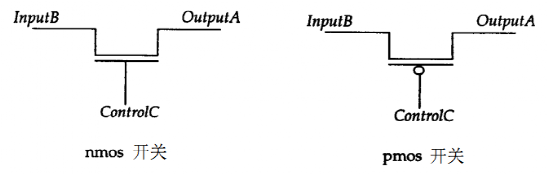

開關(guān)級建模。SystemVerilog還可以使用開關(guān)原語(如pmos、nmos和cmos)、電阻開關(guān)原語(如rpmos、cnmos和rcmos)和電容網(wǎng)絡(luò)在晶體管級對數(shù)字電路建模。這種級別的建模可以很好地表示實際的硅實現(xiàn)。然而,由于這些結(jié)構(gòu)只能仿真數(shù)字行為,因此很少使用。晶體管、電阻器和電容器都是仿真器件。數(shù)字仿真不能準(zhǔn)確反映晶體管的行為。開關(guān)級建模通常不在SystemVerilog的FPGA設(shè)計流程中使用。

RTL模型

一個更抽象的建模級別——也是系列文章的重點——是寄存器傳輸級別(Register Transfer Levels),或RTL。此級別的建模使用編程語句和運算符表示數(shù)字功能。RTL模型是功能模型,不包含有關(guān)如何在硅中實現(xiàn)該功能的詳細(xì)信息。由于這種抽象,復(fù)雜的數(shù)字功能可以比在詳細(xì)的門級更快速、更簡潔地建模。RTL模型的仿真速度也大大快于門級和開關(guān)級模型,這使得驗證更大、更復(fù)雜的設(shè)計成為可能。SystemVerilog為RTL建模提供了兩種主要結(jié)構(gòu):連續(xù)賦值(continuous assignments)和always程序塊。

連續(xù)賦值以assign關(guān)鍵字開始,可以表示簡單的組合邏輯。前面的示例1-1說明了1-bit加法器的門級模型。示例1-2顯示了如何通過使用連續(xù)賦值在更抽象的層次上建模相同的1位加法器功能:

`begin_keywords

"1800-2012"

modulertl_adder

(inputlogica,b,ci,

outputlogicsum,co

);

timeunit1ns/1ns;

assign{co,sum}=a+b+ci;

endmodule:rtl_adder

`end_keywords

示例1-2:帶進位的1位加法器的SystemVerilog RTL模型

RTL建模的一個優(yōu)點是代碼更易于自文檔化(self-documenting)。查看示例1-1中的門級模型并識別模型所代表的內(nèi)容可能很困難,尤其是在沒有注釋和有意義的名稱的情況下。但是,查看示例1-2中RTL模型中的代碼并認(rèn)識到該功能是一個加法器要容易得多。

RTL建模的另一個強大優(yōu)勢是能夠處理矢量和數(shù)據(jù)包。矢量是一個大于一位寬的信號。開關(guān)級和門級建模的操作一1位寬的信號,在SystemVerilog中稱為標(biāo)量信號。要對32位加法器進行建模,需要對每個位上運行的開關(guān)或門進行建模,這與實際硅中的操作相同。上述示例1-2中的連續(xù)賦值語句可以通過改變信號的聲明,對任意大小的加法器進行建模。

更復(fù)雜的功能可以使用程序塊建模。程序塊封裝了一行或多行編程語句,以及有關(guān)何時執(zhí)行這些語句的信息。RTL級別使用四種類型的always過程:always、always_comb、always_ff和always_latch。

以下示例簡明地表示具有寄存器輸出的32位加法器/減法器:

`begin_keywords

"1800-2012"

(inputlogicclk,//1-bitscalarinput

inputlogicmode,//1-bitscalarinput

inputlogic[31:0]a,b,//32-bitvectorinputs

outputlogic[31:0]sum//32-bitvectoroutput

);

timeunit1ns/1ns;

always_ff@(posedgeclk)begin

if

(mode==0)sum<=?a?+?b;

else

sum<=?a?-?b;

end

endmodule:rtl_adder_subtracter

`end_keywords

示例1-3:32位加法器/減法器的SystemVerilog RTL模型

在一個典型的仿真和綜合設(shè)計流程中,工程師們將花費大部分時間在RTL級別建模和驗證RTL功能。

行為級和事務(wù)級建模

SystemVerilog過程塊可用于在比RTL更高的抽象級別上建模,該抽象通常被稱為行為模型(也稱為總線功能或算法模型)。行為模型可能看起來與RTL模型非常相似,因為RTL和行為模型都是程序塊。行為模型在兩個方面與RTL有所不同。

高級抽象是事務(wù)級建模。事務(wù)模型通常用于驗證代碼中,并且通常使用SystemVerilog的面向?qū)ο缶幊探Y(jié)構(gòu)進行建模。

RTL綜合編譯器無法綜合抽象的行為和事務(wù)級別,本系列中也沒有討論.

?RTL模型必須遵守嚴(yán)格的語言限制,才能由RTL綜合編譯器進行合成。行為模型可以使用完整的SystemVerilog語言。

?RTL程序塊在單個時鐘周期內(nèi)執(zhí)行其編程語句,如果是組合邏輯,則在零周期內(nèi)執(zhí)行。行為模型過程塊可以使用任意數(shù)量的時鐘周期來執(zhí)行其語句。

-

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110077 -

System

+關(guān)注

關(guān)注

0文章

165瀏覽量

36930 -

建模

+關(guān)注

關(guān)注

1文章

304瀏覽量

60765

發(fā)布評論請先 登錄

相關(guān)推薦

RTL級設(shè)計的基本要素和步驟是什么

RTL級仿真與門級仿真

RTL級的功能仿真結(jié)果和系統(tǒng)級建模仿真的結(jié)果比較

關(guān)于RTL仿真和門級仿真求助~

【小白入門筆記】 小腳丫實現(xiàn)38譯碼器——模塊建模和門級建模初探

【FPGA學(xué)習(xí)】Verilog HDL 語言的描述語句之門級建模形式

什么是IP開發(fā)及FPGA建模?

Verilog HDL為門級電路建模的能力詳解

FPGA基礎(chǔ)設(shè)計之使用邏輯門和連續(xù)賦值對電路建模

基于Verilog的開關(guān)級建模

RTL和門級建模

RTL和門級建模

評論