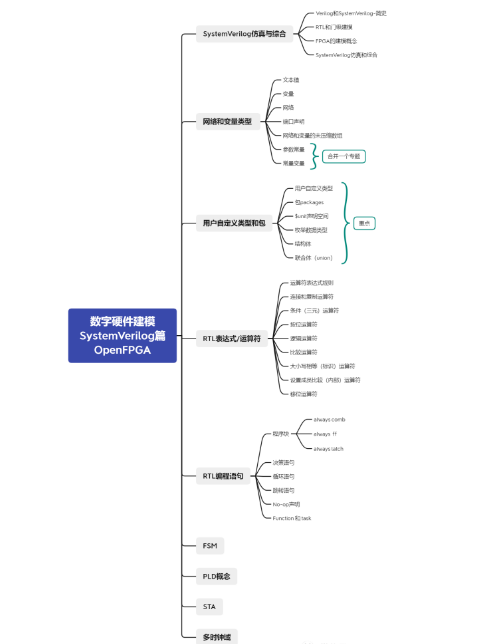

數字硬件建模SystemVerilog-程序塊 (procedural blocks)

經過幾周的更新,SV核心部分用戶自定義類型和包內容已更新完畢,接下來就是RTL編程語句。

程序塊是編程語句的容器。程序塊的主要目的是控制何時應執行編程語句,例如每當時鐘上升沿出現時,或每當信號或總線改變值時。SystemVerilog有兩種主要類型的程序塊: initial 程序塊和always 程序塊。

initial 程序是一種驗證結構;綜合編譯器不支持。但是有一個例外是,綜合編譯器支持使用或readmemh系統任務加載內存塊或分配給特定內存地址的 initial 程序。FPGA綜合器可能還允許使用 initial 程序對設備通電狀態進行建模,本文不討論或使用 initial 程序,因為它們不用于對RTL功能進行建模。

過程是無限循環。它們執行編程語句,完成后自動重新開始。一般的概念是,當電源打開時,硬件在做一些連續的事情。這種連續行為是使用always 程序建模的。

SystemVerilog有四種類型的always 程序:使用關鍵字always的通用過程和使用關鍵字always_ff, always_comb 和 always_latch的專用always 過程。

always 程序塊可用于多種類型建模,包括可綜合RTL模型、抽象行為模型(如不會綜合的RAM)以及驗證代碼(如時鐘振蕩器或連續響應檢查器)。雖然通用always程序的靈活性使其在各種建模和驗證項目中都很有用,但同樣的靈活性意味著軟件工具不知道always的預期用途是什么,什么時候用于可綜合的RTL模型。為了將RTL模型準確地轉換為ASIC或FPGA設備,綜合器對通用always程序設置了許多編碼限制。

專用的RTL程序。Always_ff、always_comb和always_latch專用always程序塊的行為與通用always程序塊相同,但會施加綜合所需的特殊編碼限制。這些額外的限制有助于確保RTL仿真的行為與實際ASIC或FPGA的門級行為相匹配。正如這些專用程序的名稱所表明的,Always_ff對仿真觸發器等時序邏輯器件施加了某些綜合限制。Always_comb為建模組合邏輯(如解碼器)施加了某些綜合限制,always_latch為建模鎖存行為施加了某些綜合限制。后面會詳細說明每個過程塊功能及驗證。

敏感列表

always 程序告訴仿真,應該“always”評估被建模的功能(一個無限循環),但仿真和綜合都需要了解更多信息,以便準確地建模硬件行為。這些工具還需要知道何時執行程序塊中的語句。對于RTL建模,時間要么在表示時序邏輯的時鐘邊沿上,要么在表示組合邏輯或鎖存邏輯的過程更改值所使用的任何信號上。

為了控制在可綜合RTL模型中何時執行編程語句,程序是以敏感列表開始,敏感列表是一個信號列表,值的變化將觸發程序的執行。通用always和RTL特定always_ff程序要求RTL設計工程師明確規定靈敏度列表。RTL特定的always_comb和always_latch程序將推斷出一個隱式靈敏度列表。

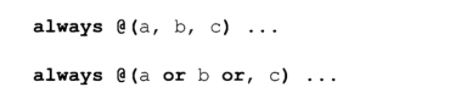

顯式指定的敏感度列表與@標記一起引入,口頭上稱為“at”。在可綜合RTL建模中,靈敏度列表包含一個或多個網絡或變量名的列表。名稱可以用逗號(,)或關鍵字”or”分隔。

以下兩個明確的敏感度列表功能相同:

在敏感度列表的上下文中,or關鍵字只是一個分隔符:它不是or操作。逗號與關鍵字or的使用取決于用戶的偏好。一種風格在功能上并不優于另一種風格。

靈敏度列表還可以指定標量(l位)信號的特定邊沿,該邊沿將觸發always 程序。邊沿由關鍵詞posedge和negedge指定,邊沿靈敏度對于基于時鐘的功能非常重要:

always@(posedgeelkornegedgerstN)…

posedge關鍵字是“正邊沿”的縮寫,negedge是“負邊沿”的縮寫。正邊沿是任何可能被硅晶體管感知為正向過渡的過渡。因此,posedge將在0-to-1、0-to-z、0-to-x、z-to-1、x-to-l、z-to-x和x-to-z轉換時觸發,相反,negedge將在1-to-0、1-to-z、1-to-x、z-to-0、x-to-0、z-to-x和x-to-z轉換時觸發.

時序邏輯靈敏度。時序邏輯元件,如觸發器,在時鐘邊沿觸發,通常是該時鐘的上升沿。(一些ASIC和FPGA設備具有在時鐘下降沿觸發的組件,很少有在時鐘兩側觸發的組件。)為了指示always 程序代表時鐘觸發的時序邏輯行為,always或always_ff關鍵字后跟:

@(posedge或者@(negedge)name>

例如:

always_ff@(posedgeclk)

q<=?d;?//時序邏輯觸發器

一些時序元件具有異步輸入,例如set或reset控制。這些異步信號也會影響仿真或綜合時評估always程序的運行時間,因此也應該包括在靈敏度列表中。

后面章節更詳細地討論了時序邏輯的建模,包括同步和異步set、enable控制,以及正確使用通用always和專用always_ff程序塊的指南。

組合邏輯靈敏度。組合邏輯(如加法器或解碼器)的輸出反映了該邏輯塊當前輸入值的組合。因此,每當組合邏輯的任何輸入值改變時(即敏感度列表),就需要重新評估組合邏輯中的編程語句。為了仿真這種行為,always關鍵字后面是一個明確的敏感度列表,其中包括該邏輯塊讀取的所有信號,其形式為:

@(,,…)name>

例如:

always@(a,b)

sum=a+b;

always_comb專用always程序的一個特點是,它自動推斷出一個合適的組合邏輯靈敏度列表。上述加法器代碼使用always_comb建模為:

always_comb@(a,b)

sum=a+b;

后面章節將更詳細地討論組合邏輯建模,以及always和always_comb程序塊的正確使用指南。

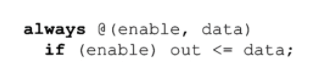

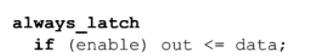

latch邏輯靈敏度。鎖存是組合邏輯塊的一種形式,可以存儲其當前狀態,建模鎖存行為遵循與建模組合邏輯行為相同的敏感度列表規則。Always_latch關鍵字后面是一個靈敏度列表,其中包括該邏輯塊讀取的所有信號,格式為:

@(,,…)name>

如下所示:

Always_latch專用always程序自動推斷出正確的組合邏輯靈敏度列表。

后續章節將更詳細地討論了鎖存邏輯的建模,包括使用always和always_latch程序塊的最佳實踐編碼指南。

不可綜合的敏感度列表。從語法上講,靈敏度列表可以包含操作,例如@(a+b)或iff保護條件,posedge和negedge限定符也可以用于大于1位寬的向量,但只使用向量的最低有效位(最右邊的位),向量中其他位的更改不會觸發敏感度列表,RTL綜合編譯器通常不支持操作:iff和向量邊沿(posedge和negedge)。

begin-end語句組

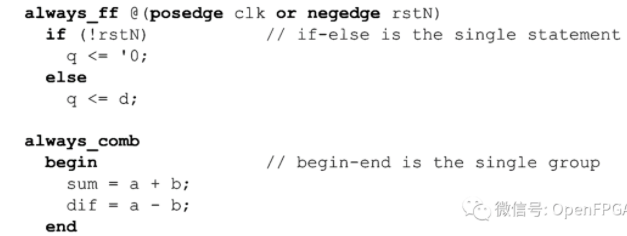

所有形式的程序塊都可以包含一條語句或一組語句。語句組包含在關鍵字begin和end之間,可以包含任意數量的語句,包括none語句。下面的代碼片段顯示了一個包含單個語句的always 程序和一個包含begin end組的always 程序。

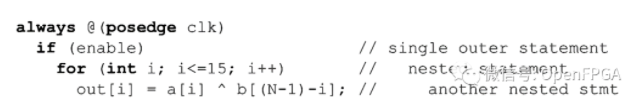

一條語句可以嵌套在另一條語句中,如:

在前面的代碼段中,外部語句是always 程序中的單個語句,因此不需要begin-end語句組。

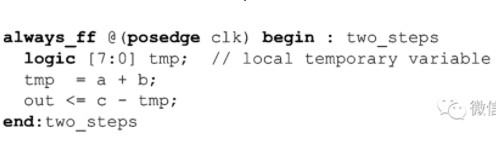

可以使用以下語法命名begin-end語句組:

begin:

命名語句組可以包含局部變量聲明,局部變量可以在語句組內使用,但不能在可綜合RTL模型的組外引用,(SystemVerilog的更高版本增加了在未命名的begin端組中聲明局部變量的功能,但在編寫本文時,大多數綜合編譯器都不支持這種功能。)

也可以選擇命名組的匹配端。命名語句組的結尾可以幫助直觀地匹配嵌套的語句組。SystemVerilog要求用于開始和結束的名稱必須完全匹配。

局部變量的使用有助于確保在某些情況下得到適當的綜合結果。在時序always程序中計算并由另一個程序使用的臨時中間變量可能在仿真中起作用,但可能綜合出與RTL仿真行為不匹配的門級功能,在過程中聲明局部變量將防止此編碼錯誤-無法從過程外部訪問局部變量,

下面的示例聲明了一個臨時變量,該變量位于always_ff 過程的局部。臨時變量用于計算中間結果,然后用于計算最終結果(本例中的計算特意保持簡單,以便專注于局部變量的聲明,而不是一些可能需要中間計算的復雜算法)

請注意,冒號前后允許有空白,如上面的begin后面所示。但是,end后面不能有空白,如上圖所示。使用空格有助于使復雜的代碼更易于閱讀。

在程序塊中使用變量和網絡

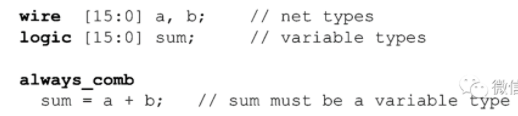

程序賦值的左側只能是變量類型,包括基于變量的用戶自定義類型。在運算符或賦值語句更新之前,變量仍然保持其先前的值,變量的這種特性會影響仿真和綜合。

在下面的代碼段中,sum必須聲明為變量類型,因為它位于過程賦值的左側。有關RTL建模中可使用的可綜合變量類型的討論,請參見之前的文章。

只有程序賦值的左側必須是變量。賦值的右側可以使用變量、網絡、參數或文字值。

-

Verilog

+關注

關注

28文章

1351瀏覽量

110074 -

System

+關注

關注

0文章

165瀏覽量

36928 -

容器

+關注

關注

0文章

495瀏覽量

22060

發布評論請先 登錄

相關推薦

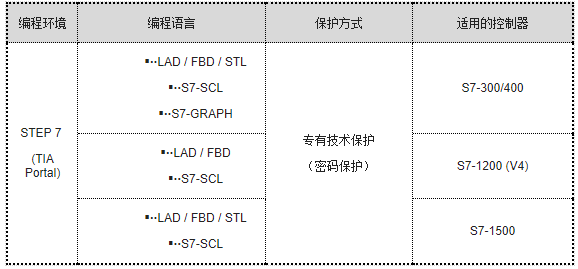

【轉】淺談西門子plc程序加密和程序塊加密及解密

在STEP7中對程序塊加密

如何暫停GRAPH程序塊

TIA Portal的程序塊保護功能實現

Sivarc畫面規則:建立程序塊與畫面的鏈接

上載程序塊--STEP7 V12及其以上版本軟件

決策語句允許程序塊的執行流程

西門子S7-1200/1500程序塊加密,你真的了解嗎?

如何實現暫停GRAPH程序塊?

什么是程序塊

什么是程序塊

評論