為高效的低損耗功率開關應用選擇低導通電阻 MOSFET?不要忘記檢查是否有隱藏的妥協。

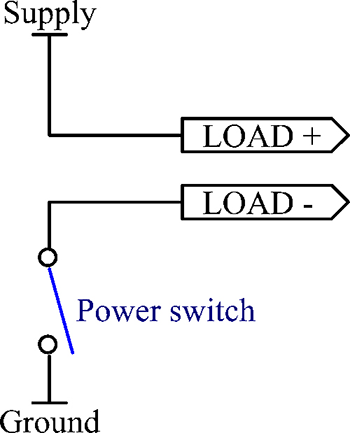

耗電應用要求提高系統效率,以滿足消費者和監管部門對更清潔空氣和減少碳足跡的要求。這推動了對理想的“無損耗”電源開關的需求,在大多數現代電子系統中,這種開關是通過功率MOSFET實現的。

完美的電源開關在關閉時具有無限電阻,打開時具有零電阻,并且關閉和打開之間的轉換將是瞬時的,而不會引起尖峰或其他瞬態噪聲。然而,在MOSFET的現實世界中,關斷時的電阻是有限的,總會有一些漏電流(IDSS),并且半導體制造商嘗試時,打開時的電阻(RDS(開啟)) 永遠不會為零。但這并不能阻止他們試圖盡可能低。

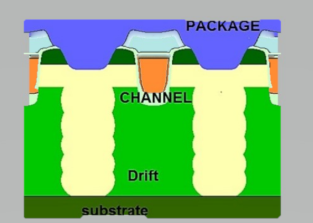

降低R的各種方法DS(開啟)可以使用溝槽MOSFET,每種MOSFET都可能產生不必要的副作用,從而影響各種應用的性能。

對于典型的功率MOSFET,溝槽結構的“有源”部分包含在硅的頂部幾μm內,大部分損耗發生在該區域內。剩余的硅,稱為基板,在制造過程中提供機械穩定性。減小基板厚度可以顯著降低MOSFET的電阻和熱阻,但背面研磨會產生額外的成本。

細胞間距

較低的RDS(開啟)大多數供應商通常通過添加更多并行通道來實現,這通常會降低電池間距,這會導致熱不穩定,因為相鄰電池會導致溫升影響通道的閾值電壓。它還會增加MOSFET的電容,從而影響開關性能。相反,SOA可能會因窄細胞間距而受到嚴重影響。超結技術使用帶有P型支柱的更深溝槽可以在不降低電池間距的情況下降低通道電阻,并且不會影響SOA性能。

漂移電阻,通過改變漂移區域的摻雜 RDS(開啟)可以減少,但 IDSS漏電流和VDS關斷條件下的額定電壓可能會受到負面影響。我DSS通常用于制造最終測試以篩選出有缺陷的設備,接受更高的泄漏電流可能意味著在最終測試期間可能未檢測到更多有缺陷的產品

溝槽阻力

封裝電阻

通過使用銅夾和漏極焊盤代替鍵合線,可以降低封裝電阻,結合使用多個源極引腳,在產品的整個生命周期內,還將對電感、額定電流、熱性能和魯棒性產生積極影響。

不言而喻,降低 RDS(開啟)有時會導致不必要的權衡,要求苛刻的應用(如電源ORing,熱插拔,電機驅動和負載切換)可能無法接受這些權衡 - 也不應該接受。

下一頁 PowerS3 MOSFET – 具有軟恢復功能的超快速開關

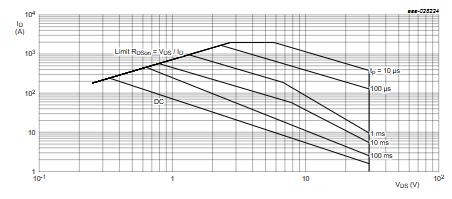

Nexperia最新加入NextPowerS3產品組合,將超結技術與銅夾式LFPAK封裝相結合,提供具有競爭力的RDS(開啟)走向市場。最新器件提供 0.5 mΩ(典型值)、高達 380 A 的直流額定電流,此外還有 6 倍的線性模式 (SOA) 性能(見下圖)和極具競爭力的 Q 值g, 1DS(開啟)品質因數。

新部件在不影響其他重要參數的情況下提高了性能。

PSMNR58-30YLH安全操作區域;連續和峰值漏極電流與漏源電壓的關系

審核編輯:郭婷

-

電源

+關注

關注

184文章

17704瀏覽量

249961 -

MOSFET

+關注

關注

147文章

7156瀏覽量

213145 -

SOA

+關注

關注

1文章

287瀏覽量

27463

發布評論請先 登錄

相關推薦

什么是電源開關,它們在哪里使用?

尋找完美的電源開關

尋找完美的電源開關

評論