電子集成技術(shù)分為三個層次,芯片上的集成,封裝內(nèi)的集成,PCB板級集成,其代表技術(shù)分別為SoC,SiP和PCB(也可以稱為SoP或者SoB)。

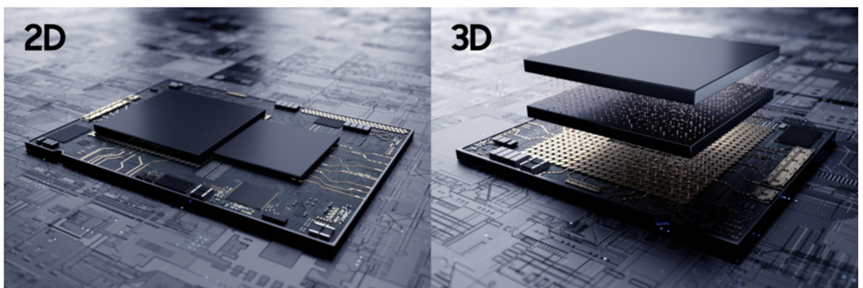

芯片上的集成主要以2D為主,晶體管以平鋪的形式集成于晶圓平面;同樣,PCB上的集成也是以2D為主,電子元器件平鋪安裝在PCB表面,因此,二者都屬于2D集成。而針對于封裝內(nèi)的集成,情況就要復(fù)雜的多。

電子集成技術(shù)分類的兩個重要判據(jù):1.物理結(jié)構(gòu),2.電氣連接(電氣互連)。

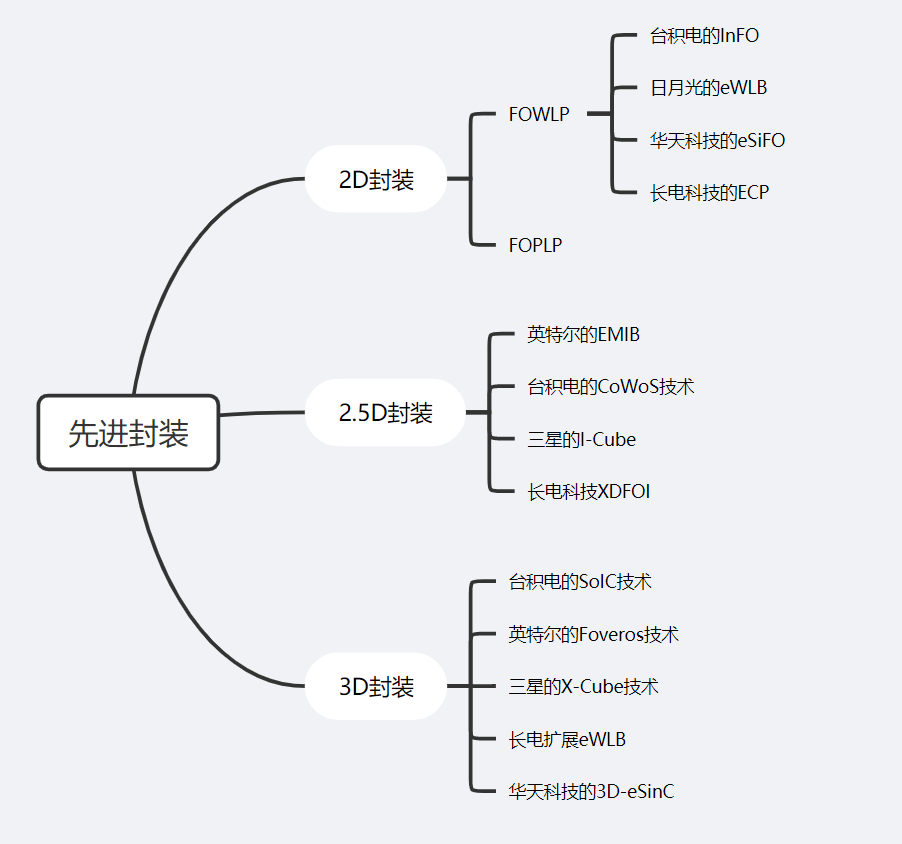

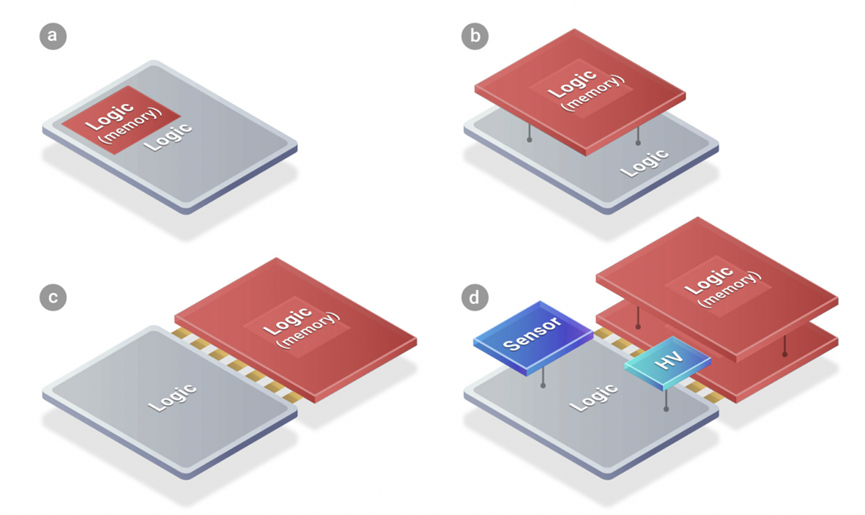

目前先進封裝中按照主流可分為2D封裝、2.5D封裝、3D封裝三種類型。

2D封裝

2D封裝是指在基板的表面水平安裝所有芯片和無源器件的集成方式。2D封裝上包括FOWLP、FOPLP等技術(shù)。

物理結(jié)構(gòu):所有芯片和無源器件均安裝在基板平面,芯片和無源器件和 XY 平面直接接觸,基板上的布線和過孔均位于 XY 平面下方;電氣連接:均需要通過基板(除了極少數(shù)通過鍵合線直接連接的鍵合點)

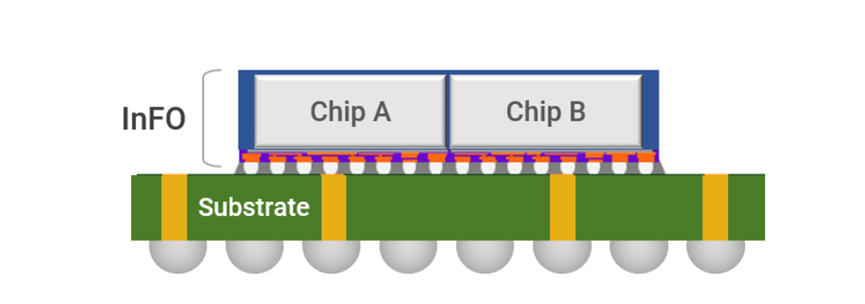

臺積電的InFO:

臺積電在2017年開發(fā)的InFO技術(shù)。InFO技術(shù)與大多數(shù)封裝廠的Fan-out類似,可以理解為多個芯片F(xiàn)an-out工藝的集成,主要區(qū)別在于去掉了silicon interposer,使用一些RDL層進行串連(2016年推出的iPhone7中的A10處理器,采用臺積電16nm FinFET工藝以及InFO技術(shù))。

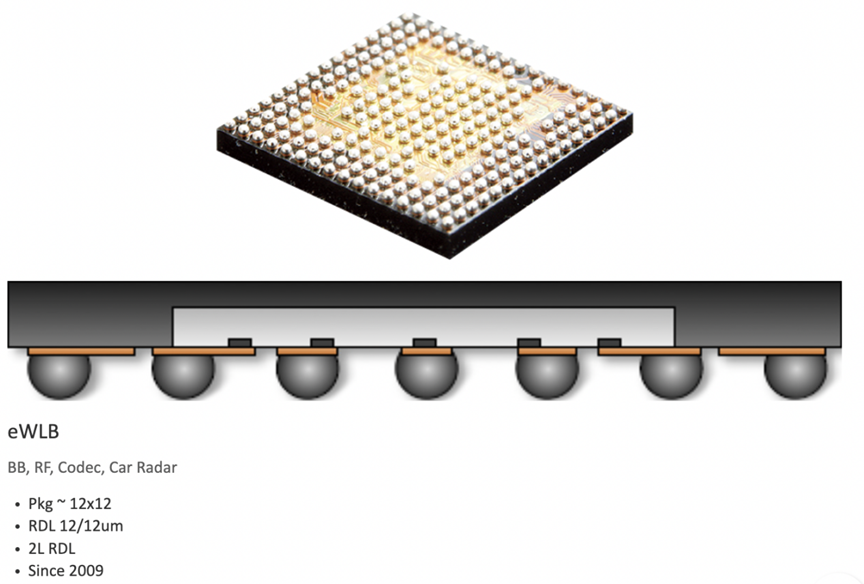

日月光的eWLB:與臺積的InFO類似,都屬于Fan-out技術(shù)

另外,還有一種2D+ 集成

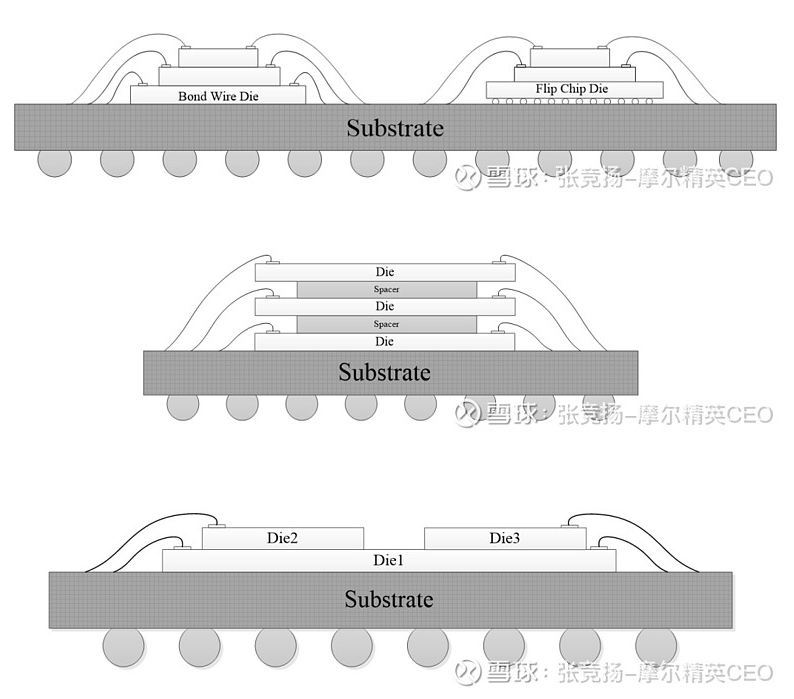

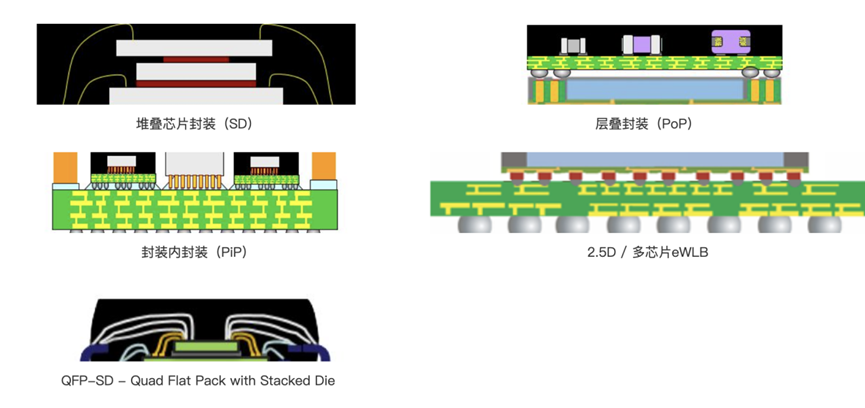

2D+集成是指的傳統(tǒng)的通過鍵合線連接的芯片堆疊集成。也許會有人問,芯片堆疊不就是3D嗎,為什么要定義為2D+集成呢?

主要基于以下兩點原因:

1)3D集成目前在很大程度上特指通過3D TSV的集成,為了避免概念混淆,我們定義這種傳統(tǒng)的芯片堆疊為2D+集成;

2)雖然物理結(jié)構(gòu)上是3D的,但其電氣互連上均需要通過基板,即先通過鍵合線鍵合到基板,然后在基板上進行電氣互連。這一點和2D集成相同,比2D集成改進的是結(jié)構(gòu)上的堆疊,能夠節(jié)省封裝的空間,因此稱之為2D+集成。

物理結(jié)構(gòu):所有芯片和無源器件均地位于XY平面上方,部分芯片不直接接觸基板,基板上的布線和過孔均位于XY平面下方;

電氣連接:均需要通過基板(除了極少數(shù)通過鍵合線直接連接的鍵合點)

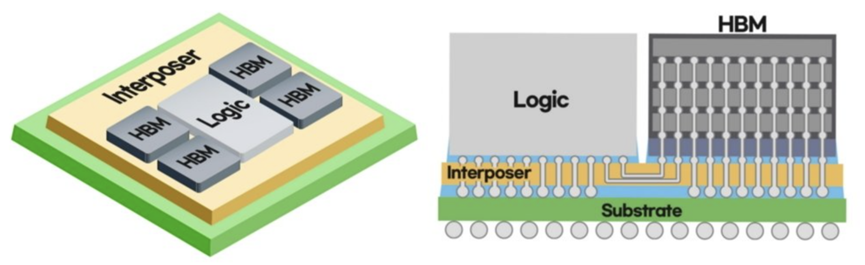

2.5D封裝:

2.5D封裝通常是指既有2D的特點,又有部分3D的特點,其中的代表技術(shù)包括英特爾的EMIB、臺積電的CoWoS、三星的I-Cube。

物理結(jié)構(gòu):所有芯片和無源器件均XY平面上方,至少有部分芯片和無源器件安裝在中介層上(Interposer),在XY平面的上方有中介層的布線和過孔,在XY平面的下方有基板的布線和過孔。

電氣連接:中介層(Interposer)可提供位于中介層上的芯片的電氣連接。

2.5D集成的關(guān)鍵在于中介層Interposer,一般會有幾種情況,1)中介層是否采用硅轉(zhuǎn)接板,2)中介層是否采用TSV,3)采用其他類型的材質(zhì)的轉(zhuǎn)接板;在硅轉(zhuǎn)接板上,我們將穿越中介層的過孔稱之為TSV,對于玻璃轉(zhuǎn)接板,我們稱之為TGV。

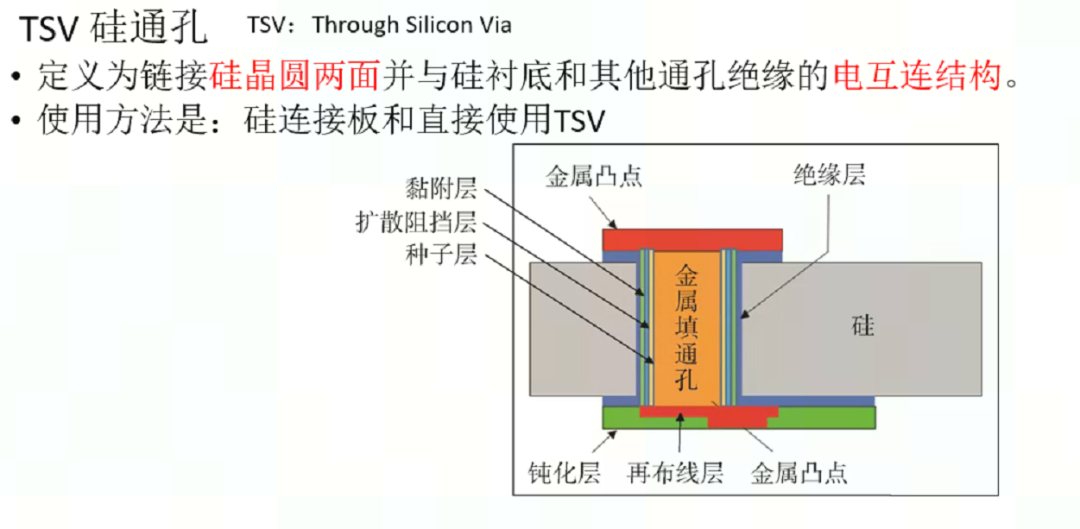

所謂的TSV 指的是:

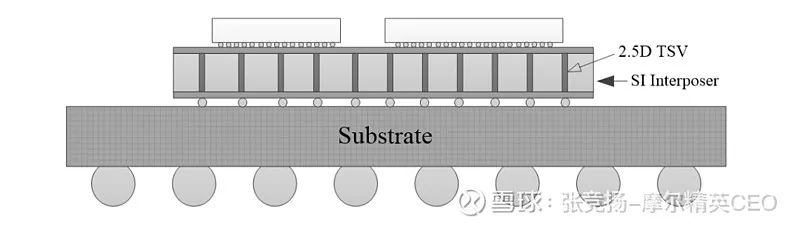

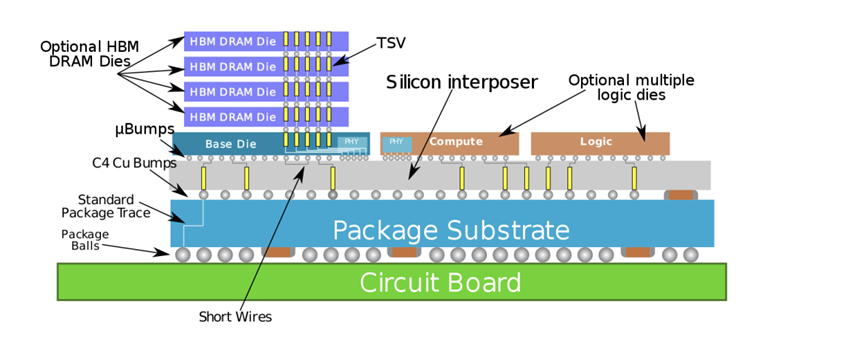

硅中介層有TSV的集成是最常見的一種2.5D集成技術(shù),芯片通常通過MicroBump和中介層相連接,作為中介層的硅基板采用Bump和基板相連,硅基板表面通過RDL布線,TSV作為硅基板上下表面電氣連接的通道,這種2.5D集成適合芯片規(guī)模比較大,引腳密度高的情況,芯片一般以FlipChip形式安裝在硅基板上。

有TSV的2.5D集成示意圖:

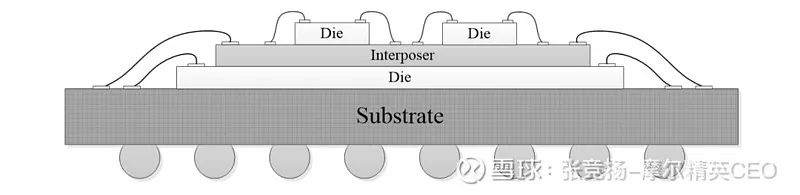

硅中介層無TSV的2.5D集成的結(jié)構(gòu)一般如下圖所示,有一顆面積較大的裸芯片直接安裝在基板上,該芯片和基板的連接可以采用Bond Wire或者Flip Chip兩種方式,大芯片上方由于面積較大,可以安裝多個較小的裸芯片,但小芯片無法直接連接到基板,所以需要插入一塊中介層(Interposer),在中介層上方安裝多個裸芯片,中介層上有RDL布線,可將芯片的信號引出到中介層的邊沿,然后通過Bond Wire連接到基板。這類中介層通常不需要TSV,只需要通過Interposer上表面的布線進行電氣互連,Interposer采用Bond Wire和封裝基板連接。

無TSV的2.5D集成示意圖:

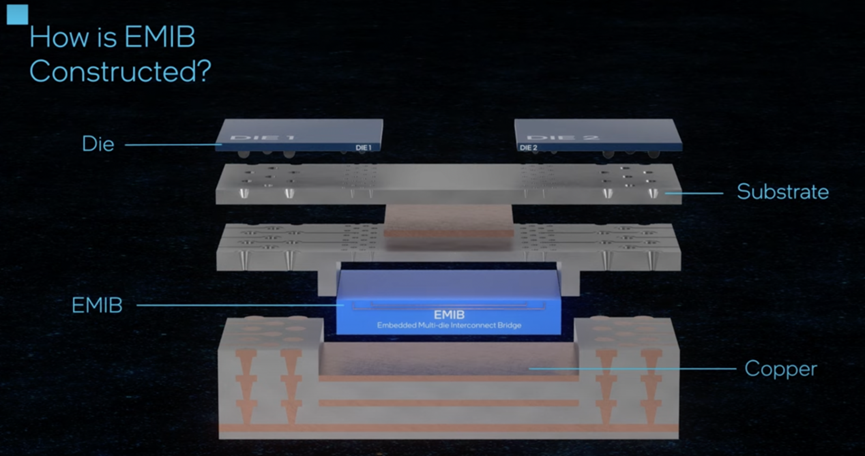

英特爾的EMIB:

概念與2.5D封裝類似,但與傳統(tǒng)2.5D封裝的區(qū)別在于沒有TSV。也正是這個原因,EMIB技術(shù)具有正常的封裝良率、無需額外工藝和設(shè)計簡單等優(yōu)點。

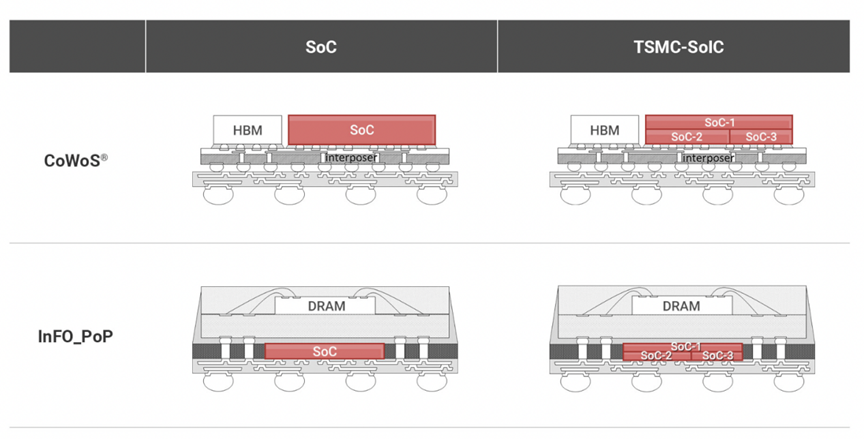

臺積電的CoWoS技術(shù)

臺積電的CoWoS技術(shù)也是一種2.5D封裝技術(shù)。根據(jù)中介層的不同可以分為三類,一種是CoWoS_S使用Si襯底作為中介層,另一種是CoWoS_R使用RDL作為中介層,第三種是CoWoS_L使用小芯片(Chiplet)和RDL作為中介層。

臺積電InFO(2D)與CoWoS(2.5D)之間的區(qū)別在于,CoWoS針對高端市場,連線數(shù)量和封裝尺寸都比較大;InFO針對性價比市場,封裝尺寸較小,連線數(shù)量也比較少。

第一代CoWoS主要用于大型FPGA。CoWoS-1的中介層芯片面積高達約800mm2,非常接近掩模版限制。第二代CoWoS通過掩模拼接顯著增加了中介層尺寸。臺積電最初符合1200mm2的要求,此后將中介層尺寸增加到1700mm2。這些大型封裝稱為CoWoS-XL2。

最近,臺積電公布的第五代CoWoS-S的晶體管數(shù)量將增加20倍,中介層面積也會提升3倍。第五代封裝技術(shù)還將封裝8個128G的HBM2e內(nèi)存和2顆大型SoC內(nèi)核。

長電科技XDFOI技術(shù):

相較于2.5D TSV封裝技術(shù),具備更高性能、更高可靠性以及更低成本等特性。該解決方案在線寬或線距可達到2um的同時,可實現(xiàn)多層布線層,另外,采用了極窄節(jié)距凸塊互聯(lián)技術(shù),封裝尺寸大,可集成多顆芯片、高帶寬內(nèi)存和無源器件。

三星的I-Cube

三星的具有的先進封裝包括I-Cube、X-Cube、R-Cube和H-Cube四種方案。其中,三星的I-Cube同樣也屬于2.5D封裝。

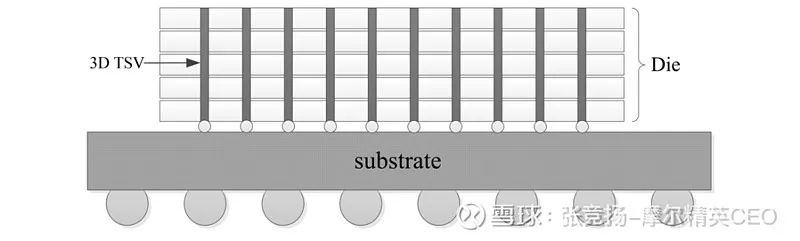

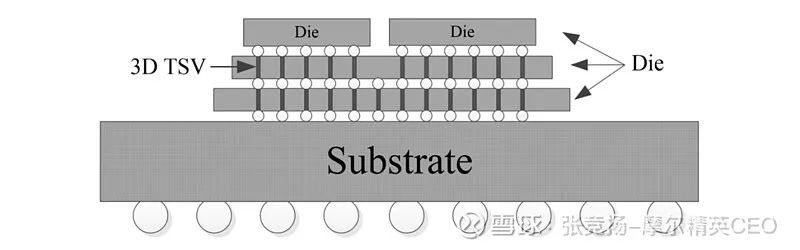

3D封裝:

3D封裝和2.5D封裝的主要區(qū)別在于:2.5D封裝是在Interposer上進行布線和打孔,而3D封裝是直接在芯片上打孔和布線,電氣連接上下層芯片。3D集成目前在很大程度上特指通過3D TSV的集成。

3D集成和2.5D集成的主要區(qū)別在于:2.5D集成是在中介層Interposer上進行布線和打孔,而3D集成是直接在芯片上打孔(TSV)和布線(RDL),電氣連接上下層芯片。

物理結(jié)構(gòu):所有芯片和無源器件均位于XY平面上方,芯片堆疊在一起,在XY平面的上方有穿過芯片的TSV,在XY平面的下方有基板的布線和過孔。

電氣連接:通過TSV和RDL將芯片直接電氣連接

3D集成大多數(shù)應(yīng)用在同類芯片堆疊中,多個相同的芯片垂直堆疊在一起,通過穿過芯片堆疊的TSV互連,如下圖所示。同類芯片集成大多應(yīng)用在存儲器集成中,例如DRAM Stack,F(xiàn)LASH Stack等。

同類芯片的3D集成示意圖:

不同類芯片的3D集成中,一般是將兩種不同的芯片垂直堆疊,并通過TSV電氣連接在一起,并和下方的基板互連,有時候需要在芯片表面制作RDL來連接上下層的TSV。

臺積電的SoIC技術(shù):

臺積電SoIC技術(shù)屬于3D封裝,是一種晶圓對晶圓(Wafer-on-wafer)的鍵合技術(shù)。SoIC技術(shù)是采用TSV技術(shù),可以達到無凸起的鍵合結(jié)構(gòu),把很多不同性質(zhì)的臨近芯片整合在一起,而且當(dāng)中最關(guān)鍵、最神秘之處,就在于接合的材料,號稱是價值高達十億美元的機密材料。

SoIC技術(shù)將同質(zhì)和異質(zhì)小芯片集成到單個類似SoC的芯片中,具有更小尺寸和更薄的外形,可以整體集成到先進的WLSI(又名CoWoS和InFO)中。從外觀上看,新集成的芯片就像一個通用的SoC芯片,但嵌入了所需的異構(gòu)集成功能。

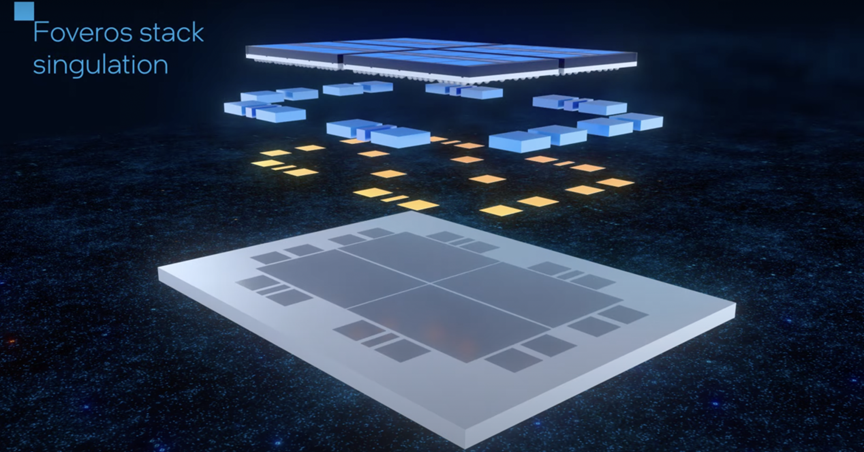

英特爾的Foveros技術(shù):

從3D Foveros的結(jié)構(gòu)上看,最下邊是封裝基底,之上安放一個底層芯片,起到主動中介層的作用。在中介層里有大量的TSV 3D硅穿孔,負(fù)責(zé)聯(lián)通上下的焊料凸起,讓上層芯片和模塊與系統(tǒng)其他部分通信。

三星的X-Cube 3D封裝技術(shù):

使用TSV工藝,目前三星的X-Cube測試芯片已經(jīng)能夠做到將SRAM層堆疊在邏輯層之上,通過TSV進行互聯(lián),制程是他們自家的7nm EUV工藝。

長電科技的擴展eWLB:

長電科技基于eWLB的中介層可在成熟的低損耗封裝結(jié)構(gòu)中實現(xiàn)高密度互連,提供更高效的散熱和更快的處理速度。3D eWLB互連(包括硅分割)是通過獨特的面對面鍵合方式實現(xiàn),無需成本更高的TSV互連,同時還能實現(xiàn)高帶寬的3D集成。

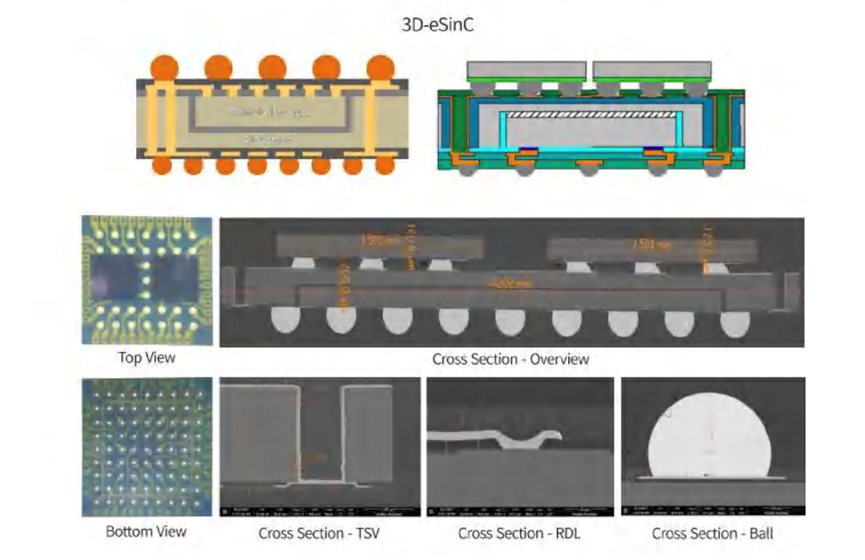

華天科技的3D-eSinC解決方案:

華天科技稱,2022年將開展2.5D Interpose FCBGA、FOFCBGA、3D FOSiP等先進封裝技術(shù),以及基于TCB工藝的3D Memory封裝技術(shù),Double Sidemolding射頻封裝技術(shù)、車載激光雷達及車規(guī)級12英寸晶圓級封裝等技術(shù)和產(chǎn)品的研發(fā)。

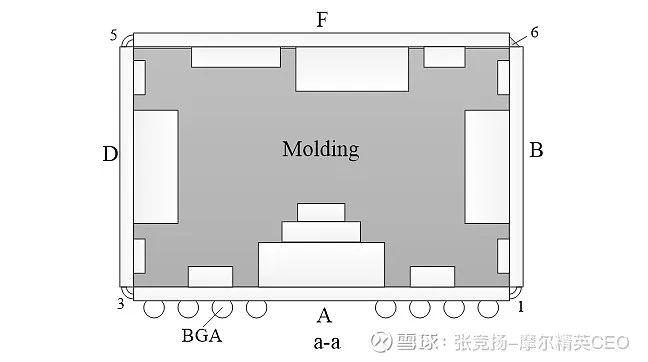

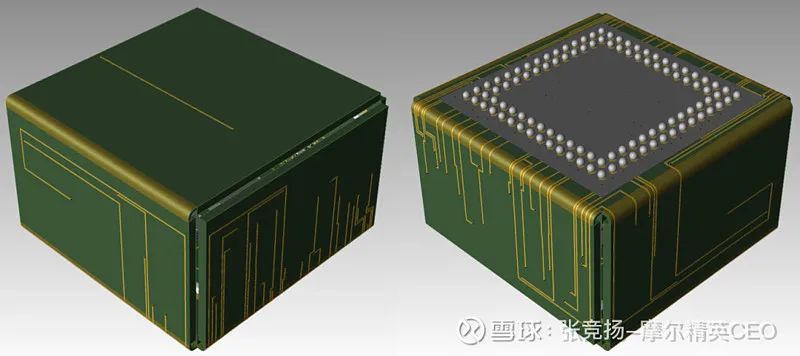

4D 集成:

物理結(jié)構(gòu):多塊基板以非平行方式安裝,每塊基板上都安裝有元器件,元器件安裝方式多樣化。電氣連接:基板之間通過柔性電路或者焊接連接,基板上芯片電氣連接多樣化。

基于剛?cè)峄宓?D集成示意圖:

4D集成定義主要是關(guān)于多塊基板的方位和相互連接方式,因此在4D集成也會包含有2D,2D+,2.5D,3D的集成方式

先進封裝設(shè)備類似前道晶圓制造設(shè)備,供應(yīng)商受益先進封測產(chǎn)業(yè)增長。隨著先進封裝的發(fā)展,Bumping(凸塊)、Flip(倒裝) 、TSV 和 RDL(重布線)等新的連接形式所需要用到的設(shè)備也越先進。以長球凸點為例,主要的工藝流程為預(yù)清洗、UBM、淀積、光刻、焊料 電鍍、去膠、刻蝕、清洗、檢測等,因此所需要的設(shè)備包括清洗機、PVD 設(shè)備、***、 刻蝕機、電鍍設(shè)備、清洗機等,材料需要包括光刻膠、顯影劑、刻蝕液、清洗液等。為促進行業(yè)發(fā)展,互通有無,歡迎芯片設(shè)計、晶圓制造、裝備、材料等產(chǎn)業(yè)鏈上下游加入艾邦半導(dǎo)體先進封裝產(chǎn)業(yè)鏈交流群。

審核編輯 :李倩

-

pcb

+關(guān)注

關(guān)注

4319文章

23095瀏覽量

397781 -

封裝

+關(guān)注

關(guān)注

126文章

7894瀏覽量

142942 -

晶體管

+關(guān)注

關(guān)注

77文章

9688瀏覽量

138157 -

先進封裝

+關(guān)注

關(guān)注

2文章

404瀏覽量

246

原文標(biāo)題:先進封裝——從2D,3D到4D封裝

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

3D封裝熱設(shè)計:挑戰(zhàn)與機遇并存

Altium Designer 09的3D封裝旋轉(zhuǎn)的問題

2D到3D視頻自動轉(zhuǎn)換系統(tǒng)

4D打印技術(shù)是什么,與3D打印有何區(qū)別?

3d人臉識別和2d人臉識別的區(qū)別

淺談電子集成技術(shù)先進封裝的從2D,3D,4D封裝

先進封裝-從2D,3D到4D封裝

【半導(dǎo)光電】先進封裝-從2D,3D到4D封裝

2D與3D視覺技術(shù)的比較

4DGen:基于動態(tài)3D高斯的可控4D生成新工作

先進封裝——從2D,3D到4D封裝

先進封裝——從2D,3D到4D封裝

評論