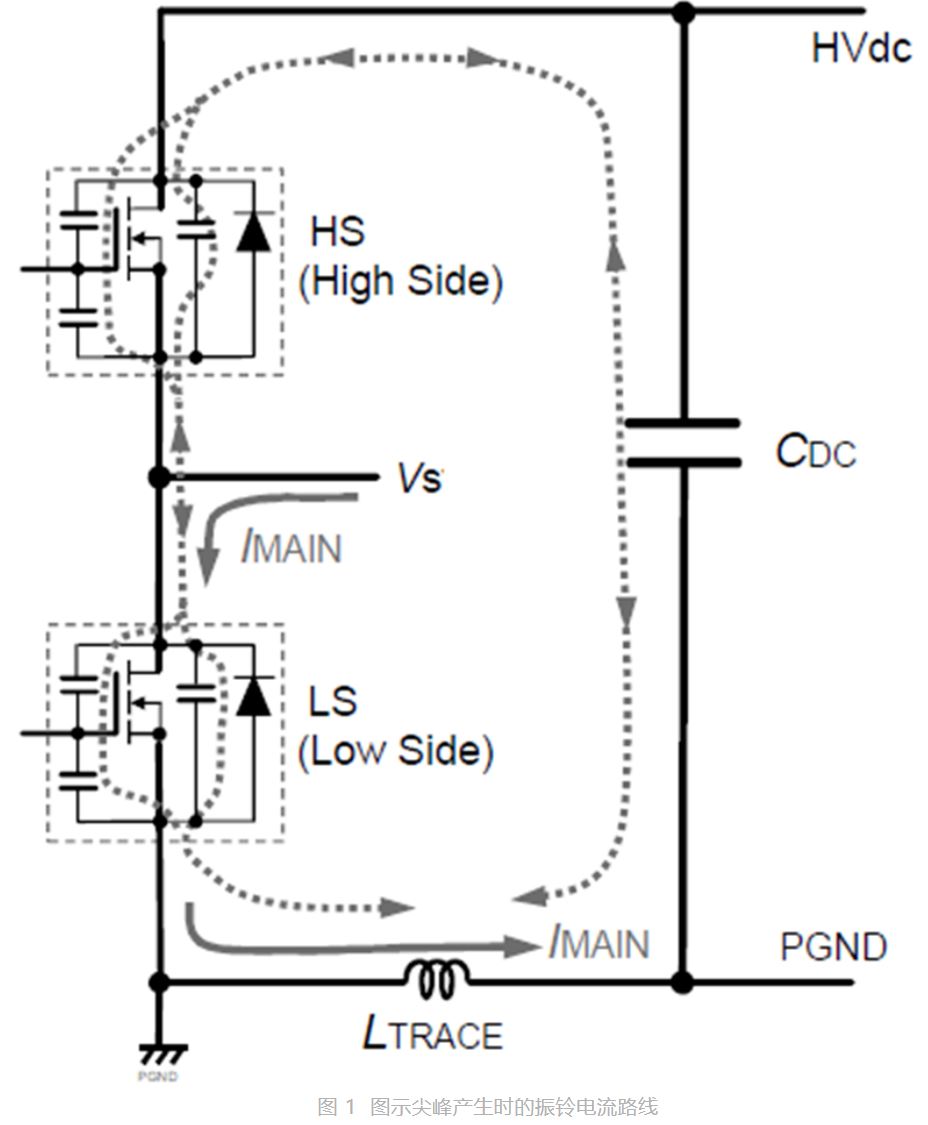

為了更好地發揮其的效果,必須將這些緩沖電路盡可能布局在在開關元件的附近。

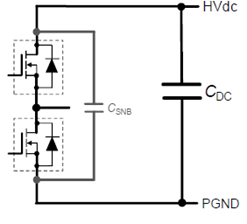

- CSNB緩沖電路零件數目少,但必須連接到橋式結構的上部和下部之間,因此缺點是線路會變得較長,因此通常不是用分立元器件,而是多用2合1 的分立元器件模塊。

- RC 緩沖電路可在各開關元件附近能布局緩沖電路,不過,必須確保每次元件Turn ON 時CSNB 中積存的全部能量均由RSNB 消耗掉。因此,當開關頻率變高時,RSNB 所消耗的電力可能會變為數W,而CSNB 很難很大,所以抑制尖峰的效果也會變得有限。此外,RSNB 的尖峰吸收能力有限,因此抑制效果也會受限。

- RCD 緩沖電路的RSNB 消耗的電力與(b)相同,但因為只經由二極管吸收尖峰,比起(b)的吸收效果高、更實用。但是,需要注意使用的二極管的恢復特性,因為吸收尖峰時的電流變化大,需要極力減少緩沖電路的配線電感。另外,如果將RSNB 與CSNB 并聯,在動作上也是相同的。

- 非放電型RCD 緩沖電路的RSNB 只消耗CSNB 所吸收的電壓尖峰能量,CSNB 所積蓄的能量不會每次開關都充分釋放出來。因此,即使開關頻率加快,RSNB 的消耗功率也不會變得很大,可以將CSNB 增大,大幅提高電路的抑制效果。但樣線路布局變得復雜,如果不是4 層以上的基板,布線會極為困難。

如上所述,這里介紹的緩沖電路各有長短,需要根據電源電路結構和轉換功率容量選擇最佳的緩沖電路。

緩沖電路的設計方法

1.

圖5所示的緩沖電路是通過CSNB 吸收LTRACE 積蓄的能量。因此,在緩沖電路中形成的LSNB 必須比LTRACE 小。由于CSNB 中積蓄的能量基本不放電,靜電容量越大電壓尖峰抑制效果變好,但使用的電容器的等價串聯電感 (ESL) 也必須考慮到LSNB 中。一般來說,電容器的尺寸越大ESL 越大,在選擇靜電容量時要注意。

圖5 CSNB緩沖電路

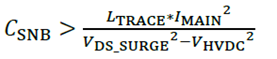

為了將LTRACE 中積蓄的能量全部用CSNB 吸收, 需以算式(2)所示靜電電容為依據選定電容。

(2)

2.

RC 緩沖電路的設計

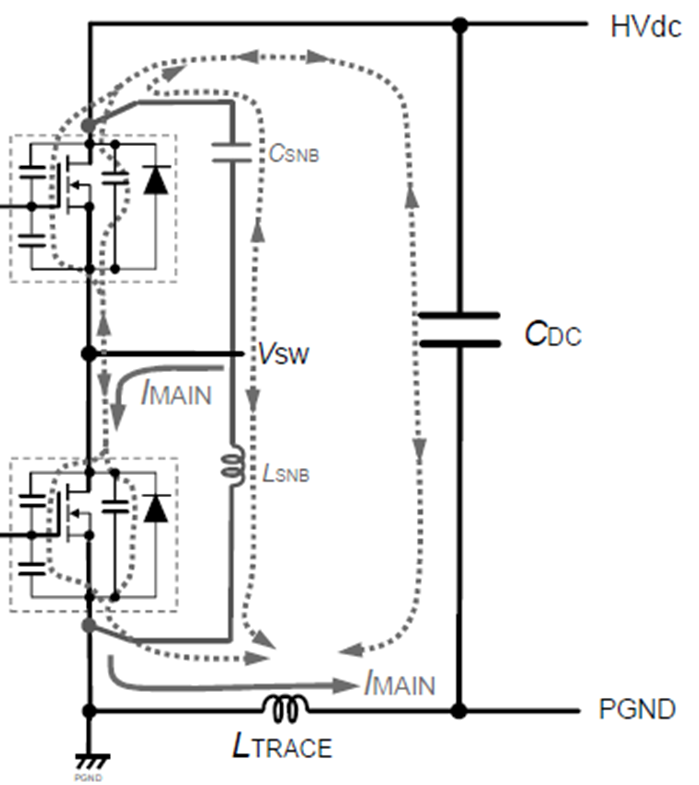

圖6所示為RC緩沖電路動作時的電流路徑與CSNB緩沖電路一樣:

圖6 RC 緩沖電路

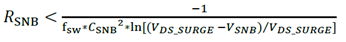

CSNB的數值由算式(2)決定,而RSNB 的參考值根據算式(3)求得。

(3)

fSW:開關頻率VSNB:放電緩沖電壓(VDS_SURGE 的0.9 倍)

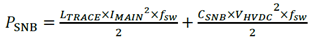

決定RSNB 之后,以算式(4)計算出RSNB 的消耗功率,選定功率滿足要求的電阻。

(4)

對于RC 緩沖電路,算式(4)追加了第二項,因為fSW 或VHVDC越高RSNB 所消耗的電力越大,PSNB 太大導致電阻選定困難時,必須降低CSNB 的靜電容量值重新計算。

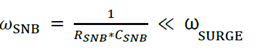

另外,為了RC 緩沖電路充分吸收電壓尖峰,RSNB 和CSNB 的諧振頻率ωSNB 必須比電壓尖峰的諧振頻率ωSURGE 低很多,需要結合算式(5)所示的RC 緩沖電路的諧振頻率ωSNB 來確認。

(5)

3.

放電型RCD 緩沖電路的設計

放電型RCD 緩沖電路的設計基本上與RC 緩沖電路相同。只是由于是通過二極管吸收的尖峰,所以不需要通過算式(5)確認諧振頻率。并且,二極管必須選定為恢復電流小的型號。

4.

非放電型RCD 緩沖電路的設計

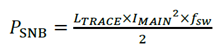

非放電型RCD 緩沖電路與放電型RCD 緩沖電路不同,RSNB消耗的電力僅限于電壓尖峰的能量,用于抑制容許損失的RSNB的選擇范圍很廣。因此可以增大CSNB 的靜電容量,提高鉗位的效果。CSNB 由算式(2)決定,RSNB 由算式(3)決定,而RSNB 的消耗功率由算式(6)決定,沒有算式(4)中包含CSNB 及fsw 的第二項。因此,由CSNB 或fsw 產生的消耗功率增加基本沒有,能選擇大的靜電容量的CSNB,不僅僅緩沖電路的鉗位效果更好,還能對應fsw 的高頻化。

(6)

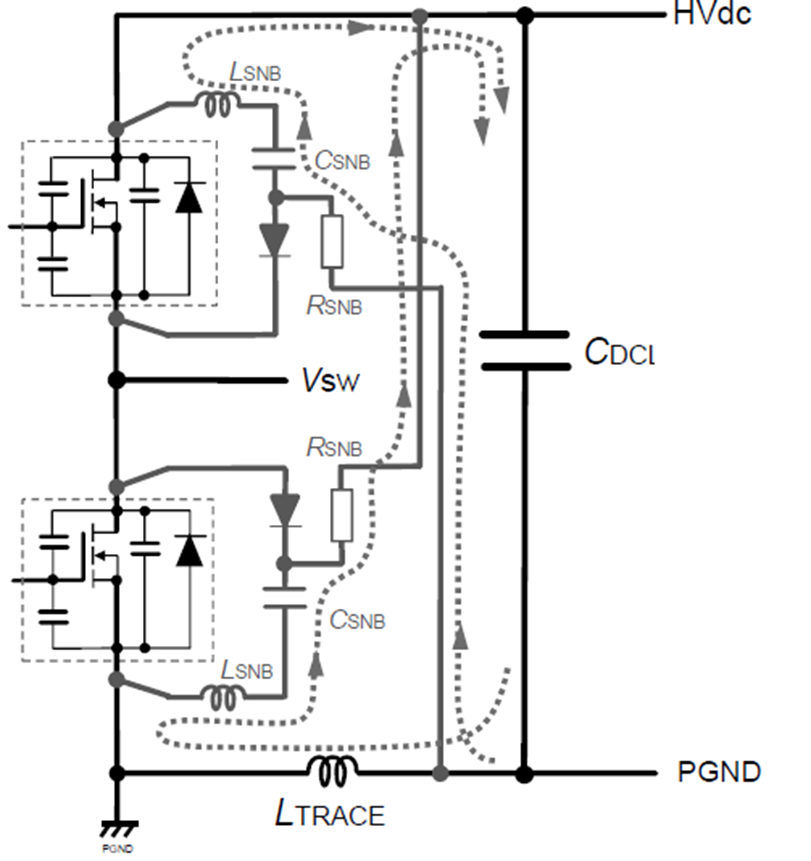

圖8所示為非放電型RCD 緩沖電路動作時的放電路徑。因為上臂的尖峰朝向PGND、下臂的尖峰朝向HVdc,放電流經由RSNB 流動,不那么受線路電感影響。另一方面,連接到MOSFET 的漏極源極之間的布線電感LSNB 因為電流變化大,電感值需要盡量小。

圖8 非放電型RCD 緩沖電路動作時的放電路徑

封裝不同而造成的電壓尖峰差異

最后說明的是,Turn OFF 尖峰根據封裝的不同而有差異。圖9是 SiC MOSFET 的代表性封裝, (a)是被廣泛采用的TO-247-3L,(b)是近幾年漸漸擴大采用的用于驅動電路的源極端子(即所謂的開爾文接法)的TO-247-4L。

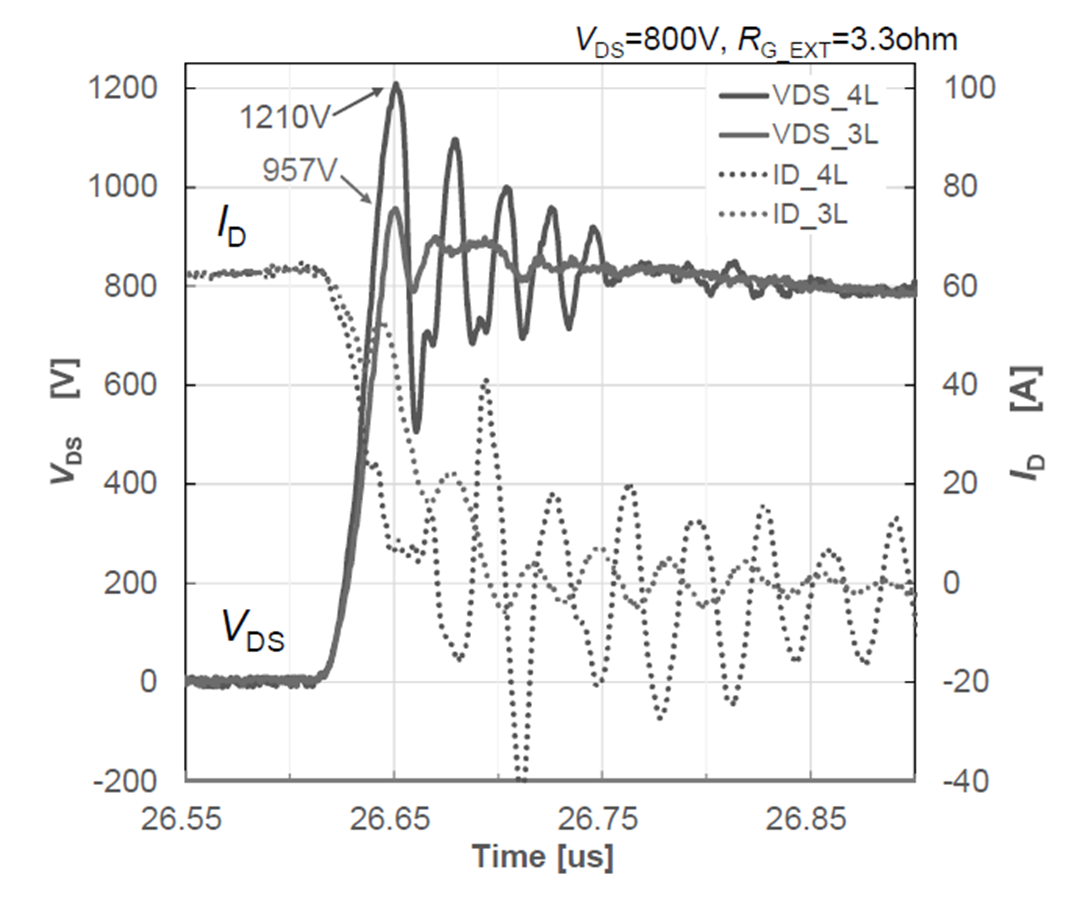

4L 型與3L 型相比,改變了驅動電路路徑,使開關速度加快。由于這個原因,Turn ON 電壓尖峰和Turn OFF 電壓尖峰變得更大。圖10為3L 類型和4L 類型的Turn OFF 電壓尖峰的對比波形。VDS=800V、RG_EXT=3.3Ω、ID=65A 時的Turn OFF波形,漏極源極間電壓尖峰3L 類型為957V,而4L 類型則為1210V。

圖10

如上所述,橋式電路中的MOSFET 的柵極信號在MOSFET之間相互關聯、動作,并在柵極源極之間產生預料之外的電壓尖峰,其抑制方法需要考慮基板的線路布線,根據情況不同采取不同的對應。

-

MOSFET

+關注

關注

147文章

7201瀏覽量

213624 -

SiC

+關注

關注

29文章

2841瀏覽量

62725 -

寬禁帶半導體

+關注

關注

0文章

92瀏覽量

8097

發布評論請先 登錄

相關推薦

碳化硅MOSFET的開關尖峰問題與TVS保護方案

簡述碳化硅MOSFET尖峰的抑制 2

簡述碳化硅MOSFET尖峰的抑制 2

評論