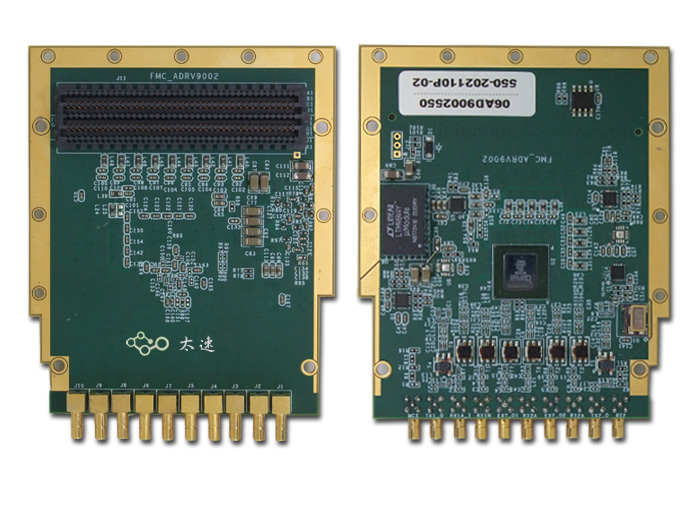

FMC550-基于ADRV9002雙窄帶寬帶射頻收發(fā)器FMC子卡

一、產(chǎn)品概述

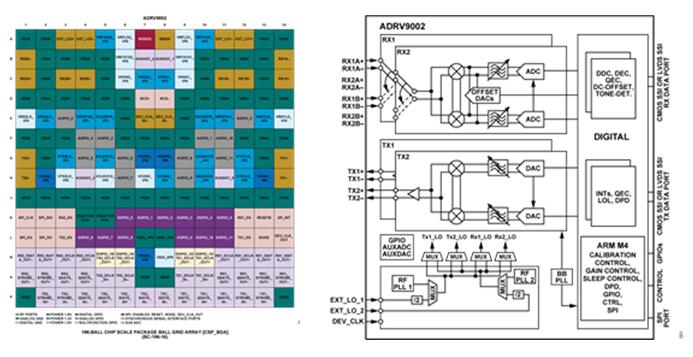

ADRV9002是一款高性能、高線性度、高動(dòng)態(tài)范圍收發(fā)器,旨在針對(duì)性能與功耗系統(tǒng)進(jìn)行優(yōu)化。該設(shè)備是可配置的,非常適合要求苛刻、低功耗、便攜式和電池供電的設(shè)備。ADRV9002的工作頻率為30MHz至6000MHz,涵蓋UHF、VHF、工業(yè)、科學(xué)和醫(yī)療(ISM)頻段、窄帶(kHz)的蜂窩頻段以及高達(dá)40MHz的寬帶操作。ADRV9002能夠同時(shí)進(jìn)行TDD和FDD操作。

收發(fā)器包括直接轉(zhuǎn)換信號(hào)路徑,具有先進(jìn)的噪聲指數(shù)和線性度。每個(gè)完整的接收器和變送器子系統(tǒng)都包括直流失調(diào)矯正、正交誤差校正(QEC)以及可編程數(shù)字濾波器,因此數(shù)字基帶中不再需要這些功能。另外,它集成了輔助模數(shù)轉(zhuǎn)換器(ADC)、輔助數(shù)模轉(zhuǎn)換器(DAC)以及通用輸入/輸出(GPIO)等若干輔助功能,因而可提供額外的監(jiān)測(cè)和控制能力。

完全集成的鎖相環(huán)(PLL)為變送器、接收器和時(shí)鐘部分提供高性能、低功耗小數(shù)N頻率合成。精心選用的設(shè)計(jì)和布局技術(shù)提供了高性能個(gè)人射頻應(yīng)用所需要的隔離。

其中集成了全部壓控振蕩器(VCO)和環(huán)路濾波器元件,從而盡可能減少外部元件數(shù)量。本地振蕩器(LO)具有靈活的配置選項(xiàng),并包括快速鎖定模式。

該收發(fā)器具有低功耗睡眠和監(jiān)控模式,可在監(jiān)控通信的同時(shí),節(jié)省功耗并延長(zhǎng)便攜式設(shè)備的電池壽命。

完全集成的低功耗數(shù)字預(yù)失真(DPD)針對(duì)窄帶和寬帶信號(hào)進(jìn)行了優(yōu)化,并實(shí)現(xiàn)了高效功率放大器的線性化。

ADRV9002的內(nèi)核可以直接由1.0V、1.3V和1.8V穩(wěn)壓器供電,并通過(guò)標(biāo)準(zhǔn)4線串行端口進(jìn)行控制。其他電源用來(lái)提供正確的數(shù)字接口電平,并優(yōu)化接收器、變送器和輔助轉(zhuǎn)換器性能。

使用可配置的CMOS或低電壓差分信號(hào)(LVDS)串行同步接口(SSI)選項(xiàng),可支持高數(shù)據(jù)速率和低數(shù)據(jù)速率接口。

二、優(yōu)勢(shì)和特點(diǎn)

?2×2高度集成的收發(fā)器

?頻率范圍為30MHz至6000MHz

?變送器和接收器帶寬為12kHz至40MHz

?兩個(gè)完全集成的小數(shù)N射頻頻率合成器

?LVDS和CMOS同步串行數(shù)據(jù)接口選項(xiàng)

?低功耗監(jiān)控器和休眠模式

?多芯片同步功能

?快速跳頻

?動(dòng)態(tài)配置文件切換,可實(shí)現(xiàn)動(dòng)態(tài)數(shù)據(jù)速率和采樣率

?完全集成的DPD,適用于窄帶和寬帶波形

?可通過(guò)4線SPI完全編程

?12mm×12mm、196球CSP_BGA

?通過(guò)FMC連接器連接FPGA母板(ZC706和ZCU102)

?采用單個(gè)FMC連接器供電

?包括原理圖、布局、BOM、HDL、驅(qū)動(dòng)程序和應(yīng)用軟件

三、產(chǎn)品應(yīng)用

?關(guān)鍵任務(wù)通信

?甚高頻(VHF)、超高頻(UHF),以及蜂窩到6GHz

?時(shí)分雙工(TDD)和頻分雙工(FDD)應(yīng)用

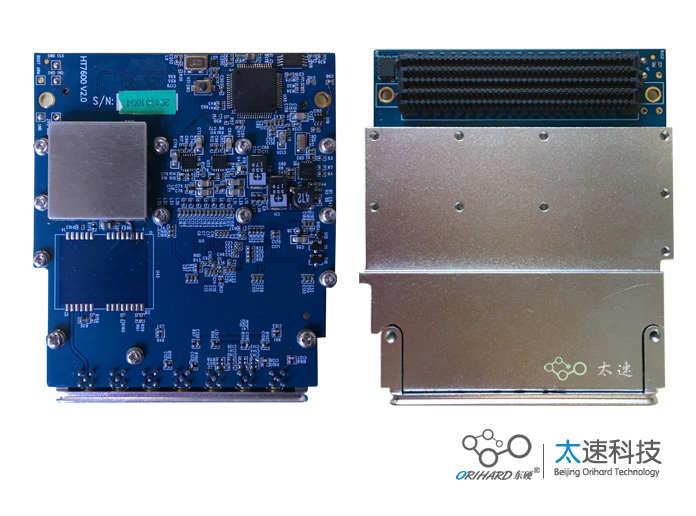

FMC177-基于AD9361的雙收雙發(fā)射頻FMC子卡

一、板卡介紹

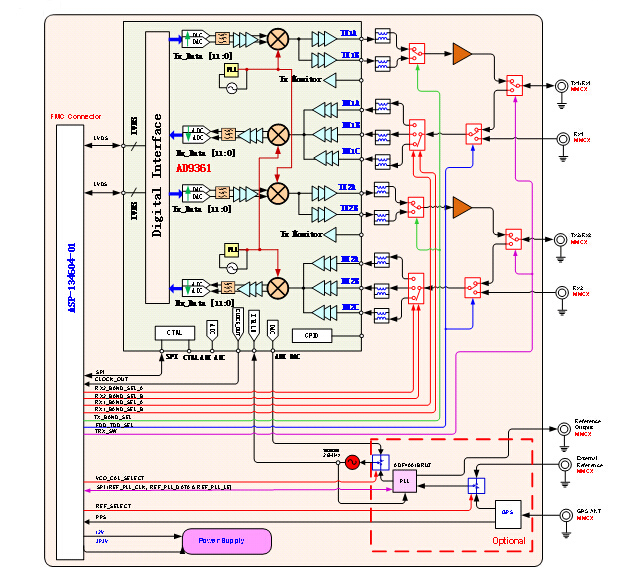

FMC177射頻模塊分別包含兩個(gè)接收通道與發(fā)射通道,其頻率可覆蓋達(dá)到70MHz~6GHz,AD9361芯片提供具有成本效益的實(shí)驗(yàn)平臺(tái),具有達(dá)到56MHz的瞬時(shí)帶寬,更高的靈敏度,靈活的動(dòng)態(tài)范圍,廣泛適合于SDR(無(wú)線電軟件),移動(dòng)基站,WiFi,無(wú)線局域網(wǎng),專用或通用無(wú)線電設(shè)備等應(yīng)用。設(shè)計(jì)者通過(guò)使用FMC177,可以有效簡(jiǎn)單的使用AD9361芯片。

二、主要指標(biāo)

1.射頻頻率:70MHz~6GHz;

2.ADC/DAC采集:12位;

3.兩路TX,兩路RX,工作實(shí)現(xiàn)方式雙工與半雙工;

5.瞬時(shí)帶寬:56MHz;

6.支持直流供電+12V;

7.支持GPS;

8.規(guī)格:標(biāo)準(zhǔn)FMC子卡。

三、板子接口特性

| No. | Items | Specifications | Remark | |

| Tx | 1 | Frequency | 70~6000MHz | |

| 2 | Bandwidth | Upto56MHz | real-timebandwidth,tunable | |

| 3 | Transmission | >5dBm | CW | |

| 4 | EVM | <1.5% | Typical:5dBm@20MHzbandwidth | |

| 5 | GainControlRange | >80dB | ||

| 6 | GainStep | 0.25dB | ||

| 7 | ACLR | @0dBmLTEoutput | ||

| 8 | Spurious | TBD | ||

| 9 | SSBSuppression | 35dBc | ||

| 10 | LOSuppression | 50dBc | ||

| 11 | DACSampleRate(max) | 61.44MS/s | ||

| 12 | DACResolution | 12bits | ||

| Rx | 1 | Frequency | 70~6000MHz | |

| 2 | Bandwidth | Upto56MHz | real-timebandwidth,tunable | |

| 3 | Sensitivity: | -90dBm@20MHz | NoiseFigure | |

| 4 | EVM | <1.5% | @-30dBminput | |

| 5 | GainControlRange | >60dB | ||

| 6 | GainStep | 1dB | ||

| 7 | Blocking | TBD | ||

| 8 | NoiseFigure | <8db | MaximumRXgain | |

| 9 | IIP3(@typNF) | -25dBm | ||

| 10 | ADCSampleRate(max) | 61.44MS/s | ||

| 11 | ADCResolution | 12bits | ||

| 12 | ADCWidebandSFDR | 78dBc | ||

| 1 | Voltage | 3.3V | ||

| 2 | ON/OFFTIME | <6us | ForTDDmodel | |

| 3 | DuplexingModel | TDDorFDD | ||

| 4 | W/GPSDOReference | 0.01ppb |

四、應(yīng)用范圍:

SDR(無(wú)線電軟件);移動(dòng)基站,例如Femto‐cells,Pico‐cells,Small‐cells,Micro‐cell等等;WiFi;無(wú)線局域網(wǎng);專用或通用無(wú)線電設(shè)備。

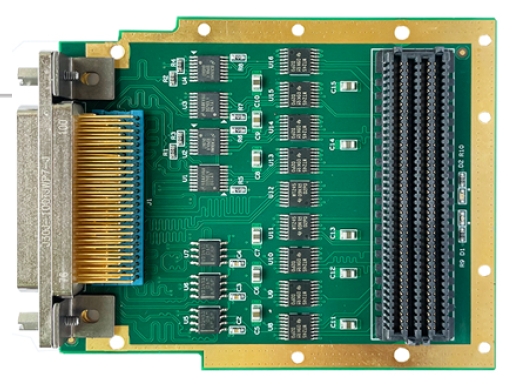

五、與FPGA處理卡搭建系統(tǒng)

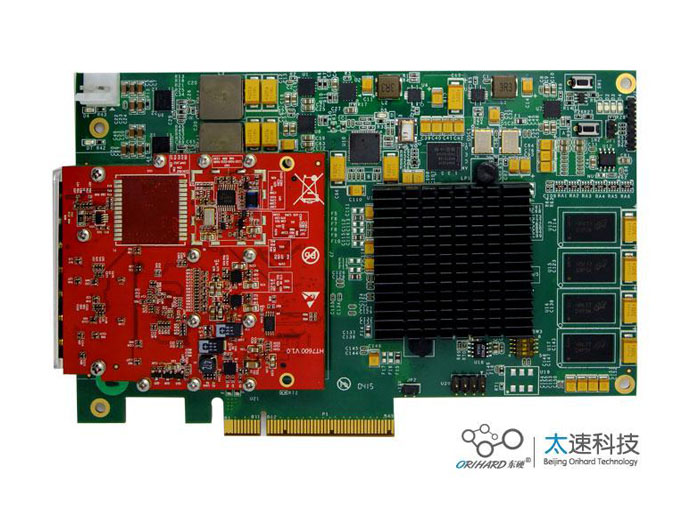

本板卡是將FMC177_AD9361射頻收發(fā)模塊與本公司基于FMC接口K7板卡通過(guò)標(biāo)準(zhǔn)的FMC接口相連接。

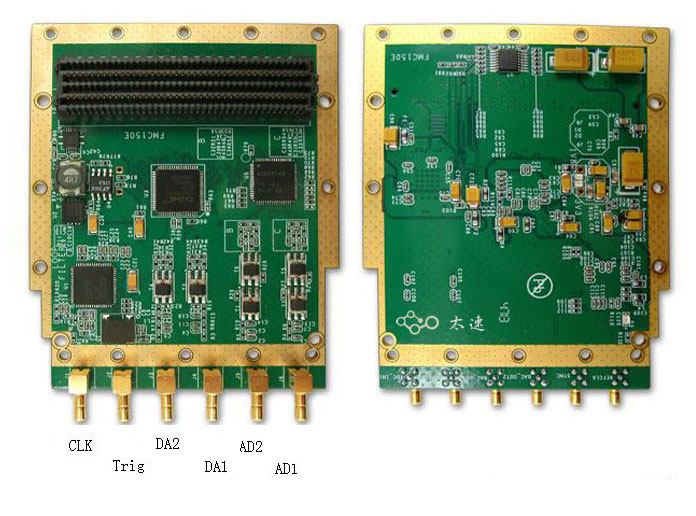

FMCJ465-2路 16bit 12.6GSPS FMC DA子卡

一、板卡概述:

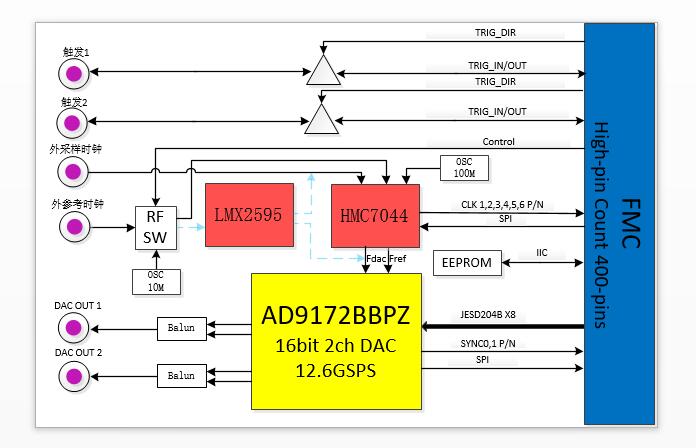

FMCJ465是一款轉(zhuǎn)換速率最高為12.6GSPS 的DAC 回放板,DAC位數(shù)16bit;板卡基于ADI的AD9172系列DAC設(shè)計(jì);板卡支持2路可配置的觸發(fā)輸出/觸發(fā)輸入;DAC的時(shí)鐘支持內(nèi)部參考時(shí)鐘、外部參考時(shí)鐘、外部采樣時(shí)鐘三種方式;并可提供一個(gè)接口同時(shí)支持外部采樣和外部參考時(shí)鐘的版本。

原理框圖

二、主要規(guī)格:

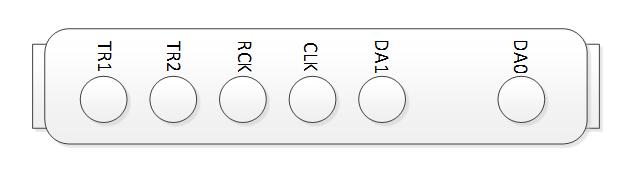

●6個(gè)SSMC的連接器,其中2個(gè)為模擬信號(hào)輸出1(DA 0)和2(DA 1);一個(gè)為外部采樣時(shí)鐘輸入(CLK);一個(gè)為外部參考時(shí)鐘輸入(RCK),2個(gè)為可由載板配置成輸入或者輸出的同步觸發(fā)信號(hào)(TR1和TR2)

●外部CLK也可同時(shí)兼容外采樣和外參考時(shí)鐘(需事先提出需求)

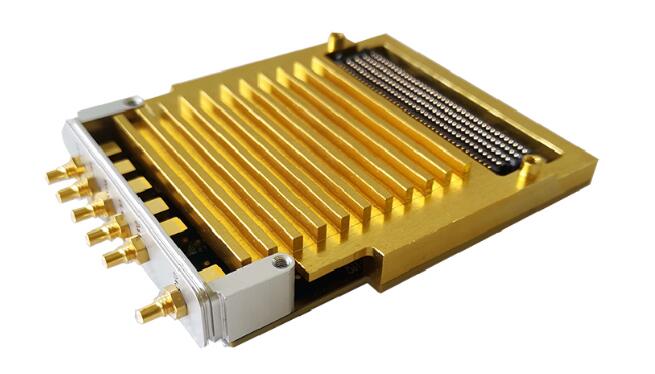

●適應(yīng)范圍:完全符合Vita57.1規(guī)范,包括結(jié)構(gòu)件,子卡尺寸,面板連接器,正反面器件的限高等,大大提供了子卡的通用性和適配性

●多種散熱方式:風(fēng)冷或?qū)Ю?/p>

●AC耦合輸入

●內(nèi)外部時(shí)鐘可靈活選擇

●HPC高引腳數(shù)連接器

●工作溫度:商業(yè)級(jí)0℃~+70℃,工業(yè)級(jí)-40℃~+85℃

三、板卡性能:

模擬輸出

●輸出耦合方式:交流耦合;

●輸出路數(shù):2路;

●輸出頻率:10MHz ~ 6000MHz;

●滿量程輸出電流:16~26mA(RSET=5KΩ),可編程;

●輸出阻抗:50 Ohm;

●連接器:SSMC;

數(shù)模轉(zhuǎn)換器DAC

●單芯片方案;

●分辨率:16bit;

●最大更新率:12.6GS/s

●DAC輸入兼容JESD204B子類1

時(shí)鐘

●支持內(nèi)參考或外部參考:10MHz,功率0~6dBm

●支持外部采樣時(shí)鐘最高:12.6GHz; 功率0~6dBm

●輸入阻抗:50 Ohm;

●耦合方式:交流耦合;

觸發(fā)

●外部觸發(fā)輸入:3.3V LVCMOS或LVTTL;

●觸發(fā)輸出:3.3V LVCMOS或LVTTL;

●最大頻率:200MHz;

●連接器:SSMC;

FMC 接口

HPC:ASP-134488-01;

●DP_C2M(0-7),LVDS 1.0V

●LA(00-33),LVDS或者LVCMOS或者LVTTL

●CLK(GBTCLK0,1;CLK0),LVDS 1.8V或2.5V

功耗

●+12V: <0.6?A;

●+3.3V: <0.1A;

●Vadj:<0.2A;

四、其他支持:

●提供Verilog bit文件

●JESD204B Core

五、前面板

|

前面板描述 序 信號(hào) 描述 1 DA 0 模擬信號(hào)輸出1 2 DA 1 模擬信號(hào)輸出 2 3 CLK 外部采樣時(shí)鐘(亦可作為外部采樣和參考時(shí)鐘,需事先提出需求) 4 RCK 外部參考時(shí)鐘 5 TR 1 觸發(fā)信號(hào)1,可配置成IN或OUT 6 TR 2 觸發(fā)信號(hào)2,可配置成IN或OUT 六、應(yīng)用(QT7227): ●軟件無(wú)線電 ●寬帶MIMO應(yīng)用 ●數(shù)字波束成形 ●(雷達(dá)/聲納)電子戰(zhàn) ●物理實(shí)驗(yàn) ●信號(hào)智能檢測(cè) ●航空航天和測(cè)試儀器 |

| FMCJ450-基于ADRV9009的雙收雙發(fā)射頻FMC子卡 |

一、板卡概述

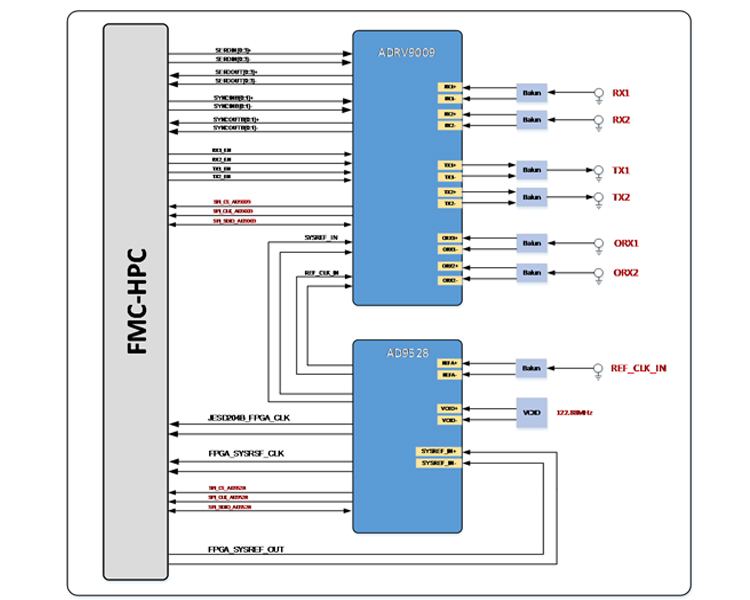

ADRV9009是一款高集成度射頻(RF)、捷變收發(fā)器,提供雙通道發(fā)射器和接收器、集成式頻率合成器以及數(shù)字信號(hào)處理功能。這款I(lǐng)C具備多樣化的高性能和低功耗組合,F(xiàn)MC子卡為2路輸入,2路輸出的射頻收發(fā)卡,配合FPGA工作滿足3G、4G和5G宏蜂窩時(shí)分雙工(TDD)基站應(yīng)用要求。

二、技術(shù)指標(biāo)

? 雙發(fā)射器

? 雙接收器

? 雙輸入共享觀察接收器

? 最大接收器帶寬:200MHz

? 最大可調(diào)諧發(fā)射器合成帶寬:450MHz

? 最大觀察接收器帶寬:450MHz

? 全集成的小數(shù)N射頻合成器

? 全集成的時(shí)鐘合成器

? 適用于射頻LO和基帶時(shí)鐘的多芯片相位同步

? JESD204B數(shù)據(jù)路徑接口

? 調(diào)諧范圍:75MHz至6000MHz

| No. | Items | Specifications | Remark | |

| Tx | 1 | Frequency | 100~6000MHz | |

| 2 | Bandwidth | Upto450MHz | Txreal-timebandwidth,tunable | |

| 3 | TransmissionPower | 17dBm | 100~6000MHz,CW | |

| 4 | EVM | <0.7%? | ||

| 5 | GainControlRange | 32dB | ||

| 6 | GainStep | 0.05dB | ||

| 7 | ACLR | @0dBmoutput | ||

| 8 | Spurious | 60dBc | ||

| 9 | SSBSuppression | 65dBc | ||

| 10 | LOSuppression | 70dBc | ||

| 11 | DACSampleRate(max) | 122.88MS/s | ||

| 12 | DACResolution | 14bits | ||

| Rx | 1 | Frequency | 100~6000MHz | |

| 2 | Bandwidth | 8to200MHz | real-timebandwidth,tunable | |

| 3 | Sensitivity: | -93dBm@20MHz | NoiseFigure<3db | |

| 4 | EVM | <1.5%? | @-30dBminput | |

| 5 | GainControlRange | |||

| 6 | GainStep | 0.5dB | ||

| 7 | RxAliasBandRejection | 80dB | Duetodigitalfilters | |

| 8 | NoiseFigure | <3db | MaximumRXgain | |

| 9 | IIP3(@typNF) | -25dBm | ||

| 10 | ADCResolution | 16bits | ||

| 11 | ADCWidebandSFDR | 78dBc | ||

| 1 | Voltage | 3.3V&12V | ||

| 2 | ON/OFFTIME | <6us? | TDDmodel | |

| 3 | DuplexingModel | TDD | ||

| 4 | PowerConsumptions | <6w |

三、產(chǎn)品應(yīng)用

3G/4G/5GTDD宏蜂窩基站;TDD有源天線系統(tǒng);大規(guī)模MIMO;電子戰(zhàn);便攜測(cè)試設(shè)備

四、軟件系統(tǒng)

提供支持ZYNQ的FMC接口測(cè)試程序源代碼

五、物理特性:

板卡遵循FMC規(guī)范,HPC,大小76.5X69mm。

六、供電要求:

FMC接口+12V供電

七、ADRV9009應(yīng)用軟件

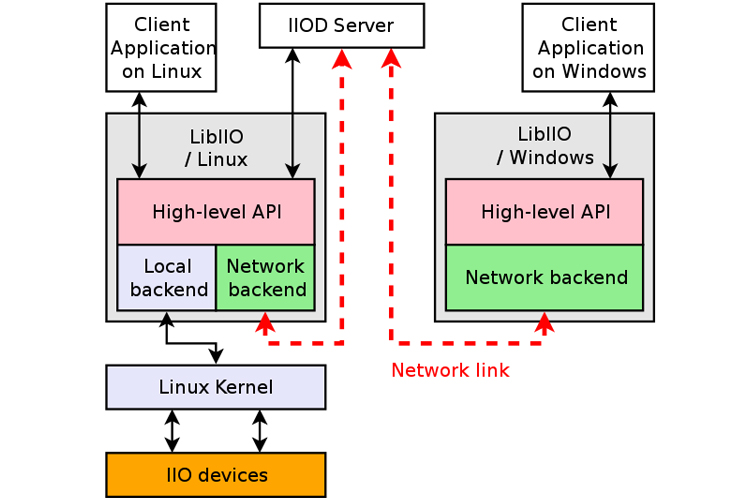

軟件架構(gòu):

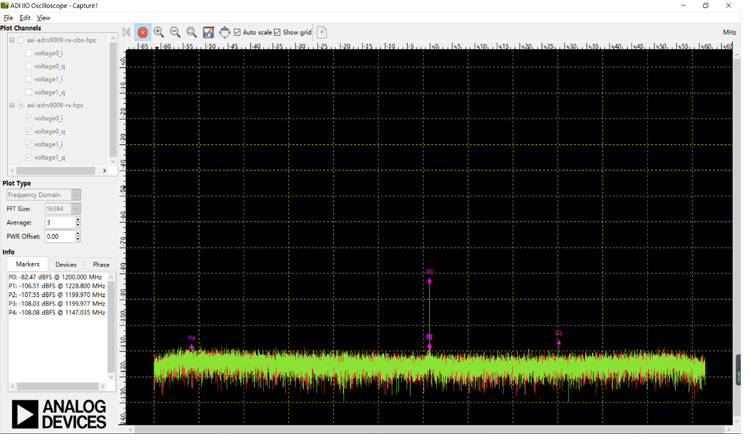

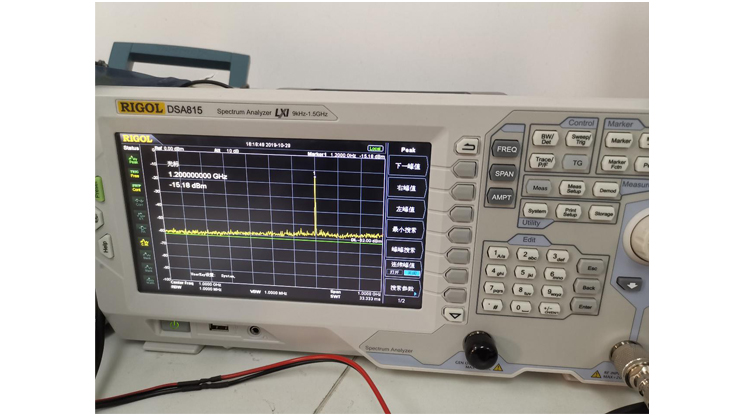

AD采集1.2G波形:

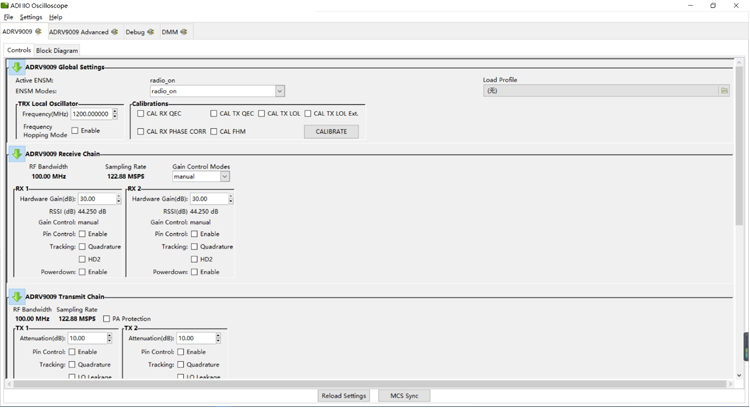

DA輸出設(shè)置1.2G及波形:

審核編輯黃宇

-

芯片

+關(guān)注

關(guān)注

455文章

50721瀏覽量

423167 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3424瀏覽量

105962 -

射頻

+關(guān)注

關(guān)注

104文章

5574瀏覽量

167695 -

FMC

+關(guān)注

關(guān)注

0文章

93瀏覽量

19676

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FMC子卡設(shè)計(jì)方案:202-基于TI DSP TMS320C6678、Xilinx K7 FPGA XC7K325T的高速數(shù)據(jù)處理核心板

TSW14J10 FMC-USB轉(zhuǎn)接卡用戶指南

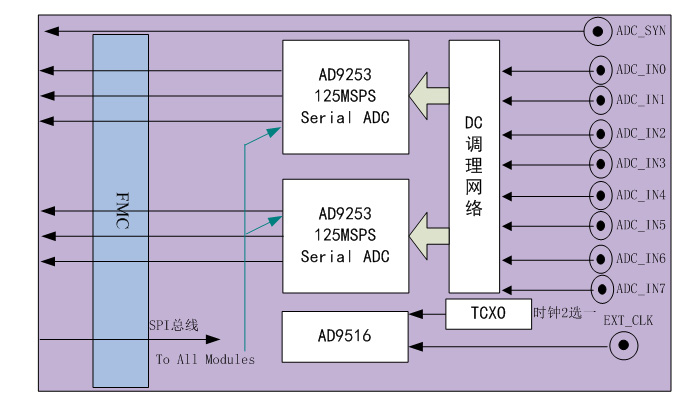

FMC子卡設(shè)計(jì)原理圖:FMC181-八路125Msps 14bit 直流耦合脈沖采集AD FMC子卡

子卡設(shè)計(jì)原理圖:232-基于FMC的2收2發(fā)TLK2711子卡

FMC子卡原理圖設(shè)計(jì):四通道1.25G/14bit數(shù)據(jù)采集

FMC子卡原理圖設(shè)計(jì): 4路 16bit 250M ADC+4路 16bit 2.8G DAC

射頻收發(fā)器就是基帶嗎

射頻收發(fā)器屬于什么類別

GD32 MCU 入門教程】GD32 MCU 常見外設(shè)介紹(12)FMC 模塊介紹

圖形圖像硬件加速器卡設(shè)計(jì)原理圖:270-VC709E 基于FMC接口的Virtex7 XC7VX690T PCIeX8 接口卡

調(diào)試STM32H750的FMC總線讀寫遇到的問題求解

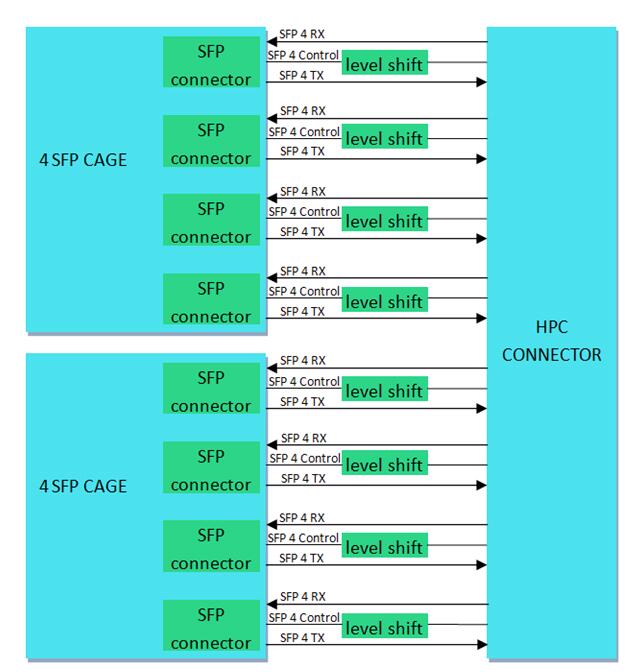

FMC擴(kuò)展子卡 6 路422,8 組LVDS,8 路GPIO

基于ADRV9002雙窄帶寬帶射頻收發(fā)器的FMC子卡FMC550介紹

基于ADRV9002雙窄帶寬帶射頻收發(fā)器的FMC子卡FMC550介紹

評(píng)論