隨著市場對嵌入式設備功能需求的提高,市面上出現了集成嵌入式處理器和單片機的主控方案,以兼顧性能和效率。

在實際應用中,嵌入式處理器和單片機之間需要進行大量且頻繁的數據交換,如果采用低速串行接口,則數據傳輸效率低,這將嚴重影響產品的性能;而如果采用高速并口,則占用管腳多,硬件成本將會增加。

為解決這一痛點,各大芯片公司陸續推出了兼具A核和M核的多核異構處理器,如NXP的i.MX8系列、瑞薩的RZ/G2L系列以及TI的AM62x系列等等。雖然這些處理器的品牌及性能有所不同,但多核通信原理基本一致,都是基于寄存器和中斷傳遞消息,基于共享內存傳輸數據。

以配電終端產品為例,A核負責通訊和顯示等人機交互任務,M核負責采樣和保護等對實時性要求較高的任務,雙核間交互模擬量、開關量和錄波文件等多種信息,A核+M核的方案既滿足了傳統采樣保護功能,又支持多種接口通信及新增容器等功能,符合國家電網現行配電標準。

通信過程整體架構說明

接下來小編將以NXP的i.MX8MP為例,借助飛凌OKMX8MP-C開發板分別從硬件層、驅動層、應用層介紹大致的通信實現流程以及實測效果。

1. 硬件層通信實現機制

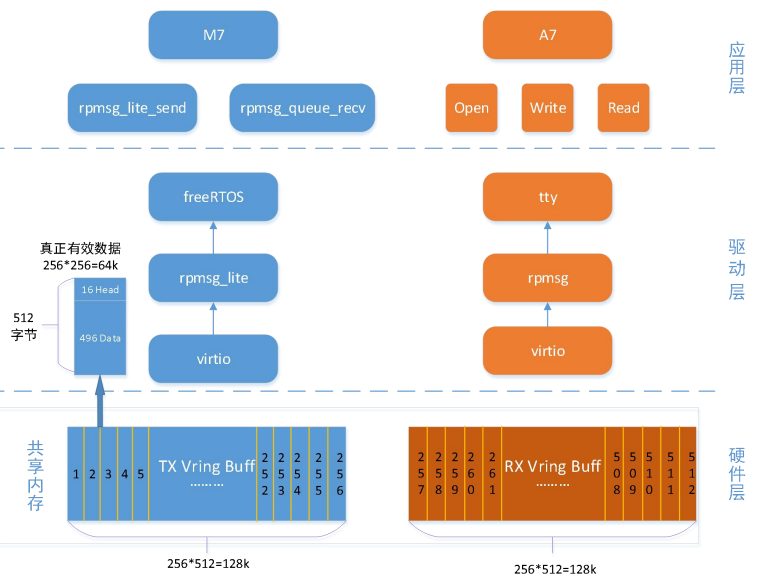

通過物理內存DDR分配,將硬件層分為了兩部分:TXVring Buffer(發送虛擬環狀緩沖區)和RXVring Buffer(接收虛擬環狀緩沖區);其中M核從TXVring區發送數據,從RXVring區讀取接收數據,A核反之。

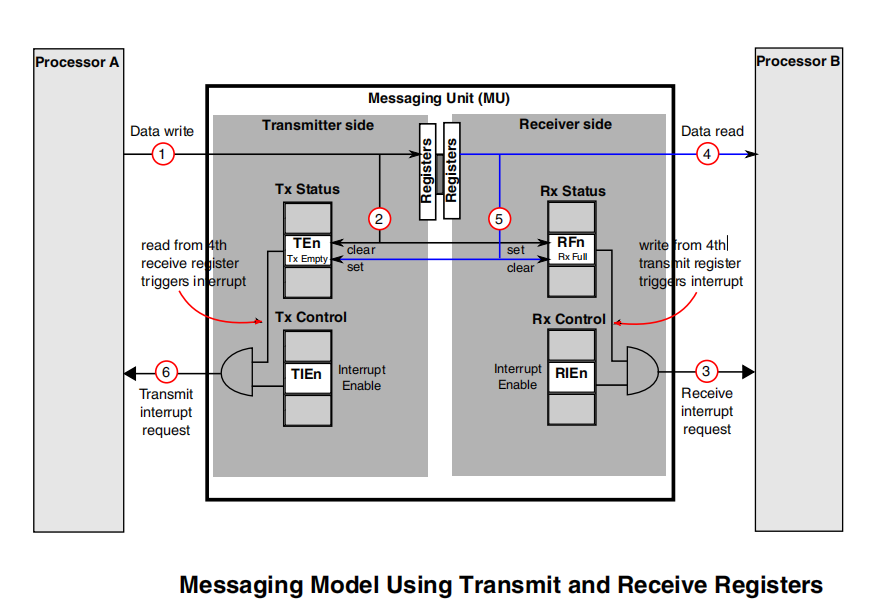

處理器支持消息傳遞單元(MessagingUnit,簡稱MU)功能模塊,通過MU傳遞消息進行通信和協調,芯片內的M7控制核和A53處理核通過通過寄存器中斷的方式傳遞命令,最多支持4組MU雙向傳遞消息,既可通過中斷告知對方數據傳遞的狀態,也可發送最多4字節數據,還可在低功耗模式下喚醒對方,是保證雙核通信實時性的重要手段。

寄存器輸入輸出通信模型

(1)CoreA寫入數據;

(2)MU將Tx 空位清0,Rx滿位置1;

(3)產生接收中斷請求,通知CoreB接收狀態寄存器中的接收器滿,可以讀取數據;

(4)CoreB響應中斷,讀取數據;

(5)CoreB讀完數據后,MU將Rx滿位清0,Tx空位置1;

(6)狀態寄存器向CoreA生成發送中斷請求,告知CoreB讀完數據,發送寄存器空。

通過以上步驟,就完成了1次從CoreA向CoreB 傳遞消息的過程,反之亦然。

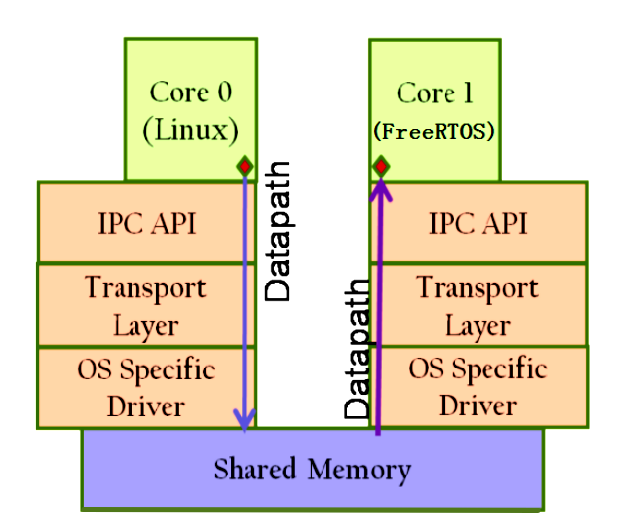

2. 驅動層Virtio下RPMsg通信實現

Virtio是通用的IO虛擬化模型,位于設備之上的抽象層,負責前后端之間的通知機制和控制流程,為異構多核間數據通信提供了層的實現。

RPMsg消息框架是Linux系統基于Virtio緩存隊列實現的主處理核和協處理核間進行消息通信的框架,當客戶端驅動需要發送消息時,RPMsg會把消息封裝成Virtio緩存并添加到緩存隊列中以完成消息的發送,當消息總線接收到協處理器送到的消息時也會合理地派送給客戶驅動程序進行處理。

在驅動層,對A核,Linux采用RPMsg框架+Virtio驅動模型,將RPMsg封裝為了tty文件供應用層調用;在M核,將Virtio移植,并使用簡化版的RPMsg,因為涉及到互斥鎖和信號量,最終使用FreeRTOS完成過程的封裝,流程框圖如下方所示。

主處理核與協處理核數據傳遞流程圖

(1)Core0向Core1發送數據,通過rpmsg_send函數將數據打包至Virtioavail鏈表區;

(2)在avail鏈表尋找共享內存中空閑緩存,將數據置于共享內存中;

(3)通過中斷通知Core1數據到來,共享內存由avail鏈表區變至used區;

(4)Core1收到中斷,觸發rpmsg的接收回調函數,從used區獲取數據所在的共享內存的物理地址,完成數據接收;

(5)通過中斷通知Core0數據接收完成,共享內存緩存由used區變為avail區,供下次傳輸使用。

3. 應用層雙核通信實現方式

在應用層,對A核可使用open、write和read函數對 /dev下設備文件進行調用;對M核,可使用rpmsg_lite_remote_init、rpmsg_lite_send和rpmsg_queue_recv函數進行調用,不做重點闡述。

4. 實際使用效果

通過程序實測,M核和A核可以批量傳輸大數據。同樣以配電產品為例——128點采樣的錄波文件大約為43K,若通過傳統的串行總線傳輸方式,需要數秒才可完成傳輸。

而使用i.MX8MP的雙核異構通信方案,只需要不到0.5秒即可傳輸完成,數據傳輸效率提升數十倍!同時還避免了串行總線易受EMC干擾的問題,提高了數據傳輸穩定性,簡化了應用編程,可滿足用戶快速開發的需求。

審核編輯:劉清

-

處理器

+關注

關注

68文章

19535瀏覽量

231859 -

單片機

+關注

關注

6050文章

44687瀏覽量

641186 -

MPU

+關注

關注

0文章

381瀏覽量

49162 -

嵌入式設備

+關注

關注

0文章

114瀏覽量

17139

原文標題:MPU進化,多核異構處理器有多強?A核與M核通信過程解析

文章出處:【微信號:Ithingedu,微信公眾號:安芯教育科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ARM多核處理器中不同的核是否可配置為純REE環境

核間通信(IPC)解決方案

MPU進化,多核異構處理器有多強?

A核+M核通信過程解析

【玩轉多核異構】處理器對共享外設和資源的調配方法

基于OKMX8MP-C板的多核異構處理器對外設和內存資源的使用方法

多核異構處理器對共享外設和資源的調配方法

MPU進化,多核異構處理器有多強?A核與M核通信過程解析

多核異構處理器中A核與M核通信過程的解析

多核異構處理器中A核與M核通信過程的解析

評論