作為一個FPGA開發(fā)者,之前對于DDR的使用,一直僅限于對廠商接口的使用,像無論是Xilinx還是Intel,在使用DDR時甚至IP配置參數(shù)都不需要了解,直接從老的工程里把IP拷貝過來就可以,而在使用DDR時只需要會使用AXI4/AvalonMm標(biāo)準(zhǔn)總線接口就行了。混了這么多年,本著夠用即可,再往下稍微了解些。

個人總結(jié),淺入淺出。讓我設(shè)計(jì)一個控制器那可是難為我了。

DDR——無非大的數(shù)組

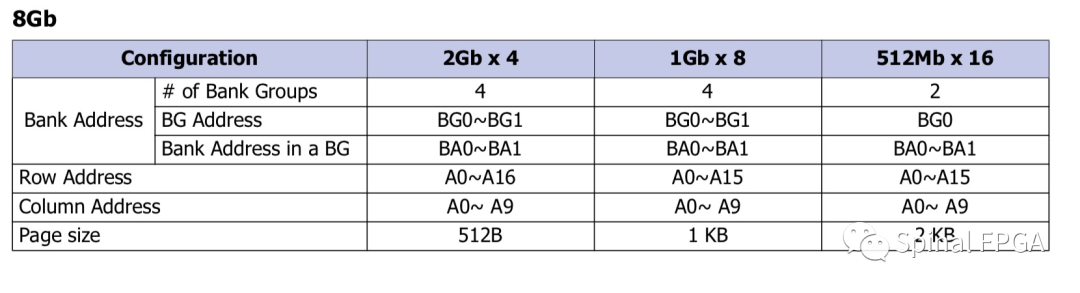

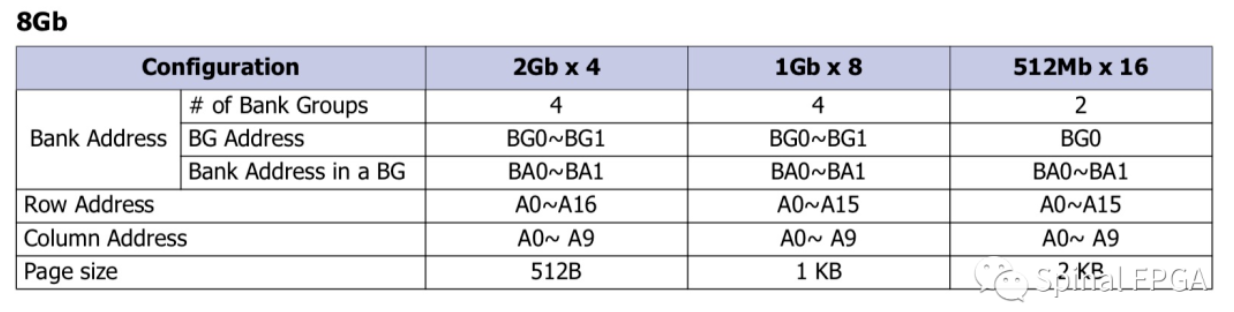

對于DDR的理解,最初簡單的以為無非一個大的數(shù)組,我會接口使用就OK了。不管各種概念天花亂墜,其總歸最終還是要?dú)w還到DDR顆粒芯片上來吧。我們常說DDR容量大小,某款DDR顆粒手冊上寫的規(guī)格容量如下圖所示:

看完之后一開始我只看懂了這個DDR顆粒手冊上寫的DDR容量是8Gb,剩下的我就能看懂的不多了~這也是為什么決定花點(diǎn)兒功夫好好了解下DDR的基礎(chǔ)知識。后面我們再來Review這張表。

這款芯片的512Mb x 16的引腳有這么幾個:

BG:1bit(GB0)

BA:2bit(BA0~BA1)

ROW:16 bit(A0~A15)

Column:10 bit(A0~A9)

DQ: 16 bit(DQ0~DQ1)

看完之后簡單總結(jié)一句話:對于DDR顆粒,Bank是讀寫地址動作的最小單元。像上面的512Mb x 16模式下,顆粒內(nèi)部有兩個Bank Group,每個Bank Group內(nèi)部有四個Bank,而每個Bank內(nèi)部的“存儲矩陣(二維數(shù)組)”對應(yīng)的行地址16 bit,列地址10 bit,每個存儲單元存儲16 bit數(shù)據(jù)。先不管對錯,這么算起來的話:

2**(1+2+10+16)*16=2**(33)=8Gb

容量是對上了,然而這看起來和上面的表格里的有些東西卻并對不上。

在上面的表格中,關(guān)于Configuration一行,512Mbx16意味著該DDR顆粒尋址能力為512Mb,每個地址對應(yīng)16 bit。由于對于DDR4列地址的低三bit并不參與譯碼,故尋址范圍大小的計(jì)算方式為:

2**(1(BG)+2(BA)+16(COL)+(10-3)COL)=2**26=512 Mb

如果你在Quartus進(jìn)行配置的話,也會發(fā)現(xiàn)給使用者的接口AvalonMm總線地址位寬也恰好為26 bit。

Page Size

按照上面文章里面的解釋,prefetch相當(dāng)于在DRAM Core與外面的IO建立了8多條通道,而Burst Fetch Length則是對于DDR顆粒可以在指定行,列地址后可連續(xù)讀取在該行指定列地址之后的多個列地址對應(yīng)的內(nèi)容。DDR4 prefetch和burst fetch length一般均為8,以上面的512Mbx16則意味著當(dāng)發(fā)起一個讀指令時,將會返回8x16=128 bit=16 Byte字節(jié)數(shù)據(jù)。

Page Size所定義的為一行ROW所對應(yīng)的數(shù)據(jù)量大小,如前所屬,參與尋址的列地址位寬為7,每個cell對應(yīng)16 bits,對應(yīng)burst fetch length為8,故Page Size的計(jì)算方式為:

2**7*16*8=2*14 bits=16 Kb=2 KB顆粒堆疊

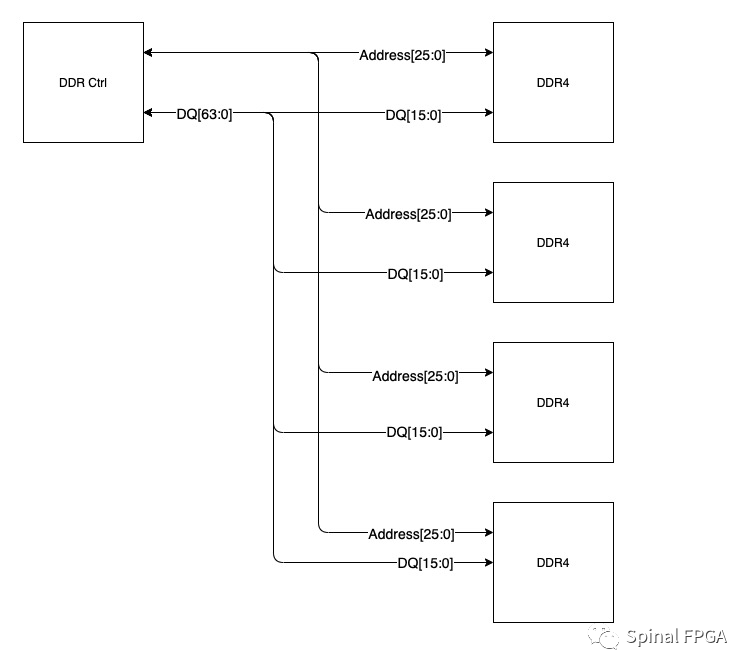

像上面的單個顆粒容量大小為8Gb。在FPGA使用里,DDR常見的配置有x64/x32這樣的模式。

如果在板卡上使用DDR顆粒,以x64的形式來組織板卡DDR架構(gòu),那就是這樣的結(jié)構(gòu)。

x64模式下,用到4片DDR,4片DDR的地址總線共用,數(shù)據(jù)總線則分成四份連接到四路DDR上。故此當(dāng)你在IP上發(fā)起64字節(jié)讀寫請求時每個DDR分別承擔(dān)了16 Byte字節(jié)的讀寫,恰好為一次Burst Length。

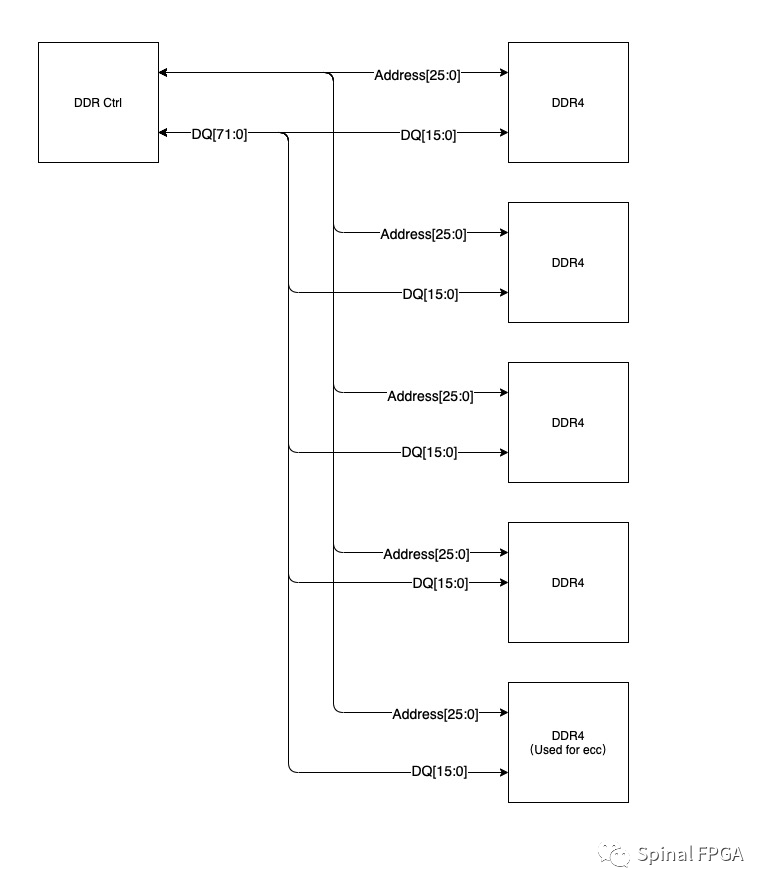

而當(dāng)你如果要是能ECC時,則需要5片DDR:

此時第五個DDR 8bit專門用于存儲ECC校驗(yàn)結(jié)果。在ECC模式下,x72bit模式下,若非64字節(jié)讀取/寫入,則需將數(shù)據(jù)先讀取出來再更新寫入,效率有一定的降低~

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603005 -

控制器

+關(guān)注

關(guān)注

112文章

16332瀏覽量

177812 -

DDR

+關(guān)注

關(guān)注

11文章

712瀏覽量

65318 -

ECC

+關(guān)注

關(guān)注

0文章

97瀏覽量

20556

原文標(biāo)題:FPGAer淺入淺出DDR——容量規(guī)格篇(一)

文章出處:【微信號:Spinal FPGA,微信公眾號:Spinal FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

淺入淺出DDR的容量規(guī)格

淺入淺出DDR的容量規(guī)格

評論