在為您的產(chǎn)品構(gòu)建ESD保護策略時,需要解決和測試多個因素,關(guān)鍵在于獲得平衡并測試其效率。

電子系統(tǒng)和組件對ESD越來越敏感。IC和半導(dǎo)體工藝的小型化、密閉空間內(nèi)的多種電源要求、數(shù)據(jù)速率的提高、單個SoC上功能的更大集成、數(shù)據(jù)和電源接口的組合——所有這些都會導(dǎo)致更高的瞬態(tài)電壓損壞風(fēng)險。每個單獨的因素對ESD和浪涌保護都有不同的要求,并且某些應(yīng)用是所有因素的組合,這使得ESD保護選擇更具挑戰(zhàn)性。

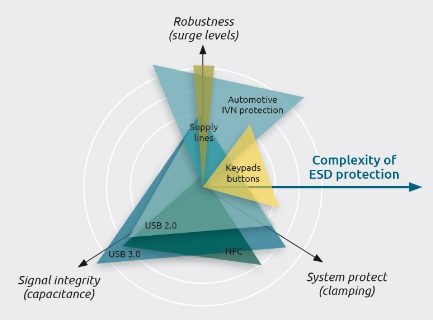

在Nexperia,當(dāng)我們考慮什么是有效的ESD保護器件時,我們會考慮三個關(guān)鍵參數(shù) - 我們稱之為ESD保護的三大支柱:

高魯棒性 - 保護器件免受 ESD 和浪涌脈沖的影響

低鉗位電壓 - 為了保護 SoC,與低動態(tài)電阻齊頭并進,以確保在浪涌電流增加時箝位電壓不會上升

三個關(guān)鍵參數(shù)與不同應(yīng)用領(lǐng)域的關(guān)系

如圖所示,這些屬性是相互依賴的,因此改進一個屬性可能會對其他屬性產(chǎn)生不利影響。對于某些應(yīng)用,這不是問題,因為它們只需要在一個或兩個屬性中具有良好的性能。然而,隨著通過接換數(shù)據(jù)的高速率,當(dāng)今的互聯(lián)世界對保護設(shè)備的需求越來越大,以便在所有三個領(lǐng)域提供最佳性能。在這些情況下,有效的解決方案必須平衡ESD保護的所有三大支柱。

Nexperia對此的回答是TrEOS保護,它實現(xiàn)了這種平衡,為系統(tǒng)提供了最先進的ESD保護。為了確保解決方案確實對瞬態(tài)和靜電放電有效,我們還超越了理論,在現(xiàn)實條件下測試我們的解決方案。

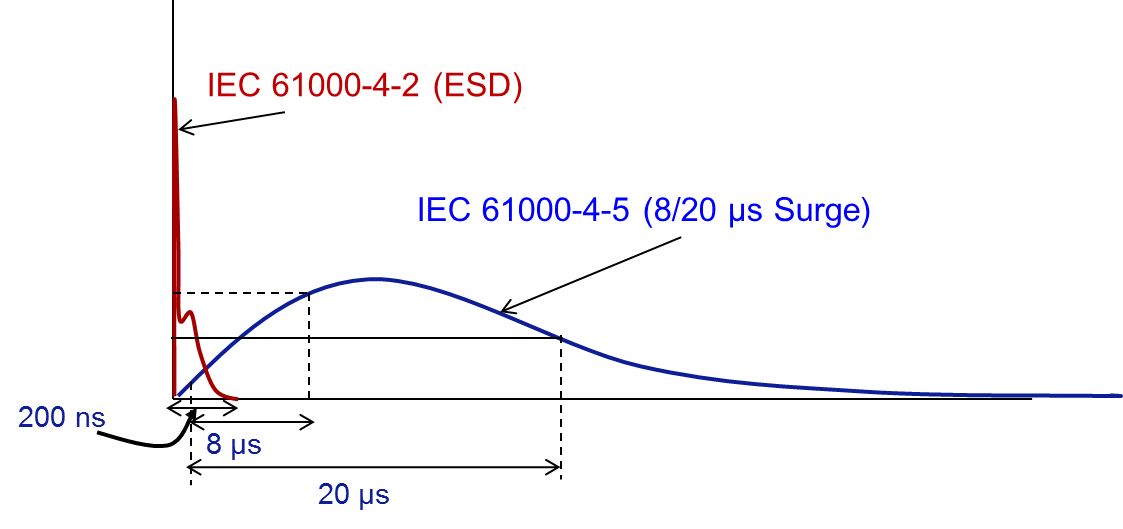

TLP / VF-TLP 測試

大多數(shù)靜電放電不會被用戶注意到,但會嚴(yán)重損壞敏感的電子設(shè)備。國際公認(rèn)的標(biāo)準(zhǔn)測試方法和技術(shù)(IEC61000-4-2 / IEC61000-4-5)提供了良好的洞察力,但結(jié)果可能因所使用的測試設(shè)備而異。因此,隨著當(dāng)今高速接口數(shù)據(jù)速率的提高,正在使用兩種相對較新的測試來確保滿足性能要求:TLP(傳輸線脈沖)和VF-TLP(超快速TLP)測試是廣泛采用的表征完整接口和ESD保護組件的方法。

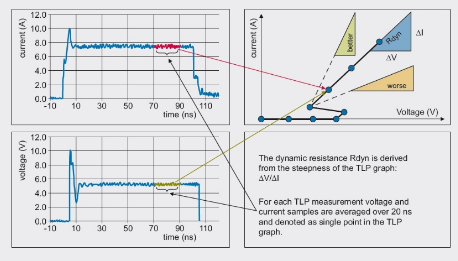

TLP 測量器件在脈沖寬度較短(通常為 100 納秒持續(xù)時間)的應(yīng)力下的性能屬性,快速上升和下降時間為 1 納秒或 600 皮秒。TLP脈沖大致相當(dāng)于一個完整的ESD脈沖的能量。相比之下,VF-TLP使用更短的測試脈沖,上升和下降時間低至100 ps。這為確定ESD保護器件的開關(guān)速度提供了良好的指示,并且可以擴展到檢查1圣和 2德·分別達到峰值。

使用測試產(chǎn)生的測量曲線有助于確定哪種保護裝置適合安全可靠地保護產(chǎn)品。在我們的ESD測試實驗室,我們不僅檢查我們自己產(chǎn)品的性能,而且還對完整的電路板進行TLP測試。根據(jù)我們的經(jīng)驗,這是找到保護整個系統(tǒng)平衡的最佳方法,因為瞬態(tài)電壓可以利用任何弱點。我們?nèi)娴恼鎸崪y試帶來了更深入的見解和更安全的結(jié)果。

從 TLP 測試事件導(dǎo)出的 TLP 曲線

為您的系統(tǒng)提供正確的平衡

了解核心參數(shù)和標(biāo)準(zhǔn)測試方法只是為您的系統(tǒng)選擇正確的ESD保護策略的第一步。選擇合適的保護解決方案還需要了解需要保護哪些接口,并且應(yīng)考慮整個系統(tǒng)的設(shè)計及其應(yīng)用。

審核編輯:郭婷

-

ESD

+關(guān)注

關(guān)注

48文章

2029瀏覽量

172929 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27286瀏覽量

218069 -

soc

+關(guān)注

關(guān)注

38文章

4161瀏覽量

218160

發(fā)布評論請先 登錄

相關(guān)推薦

ESD和浪涌保護技術(shù)應(yīng)用

超低負載電容高浪涌ESD保護TVS陣列

RS-422/RS-485接口的ESD/浪涌保護

如何保護隔離總線節(jié)點免受ESD/EFT和瞬間浪涌的影響?

ESD保護裝置·對策元件基礎(chǔ)知識——ESD(靜電放電?浪涌)保護裝置?對策元件是什么?

ESD保護裝置·對策元件基礎(chǔ)知識——ESD(靜電放電?浪涌)保護裝置?對策元件的種類

關(guān)于ESD204對HDMI接口的浪涌保護

ESDS302、ESDS304數(shù)據(jù)線路浪涌和ESD保護器件數(shù)據(jù)表

有效的ESD和浪涌保護 - 平衡問題

有效的ESD和浪涌保護 - 平衡問題

評論