RAL(Register Abstract Layer,寄存器抽象層),通常也叫寄存器模型,顧名思義就是對(duì)寄存器這個(gè)部件的建模。本文要介紹的內(nèi)容,包括對(duì)UVM寄存器模型的概述,如何構(gòu)建寄存器模型,以及如何將寄存器模型集成到驗(yàn)證環(huán)境中。篇幅原因,將在下一篇文章再給出寄存器模型的操作圖鑒(前后門(mén)訪問(wèn)API),以及寄存器覆蓋率的收集。

01 寄存器模型概述

為什么要對(duì)寄存器建模,可能是初學(xué)者問(wèn)得較多的問(wèn)題。簡(jiǎn)單地說(shuō),寄存器建模要做的事情,就是在軟件的世界里面,復(fù)刻RTL中的寄存器。既然是面向軟件世界做的事情,自然就是為軟件所用,要么方便軟件觀測(cè),要么方便軟件使用。

這里的軟件,指的是整個(gè)驗(yàn)證環(huán)境所構(gòu)造出來(lái)的面向?qū)ο蟮氖澜纭S辛思拇嫫髂P停浖澜缰械膮⒖寄P停╮eference model)可以很方便的獲取到當(dāng)前RTL的功能配置和狀態(tài),我們也可以很方便的收集到對(duì)寄存器各個(gè)域段甚至位的測(cè)試覆蓋情況等等。

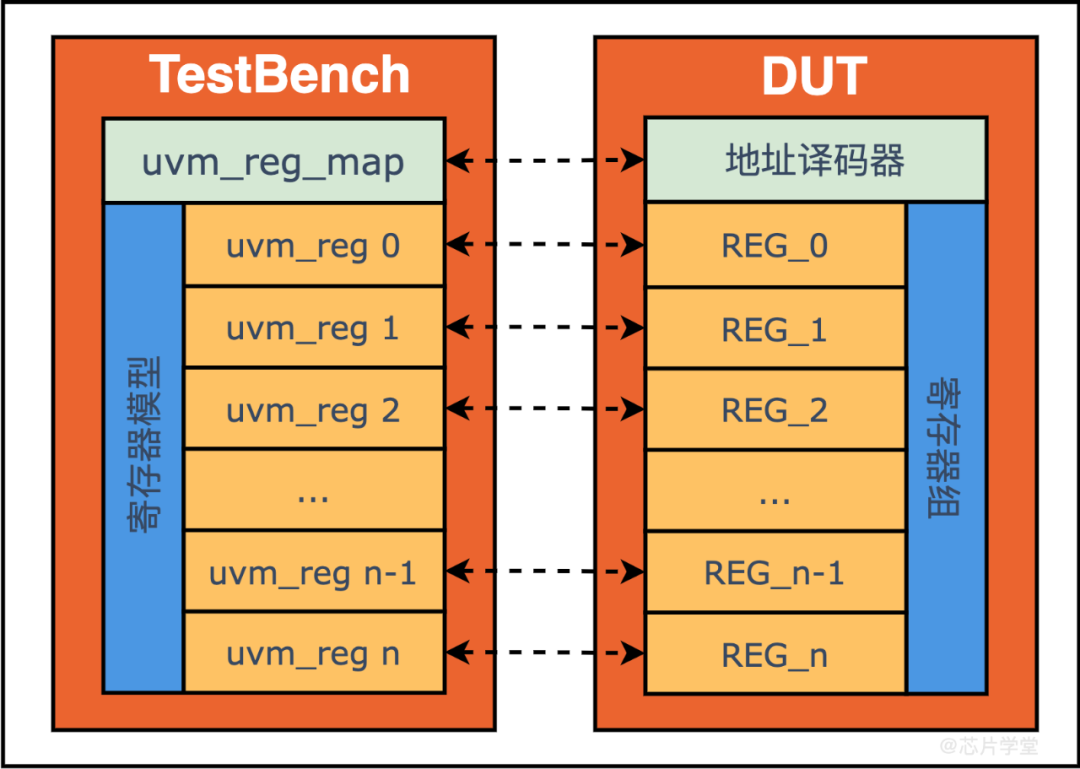

要達(dá)成這一目標(biāo),就需要考慮兩個(gè)基本的問(wèn)題:如何對(duì)寄存器進(jìn)行建模,以及建立怎樣的機(jī)制才可以讓寄存器模型是“實(shí)時(shí)”復(fù)刻RTL寄存器的(上圖中的虛線箭頭)。這也是本文后面兩個(gè)小節(jié)要介紹的內(nèi)容。

02 構(gòu)造寄存器模型

寄存器模型的框架實(shí)際上跟RTL中的寄存器組沒(méi)有什么兩樣。寄存器組中有的,寄存器模型也應(yīng)該要有,頂多是多了一些抽象。基于這個(gè)想法,構(gòu)造寄存器模型的工作,便可以從硬件寄存器組的設(shè)計(jì),一一映射為對(duì)應(yīng)的數(shù)據(jù)結(jié)構(gòu)。

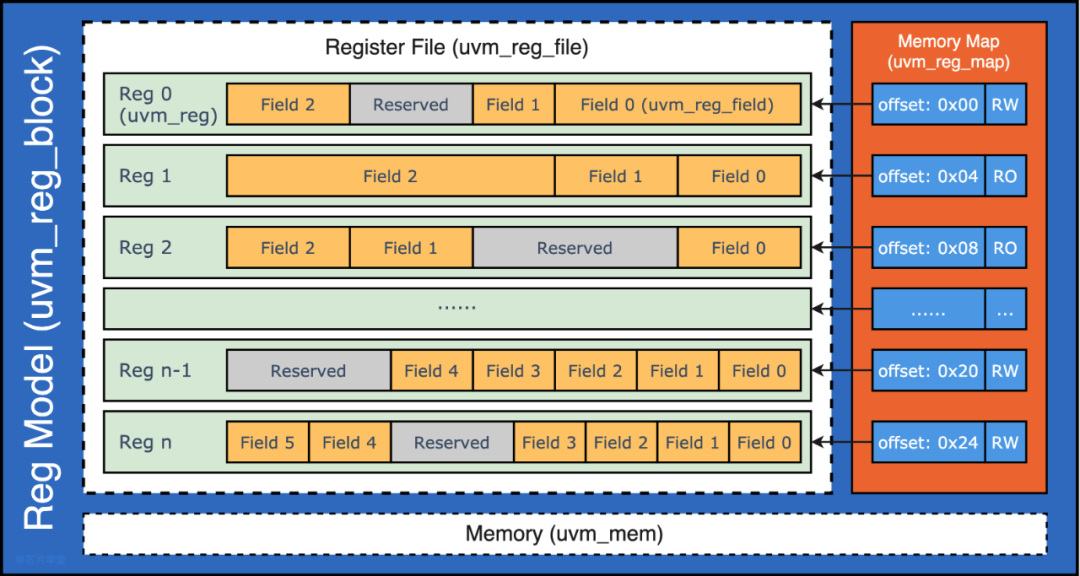

寄存器最小的功能單元是域段(field)。一個(gè)寄存器要切分成多少個(gè)域段、每個(gè)域段的位寬、默認(rèn)值、讀寫(xiě)屬性以及分別用于什么功能的控制或狀態(tài)的指示,是根據(jù)功能規(guī)范來(lái)定義的。對(duì)域段的建模,UVM類(lèi)庫(kù)提供的類(lèi)型叫uvm_reg_field。

寄存器是可作為單個(gè)實(shí)體被訪問(wèn)的多個(gè)域段的集合,它可以被映射到一個(gè)或者多個(gè)地址上(memory-mapped)被訪問(wèn)。對(duì)寄存器的建模,UVM提供的類(lèi)型叫uvm_reg。為了提供后門(mén)訪問(wèn)(backdoor access),uvm_reg還增加了成員來(lái)表示其對(duì)應(yīng)的硬件寄存器在RTL中的層次路徑。

寄存器訪問(wèn)譯碼表,或者叫memory map,是寄存器接口從訪問(wèn)地址到使能對(duì)應(yīng)寄存器所需要的查找表。這張表中指定了每個(gè)寄存器的偏移地址(offset)、訪問(wèn)屬性、大小端、對(duì)應(yīng)的總線等配置。對(duì)memory map的建模,UVM提供的類(lèi)型叫uvm_reg_map。

多個(gè)寄存器及其訪問(wèn)譯碼表最終構(gòu)成寄存器組。在同個(gè)數(shù)字系統(tǒng)的不同總線視角下,寄存器組可以映射到不同的基地址(base)。因此,一個(gè)寄存器組除了可以包含多個(gè)寄存器,還可以有多個(gè)譯碼表。UVM針對(duì)寄存器組的建模提供的類(lèi)型叫uvm_reg_block。為了便于集中管理,uvm_reg_block還可以包含其他子uvm_reg_block。

在同一類(lèi)族中,UVM還提供了uvm_mem類(lèi),用于對(duì)連續(xù)地址存儲(chǔ)空間的建模。uvm_mem對(duì)象也可以被集成到uvm_reg_block中,并通過(guò)uvm_reg_map做地址映射,

此外,UVM還提供了uvm_reg_file類(lèi)。這個(gè)類(lèi)更像是一個(gè)對(duì)象容器,可以用來(lái)裝載多個(gè)寄存器(uvm_reg)和其他uvm_reg_file,以便對(duì)相同規(guī)格的寄存器進(jìn)行多次例化。

03 集成到驗(yàn)證環(huán)境

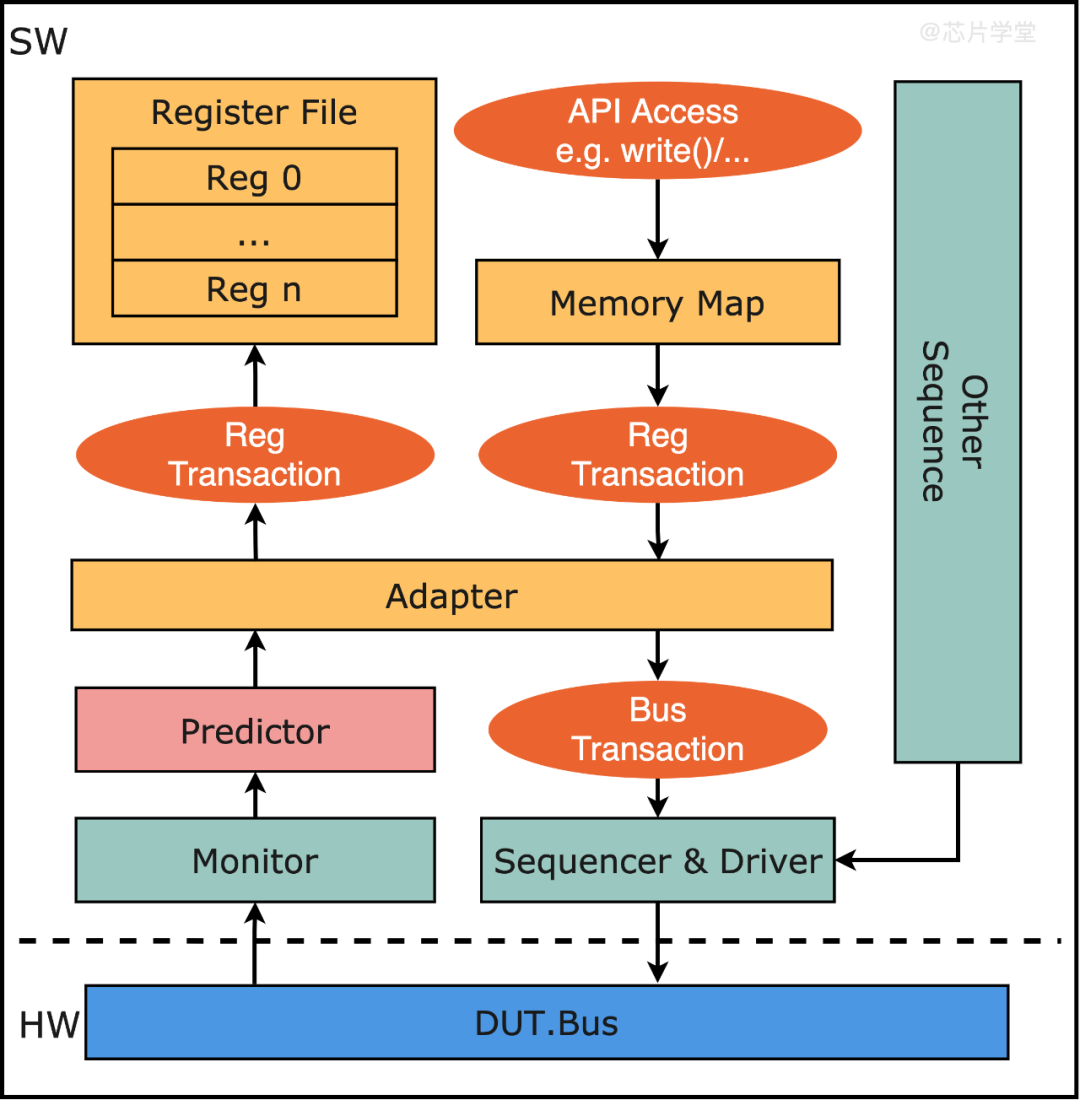

如果只是簡(jiǎn)單把寄存器模型集成到驗(yàn)證環(huán)境,那么只要例化寄存器模型就可以了。現(xiàn)在主要的問(wèn)題是,建立怎樣的機(jī)制才可以讓寄存器模型“實(shí)時(shí)”復(fù)刻RTL寄存器的值。為了解決這個(gè)問(wèn)題,UVM引入Prediction機(jī)制,用到了兩個(gè)新的組件:Adapter和Predictor。

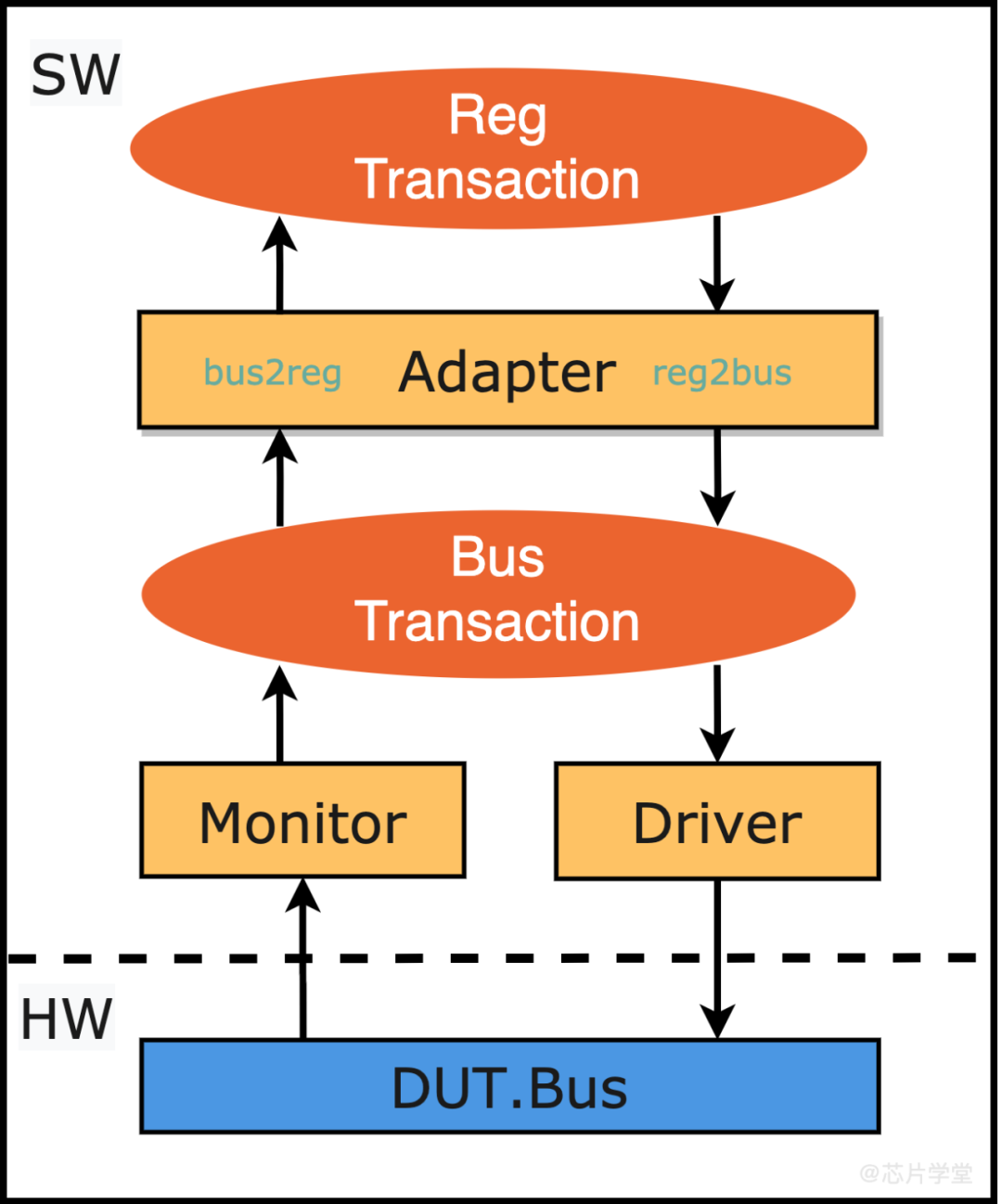

Adapter,可以翻譯為適配器,它的作用是寄存器訪問(wèn)事務(wù)和總線事務(wù)的相互轉(zhuǎn)換。寄存器訪問(wèn)事務(wù)對(duì)數(shù)據(jù)的封裝格式相對(duì)固定,一般包含讀寫(xiě)類(lèi)型、地址、數(shù)據(jù)和字節(jié)掩碼。而總線事務(wù)則根據(jù)不同的總線協(xié)議會(huì)有所不同。因此,Adapter扮演了中間做事務(wù)轉(zhuǎn)換的角色,其主要實(shí)現(xiàn)的函數(shù)為reg2bus和bus2reg。

Predictor,是保持寄存器模型“實(shí)時(shí)”復(fù)刻RTL寄存器值的關(guān)鍵組件。Predictor翻譯過(guò)來(lái)叫預(yù)測(cè)器,可能反而不是很好理解,對(duì)其功能比較好的描述我覺(jué)得應(yīng)該是“monitor and update the RAL Model”。根據(jù)是否使用外部predictor,有兩種應(yīng)用方式:Implicit Prediction和Explicit Prediction。

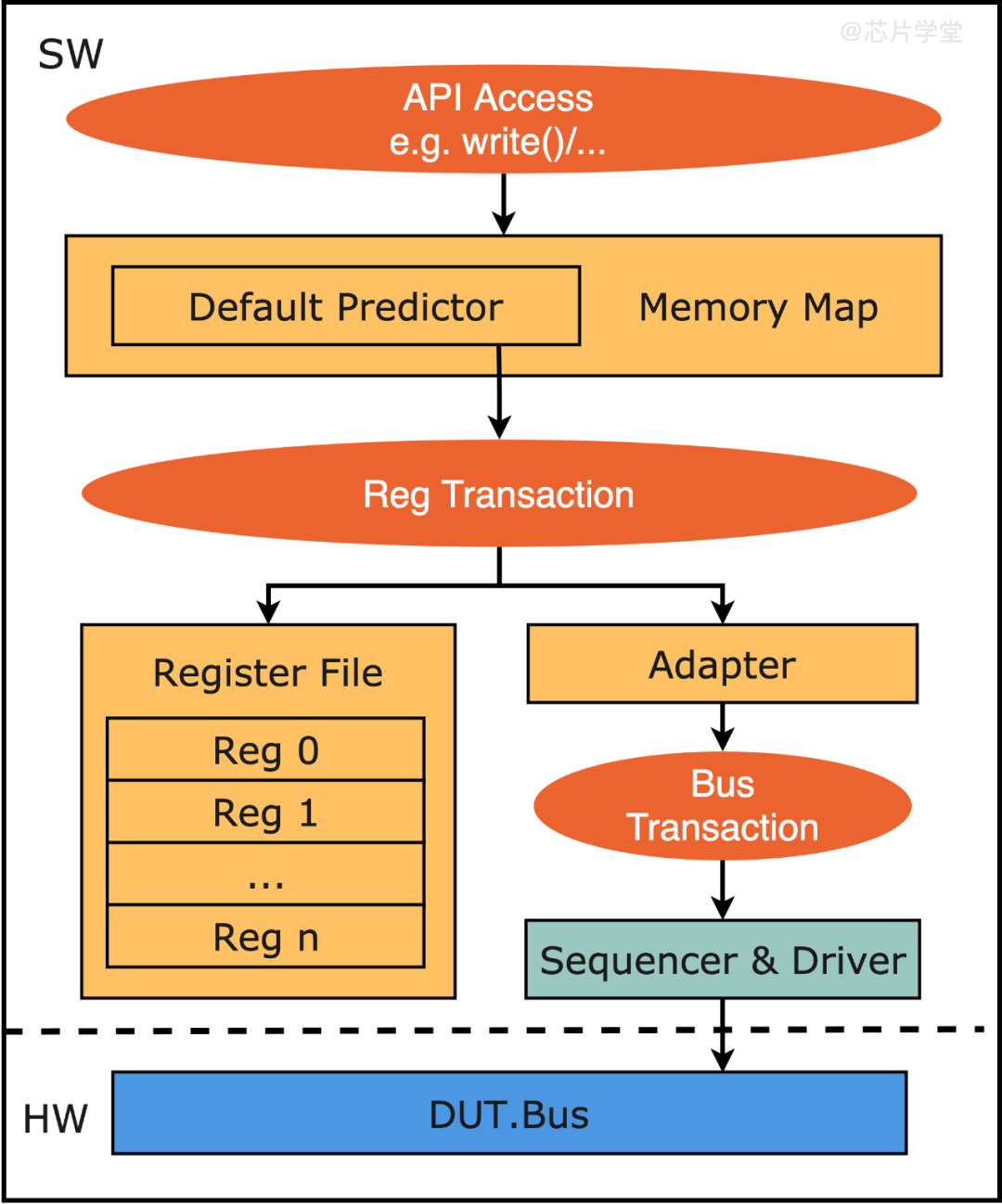

隱式預(yù)測(cè)(Implicit Prediction):用戶(hù)使用寄存器模型中memory map默認(rèn)的predictor,當(dāng)開(kāi)啟其預(yù)測(cè)功能之后,如果用戶(hù)在測(cè)試用例中通過(guò)寄存器模型的API(下篇文章會(huì)介紹都有哪些API)去發(fā)起硬件寄存器訪問(wèn)操作,該操作會(huì)自動(dòng)被predictor捕捉,并在該操作完成之后自動(dòng)同步到寄存器模型的寄存器中。下圖為了方便展示,將原本同屬于寄存器模型中的memory map、registers和adapter分開(kāi)畫(huà)了。

顯式預(yù)測(cè)(Explicit Prediction):用戶(hù)基于UVM提供的基類(lèi)uvm_reg_predictor實(shí)現(xiàn)preditor,并將monitor的總線事務(wù)傳遞給該predictor,同時(shí)將其關(guān)聯(lián)到寄存器模型的memory map和對(duì)應(yīng)總線事務(wù)的adapter適配器。工作邏輯是這樣的:該predictor相當(dāng)于可以根據(jù)memory map監(jiān)測(cè)總線上的寄存器訪問(wèn)行為,并將該行為通過(guò)adapter轉(zhuǎn)換成寄存器事務(wù),最終用于更新寄存器模型。

Explicit Prediction相對(duì)于Implicit Prediction,除了監(jiān)視通過(guò)寄存器模型API對(duì)寄存器的訪問(wèn)操作,還可以覆蓋到其他測(cè)試序列(sequence)通過(guò)總線對(duì)寄存器的直接訪問(wèn),這一點(diǎn)會(huì)使它更加通用。

相應(yīng)的代碼示例,也將在下一篇UVM系列文章中提供,歡迎關(guān)注。

參考資料

[1] Accellera Systems Initiative. "Universal Verification Methodology (UVM) 1.2 Class Reference" (2014).

-

寄存器

+關(guān)注

關(guān)注

31文章

5402瀏覽量

122917 -

API

+關(guān)注

關(guān)注

2文章

1556瀏覽量

63350 -

UVM

+關(guān)注

關(guān)注

0文章

182瀏覽量

19380

發(fā)布評(píng)論請(qǐng)先 登錄

如何構(gòu)建UVM寄存器模型并將寄存器模型集成到驗(yàn)證環(huán)境中

寄存器與移位寄存器

數(shù)據(jù)寄存器,數(shù)據(jù)寄存器是什么意思

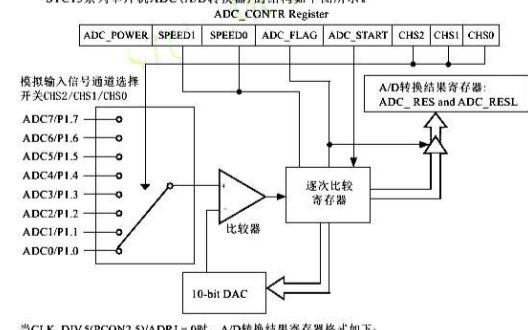

AD轉(zhuǎn)換寄存器設(shè)置

簡(jiǎn)化UVM寄存器模型的使用教程

簡(jiǎn)化UVM寄存器模型的使用

寄存器模型Register Model學(xué)習(xí)筆記

評(píng)論