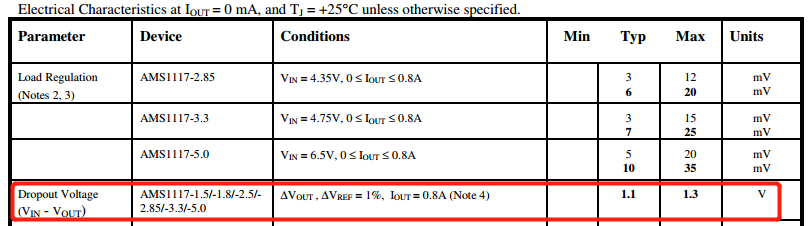

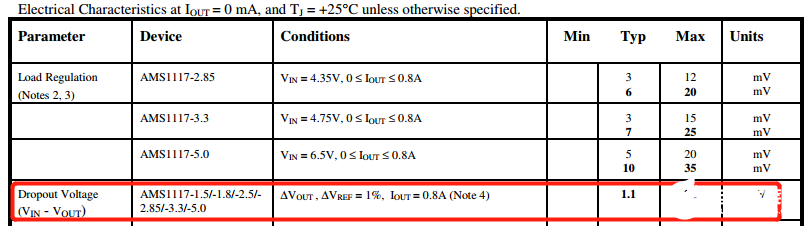

在LDO應用中,會有一個輸入輸出壓差范圍的概念 ,如AMS1117,壓差Dropout Voltage的典型值為1.1V,即:輸入至少比輸出高1.1V的壓降才能支持所需要的輸出。

在之前寫過的一篇文章《LDO與DC-DC 的入門理解》中,我們可以了解到LDO是靠內部電路分壓達到降壓輸出,而DC-DC則是通過“斷續的供給”達到降壓輸出。那么,DC-DC降壓電路輸入和輸出是否需要壓差呢?思考一個場景:某款Buck芯片自身工作電壓范圍為2.7-5.5V,現需要該芯片輸出3.3V/2A。當正常輸入5V時,該芯片可滿載輸出3.3V,當輸入電壓只有3.5V時,該芯片是否還能正常輸出3.3V/2A呢?

該問題本質其實是DC-DC降壓電路中,在輸入輸出規格內,芯片占空比是否受限、導通損耗的問題 。理論上,但芯片的開關周期達到100%時,DC-DC其實是一個“直通”狀態,即輸出電壓等于輸入電壓,當然,真實的應用中,芯片的占空比不會達到完整的100%,而且由于芯片里集成或外置的MOSFET的導通內阻以及輸出電感上Rdc,實際輸出電壓與輸入電壓之間會有一個壓差。

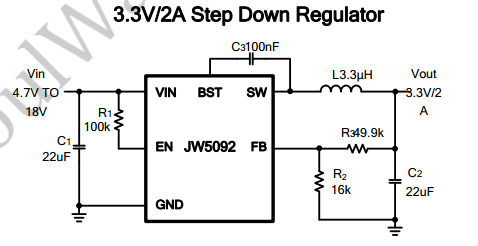

以JW5092為例,輸入4.7V時,可輸出3.3V/2A,但當輸入為4.0V的時候,是否還能滿載輸出?

首先,根據能量守恒,我們可知(Vin-Vout)ton=Vouttoff,由此

Vout = Vin * D,D為開關周期中,“開”的占空比。

考慮,MOS管導通內阻Rds、電感內阻RL,可得:

Vout = Vin * D- Iout x (Rds(ON) + RL)

查看規格書——

當Vin = 4V時,若輸出2A,暫時忽略電感選型上的內阻差異,則:

由此可知,此時該當輸入為4.0V的時候,JW5092無法滿載輸出3.3V/2A

所以DC-DC降壓電路中,實際輸出電壓要等于輸入電壓減去Buck芯片里集成或外置的MOSFET的Rds(on)以及輸出電感的Rdc上產生的壓降,包括由于占空比受限導致的無法滿載輸出。帶載越重,輸出電壓越低。當你的輸入輸出壓差范圍很小,但仍然需要滿載輸出時,請考慮號稱可達100%占空比的芯片!

-

ldo

+關注

關注

35文章

1940瀏覽量

153311 -

DC-DC

+關注

關注

30文章

1943瀏覽量

81603 -

降壓芯片

+關注

關注

1文章

159瀏覽量

16522

發布評論請先 登錄

相關推薦

請求高手推薦幾款 DC/DC 降壓芯片

30V轉5V, 30V轉3.3V, 30V轉3V芯片,DC-DC降壓和LDO集合

一款寬電壓范圍降壓型 DC-DC 電源管理芯片

使用DC-DC降壓芯片來持續穩壓12V轉5V

LDO和DC-DC有什么不同?

DC-DC降壓芯片120V轉12V5A大功率SL3038電源芯片

DC-DC降壓芯片(LCD TV驅動方案/車載AV驅動方案)

DC-DC降壓芯片 (LCD TV 驅動方案/車載AV 驅動方案)

LDO與DC-DC

基于芯鼎盛TX4130設計的POE電源DC-DC降壓芯片說明

DC-DC降壓芯片的輸入輸出壓差范圍的要求

DC-DC降壓芯片的輸入輸出壓差范圍的要求

評論