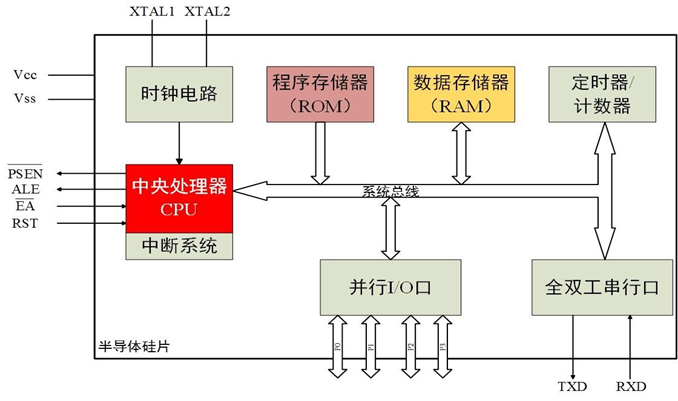

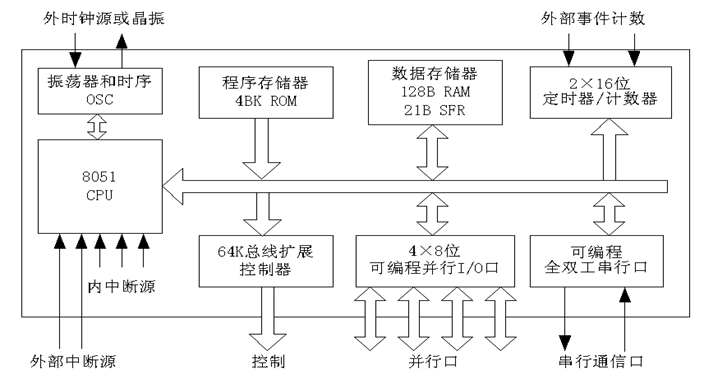

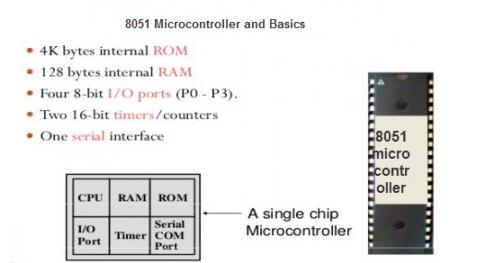

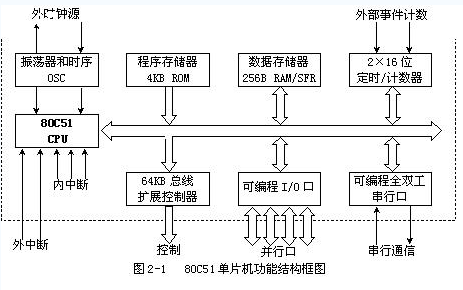

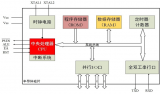

單片機的基本結構包括中央處理器(CPU) 、存儲器、定時/計數器、輸入輸出接口、中斷控制系統和時鐘電路六部分。

一、基本組成

中央處理器(CPU)

包括運算器和控制器兩部分,是單片機的核心。運算器可用于各種運算,控制器用于控制單片機各部分協調工作。

存儲器

用于存放程序和原始數據。

時鐘電路

時鐘電路產生單片機運行的控制信號,控制單片機嚴格按時序執行指令。

定時/計數器:實現定時或計數功能。

輸入輸出接口(I/O)實現單片與其他設備之間的數據傳送。

中斷控制系統: 用于響應中斷源的中斷請求;

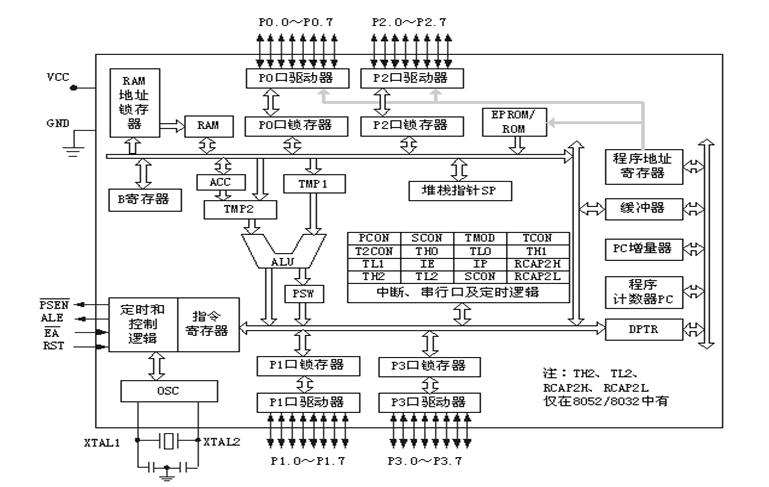

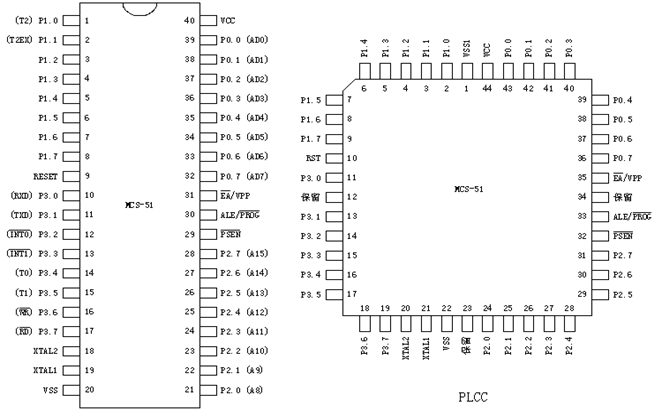

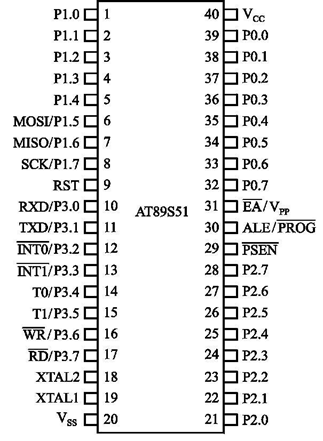

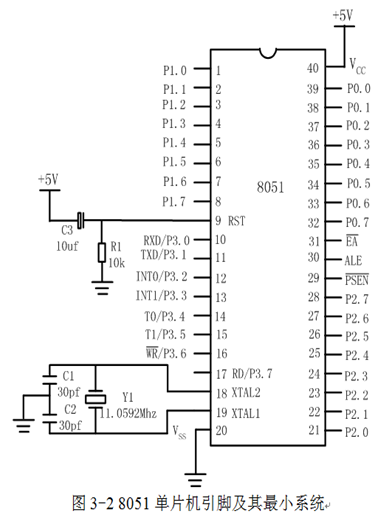

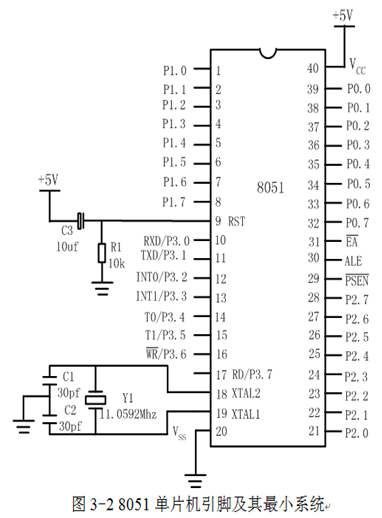

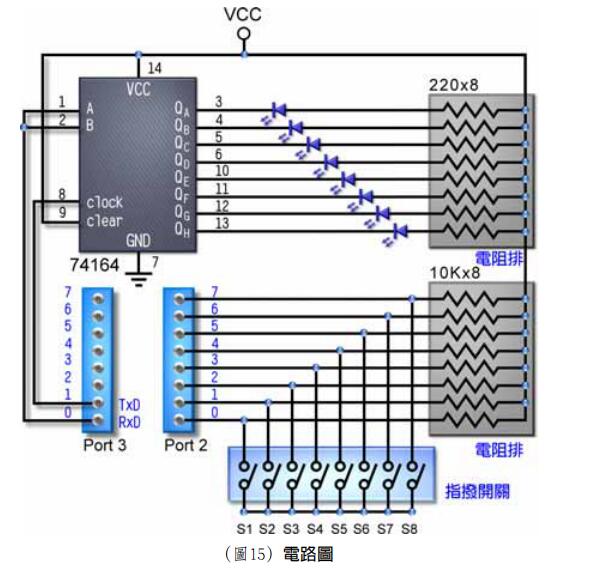

二、單片機引腳

雙列直插式封裝(DIP,Dual Inline Package)

方形封裝(PLCC,Plastic Leaded Chip Carrier)

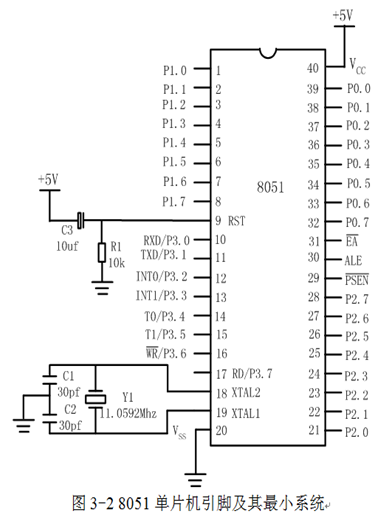

電源引腳: VCC (40腳)和VSS(20腳)分別接供電電源正極和負極。

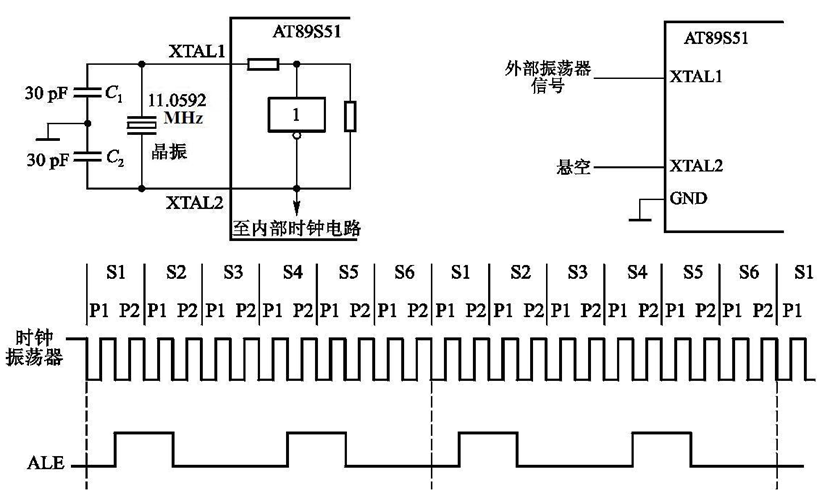

時鐘電路引腳:單片機需要有時鐘脈沖信號才能工作,經(18腳)和 (19腳)接振蕩電路。

控制信號引腳包括以下4個:

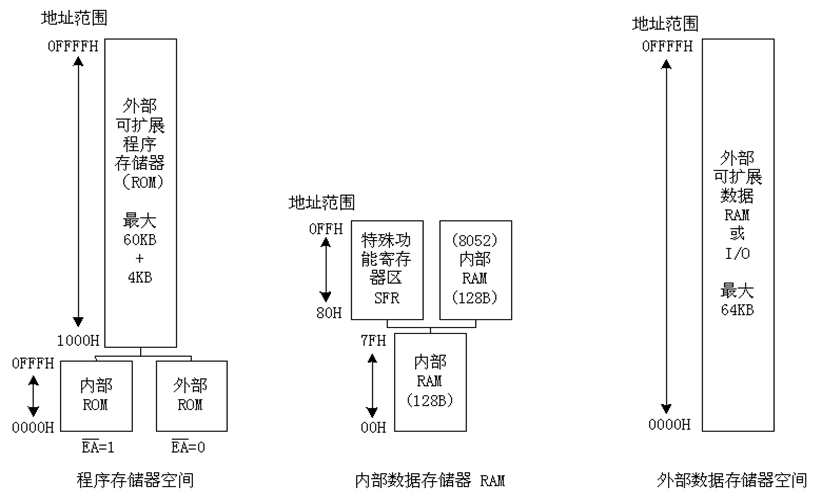

EA( 31腳):當EA接高電平時先內后外執行ROM程序。接低電平時只執行外部ROM程序。

RST (9腳):當輸入兩個機器周期以上的高電平時實現復位,使單片機初始化并重新執行程序。

ALE (30腳):訪問外部存儲器和其他外設時,ALE控制低8位地址和數據的分時傳送。

PSEN (29腳):外部程序存儲器讀選通信號。

并行輸入/輸出引腳共32個:

PO口(39-32腳):可作地址/數據總線端口用,也可作普通I/O口用。

P1口(1-8腳):一般只用作I/O端口。

P2口(21-28腳):當訪問外部存儲器時可輸出高8位地址,也可作普通I/O端口使用。

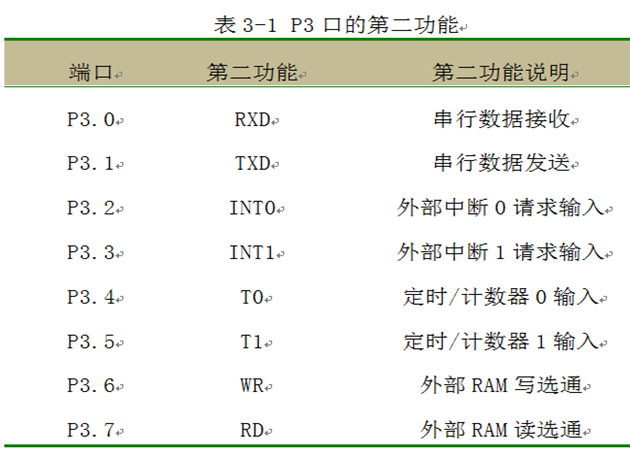

P3口(10-17腳):主要用其第二功能,也可作普通I/O口用。

三、并行輸入/輸出

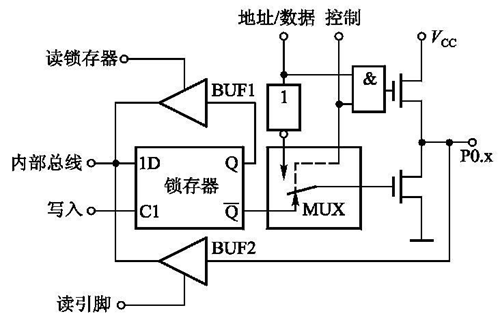

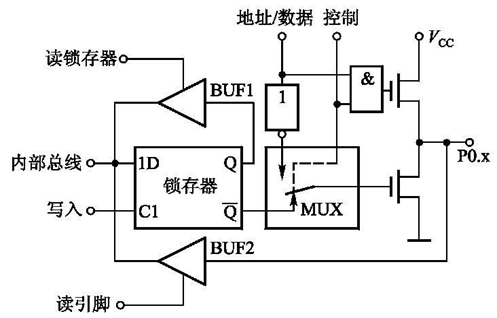

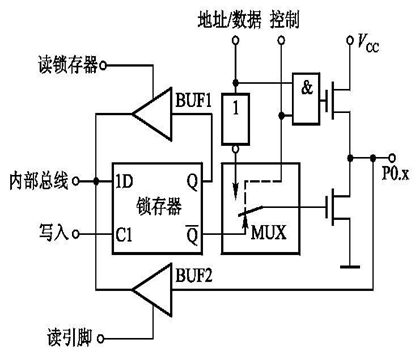

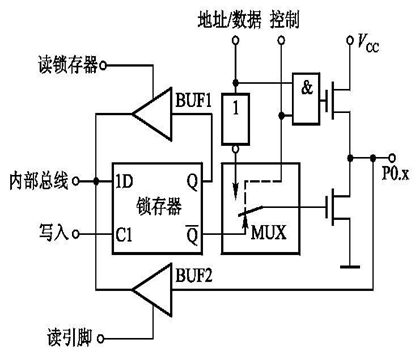

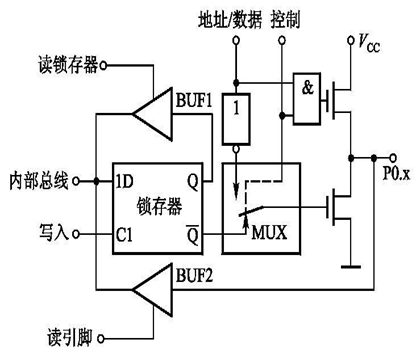

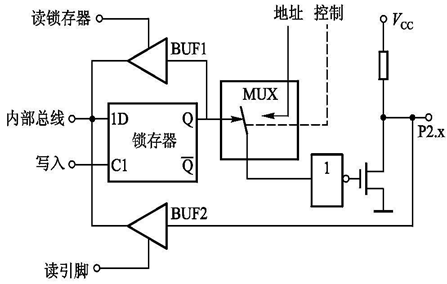

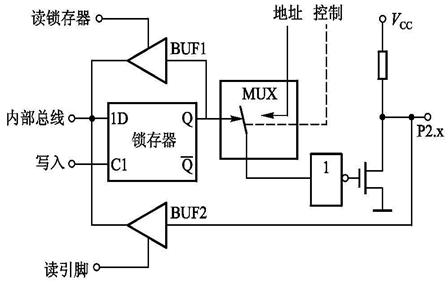

P0口位電路結構

1個數據輸出鎖存器。

2個三態的數據輸入緩沖器BUF1和BUF2。

2個場效應管(FET)。

多路開關、反相器、與門各1個。

P0口工作原理——用作復用的地址/數據總線

輸出:“控制”信號為1,硬件自動使轉接開關MUX打向上面,接通反相器的輸出,同時使“與門”開啟。

①當輸出的地址/數據信息=1,“與門”輸出為1,上方場效應管導通,下方場效應管截止,P0.x引腳輸出為1。

②當輸出的地址/數據信息=0,上方場效應管截止,下方場效應管導通,P0.x引腳輸出為0。

P0口工作原理——用作復用的地址/數據總線

輸入:當P0口作為數據輸入時,僅從外部引腳讀入信息,“控制”信號為0,MUX接通鎖存器Q端。

P0口作為地址/數據復用方式訪問外部存儲器時,CPU自動向P0口寫入FFH,使下方場效應管截止,上方場效應管由于控制信號為0也截止,從而保證數據信息的高阻抗輸入,從外部輸入的數據直接由P0.x引腳通過輸入緩沖器BUF2進入內部總線。

①當D鎖存器為1時, 端為0,下方場效應管截止,輸出為漏極開路,此時,必須外接上拉電阻才能有高電平輸出;

②當D鎖存器為0時,下方場效應管導通,P0口輸出為低電平。

P0口工作原理——用作通用I/O口

輸入:兩種讀入方式:“讀鎖存器”和“讀引腳”。

①當CPU發出“讀鎖存器”指令時,鎖存器的狀態由Q端經上方的三態緩沖器BUF1進入內部總線。

②當CPU發出“讀引腳”指令時,鎖存器的輸出狀態Q=1(Q端為0),而使下方場效應管截止,引腳的狀態經下方的三態緩沖器BUF2進入內部總線。

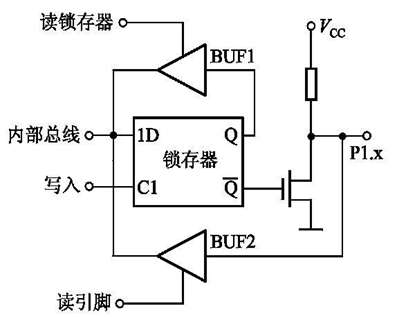

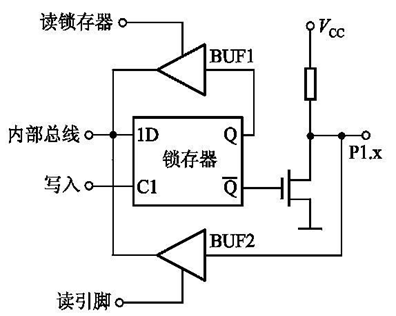

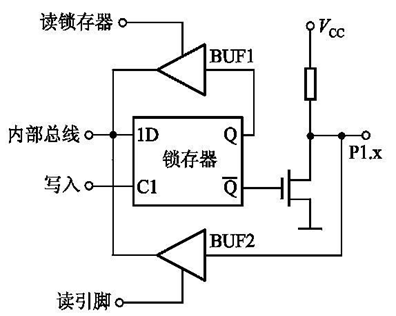

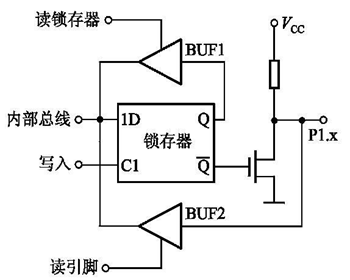

P1口位電路結構

1個數據輸出鎖存器。

2個三態的數據輸入緩沖器BUF1和BUF2。

1個場效應管(FET)和1個片內上拉電阻組成。

P1口工作原理——只用作通用I/O口

①若CPU輸出1,Q=1,Q-=0,場效應管截止,P1.x腳輸出為1;

②若CPU輸出0,Q=0,Q- =1,場效應管導通,P1.x腳輸出為0。

P1口工作原理——只用作通用I/O口

輸入:分為“讀鎖存器”和“讀引腳”

①讀“鎖存器”,輸出Q狀態經輸入緩沖器BUF1進入內部總線;

②“讀引腳”,先向鎖存器寫1,使場效應管截止,P1.x引腳上的電平經輸入緩沖器BUF2進入內部總線。

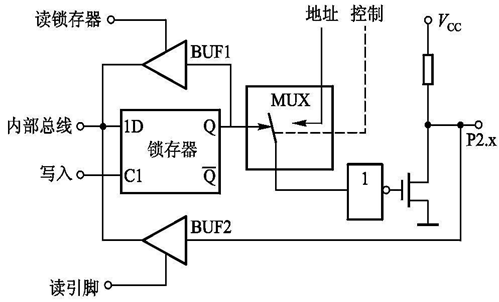

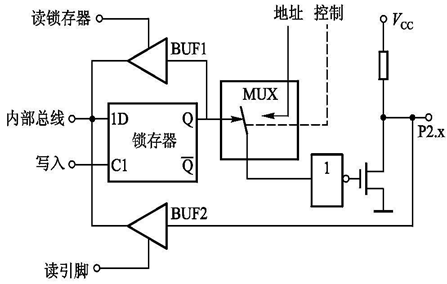

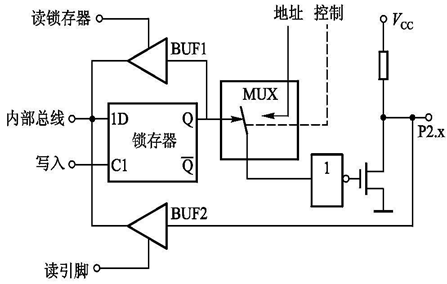

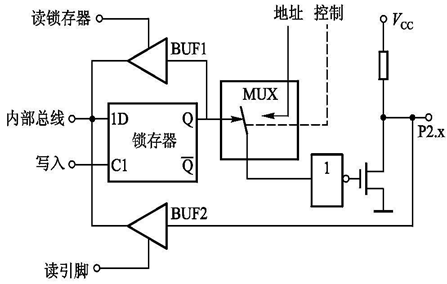

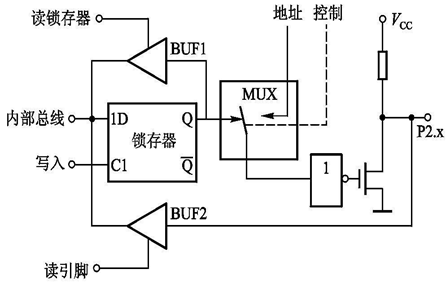

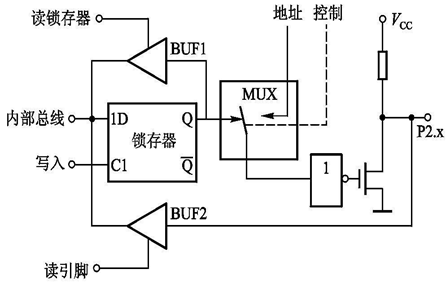

P2口位電路結構

1個數據輸出鎖存器。

2個三態的數據輸入緩沖器BUF1和BUF2。

1個場效應管(FET)和1個片內上拉電阻組成。

1個多路轉接開關MUX

P2口工作原理——用作地址總線

在控制信號作用下,MUX與“地址”接通。

①當“地址”為0時,場效應管導通,P2口引腳輸出0;

②當“地址”線為1時,場效應管截止,P2口引腳輸出1。

P2口工作原理——用作通用I/O口

輸出:在內部控制信號作用下,MUX與鎖存器Q端接通。

①CPU輸出1時,Q=1,場效應管截止,P2.x引腳輸出1;

②CPU輸出0時,Q=0,場效應管導通,P2.x引腳輸出0。

P2口工作原理——用作通用I/O口

輸入:分“讀鎖存器”和“讀引腳”兩種方式。

①“讀鎖存器”時,Q端信號經輸入緩沖器BUF1進入內部總線;

②“讀引腳”時,先向鎖存器寫1,使場效應管截止,P2.x引腳上的電平經輸入緩沖器BUF2進入內部總線。

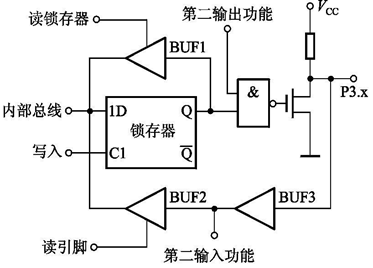

P3口位電路結構

1個數據輸出鎖存器。

3個三態的數據輸入緩沖器BUF1和BUF2。

1個場效應管(FET)和1個片內上拉電阻組成。

1個多路轉接開關MUX和1個與非門

P3口工作原理——用作第二功能

輸出:該位的鎖存器需要置“1”,使“與非門”為開啟狀態。

當第二輸出為1時,場效應管截止,P3.x引腳輸出為1;

當第二輸出為0時,場效應管導通,P3.x引腳輸出為0。

P3口工作原理——用作第二功能

輸入:該位的鎖存器和第二輸出功能端均應置1,保證場效應管截止,P3.x引腳的信息由輸入緩沖器BUF3的輸出獲得。

P3口工作原理——用作通用I/O口

輸出:第二輸出功能端應保持“1”,“與非門”開啟。

CPU輸出1時,Q=1,場效應管截止,P3.x引腳輸出為1;

CPU輸出0時,Q=0,場效應管導通,P3.x引腳輸出為0。

P3口工作原理——用作通用I/O口

輸入:P3.x位的輸出鎖存器和第二輸出功能均應置1,場效應管截止。

P3.x引腳信息通過輸入BUF3和BUF2進入內部總線,完成“讀引腳”操作;

也可執行“讀鎖存器”操作,此時Q端信息經過緩沖器BUF1進入內部總線。

四個并口(P0-P3)在讀引腳之前,都需要將鎖存器置“1”,使場效應管截止,避免鎖存器內數據的干擾。

由于在輸入操作前還必須附加一個置“1”的準備動作,因此稱為“準雙向口”。

四個并口(P0-P3)都是準雙向口

四、8051單片機的最小系統板

8051單片機內部有4KB閃爍存儲器,本身就是一個數字量輸入/輸出的最小應用系統。

在構建8051單片機最小應用系統時,8051單片機需要外接時鐘電路和復位電路即可,如下圖所示。

注意:本最小應用系統只能作為小型的數字量的測控單元。

-

單片機

+關注

關注

6035文章

44554瀏覽量

634660 -

存儲器

+關注

關注

38文章

7484瀏覽量

163765 -

中央處理器

+關注

關注

1文章

124瀏覽量

16519

發布評論請先 登錄

相關推薦

8051單片機C語言開發環境實務與設計

簡述8051單片機基本結構

8051單片機的歷史_8051單片機的應用領域

8051系列單片機的原理和結構介紹

簡述8051單片機結構與原理

8051單片機的結構與原理

8051單片機的結構與原理

評論