系統性的掌握技術開發以及相關要求,對個人就業以及職業發展都有著潛在的幫助,希望對大家有所幫助。本次帶來Vivado系列,Vivado開發軟件開發設計流程。話不多說,上貨。

Xilinx FPGAVivado 開發流程

作者:李西銳校對:陸輝

在做任何設計之前,我們都少不了一個工作,那就是新建工程,我們設計的一些操作,必須在工程下完成,那么接下來就向大家介紹一下新建工程的步驟。那么我以簡單的二輸入與門為例向大家介紹一下操作步驟。

在后續的開發設計中,我們會做各種各樣的設計。每個設計都有自己的名字,在上述文件內,用實驗的名字命名一個文件夾。名字的話一定要帶有某種含義,不建議隨便給個字母序列當做名字。例如:第一個要做的二輸入與門的設計,命名為and_gate2_1。

做好設計前準備后,我們開始新建工程。

* 新建工程

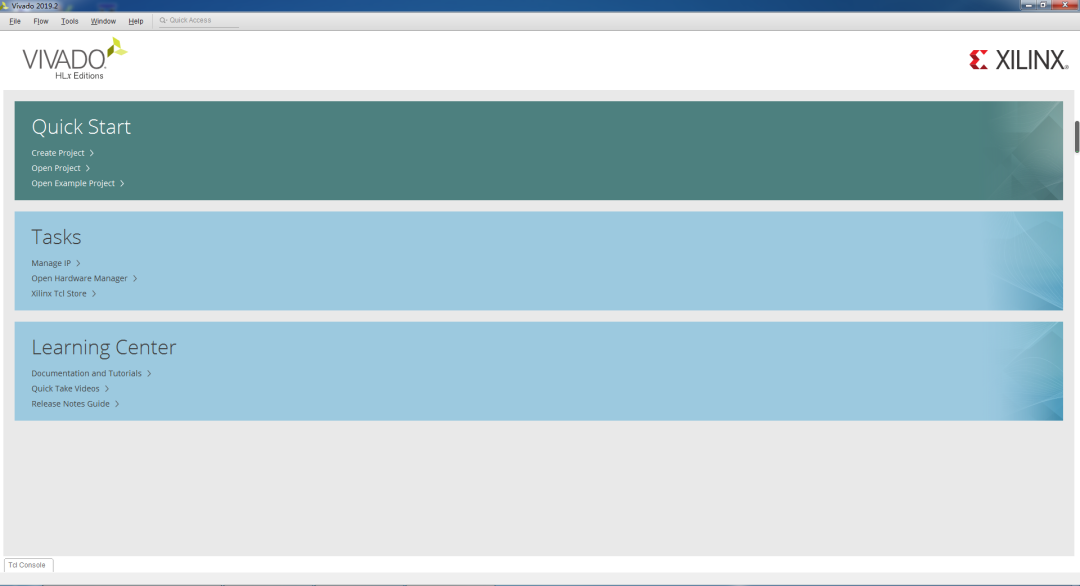

雙擊打開Vivado。

在Quick Start中,我們選擇Creat Project。打開新建工程向導,如下:

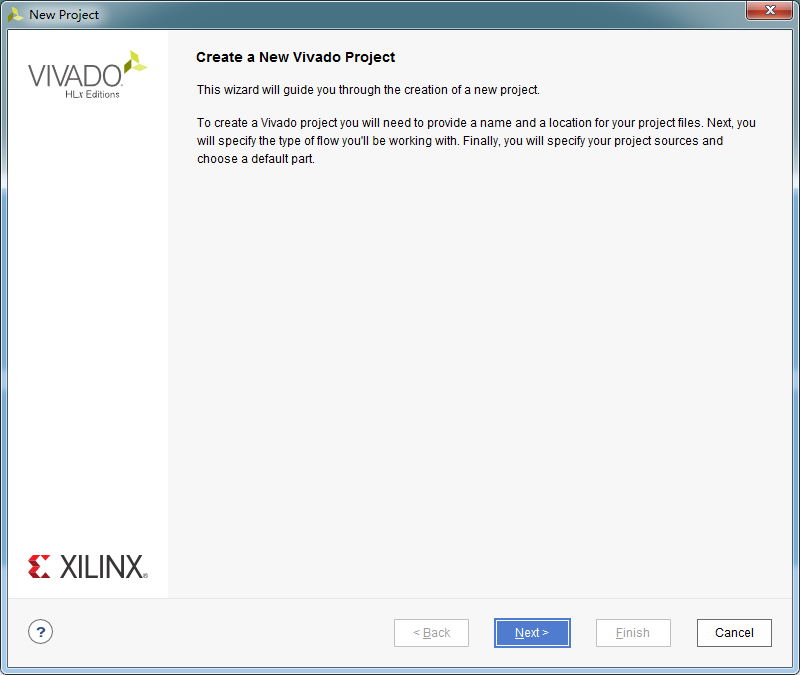

此界面為新建工程引導,此步驟沒有可以設置的內容,所以直接點擊NEXT。

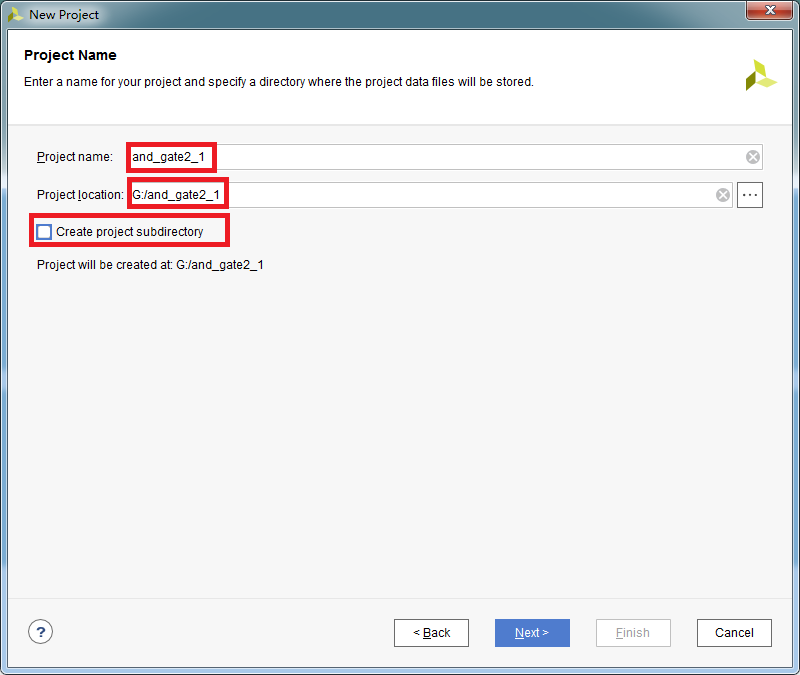

在此界面,我們第一步,需要給我們的工程起一個名字,在此我們起名為and_gate2_1。在第二步設置工程存放路徑,要求無中文路徑。第三步,如果你指定路徑位置沒有對應的and_gate2_1文件夾,那么我們就可以勾選上,軟件會自動幫我們新建。由于我已經新建過了文件夾,所以此處我沒有勾選此選項。設置好之后,點擊NEXT。

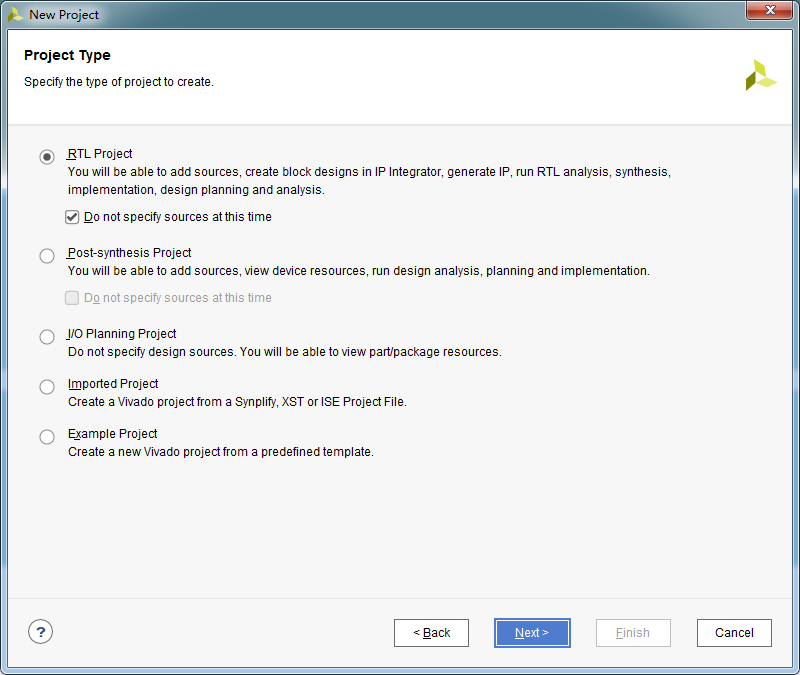

此界面我們設置工程類型,選擇RTL Project。在這個選項下面,還有另外的一個選項。這個是讓我們選擇是否創建源文件。圖示中選擇不新建,在建完工程之后我們在新建源文件。繼續點擊NEXT。

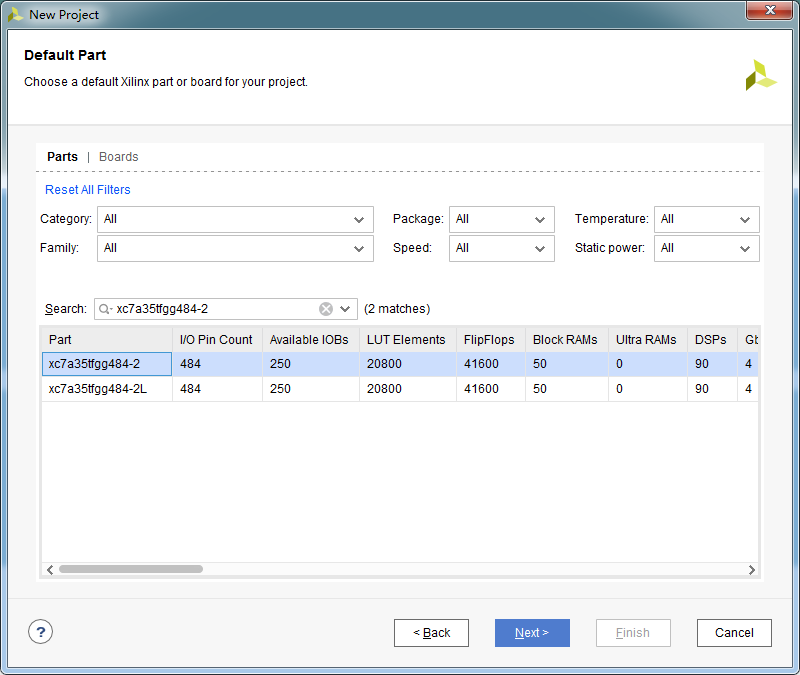

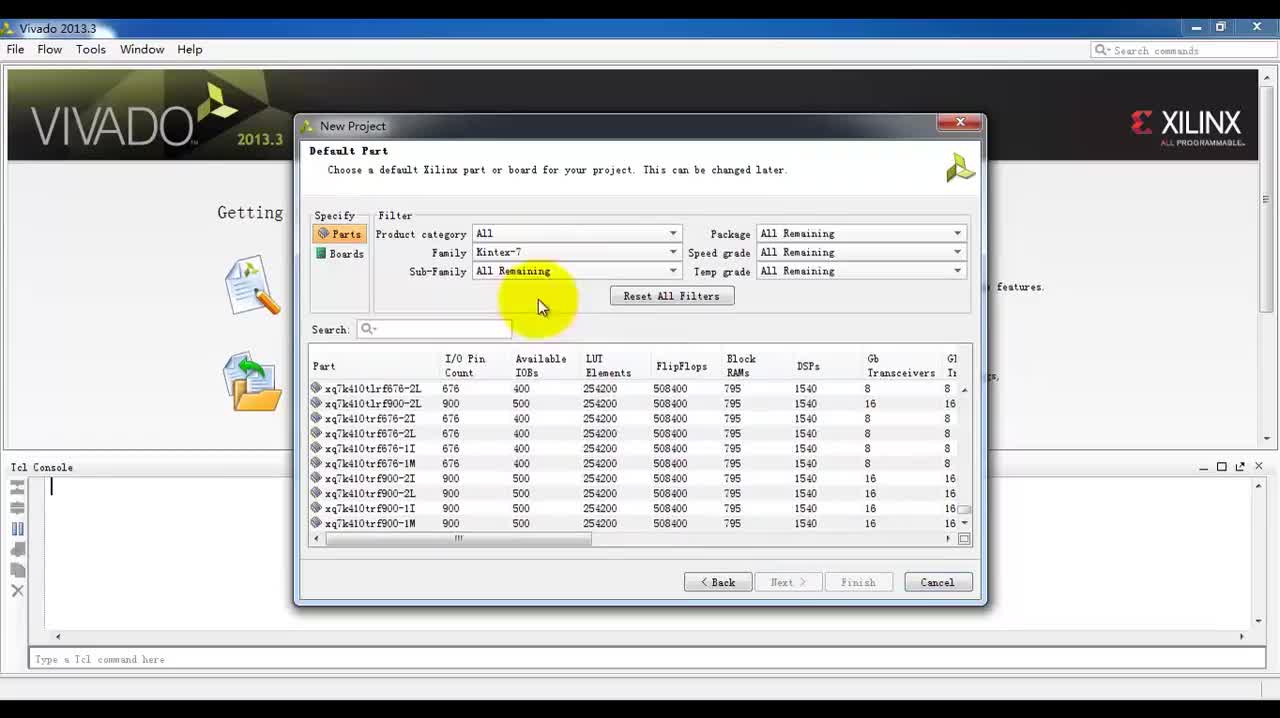

在這個步驟里面,我們選擇對應開發板的芯片型號。我以SANXIN-B04為例,芯片型號為XC7A35TFGG484-2。可以在搜索框里直接輸入,在下面的選項里面我們選擇第一個,如圖所示。選中之后點擊NEXT。

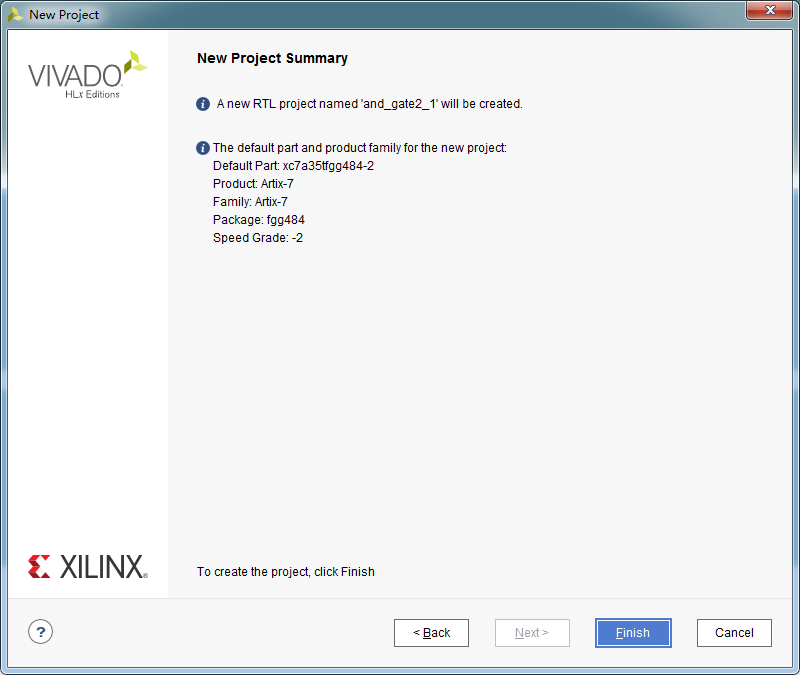

最后一步,為工程的信息展示。確認信息無誤后,點擊Finish。至此,我們的工程就新建完成了。

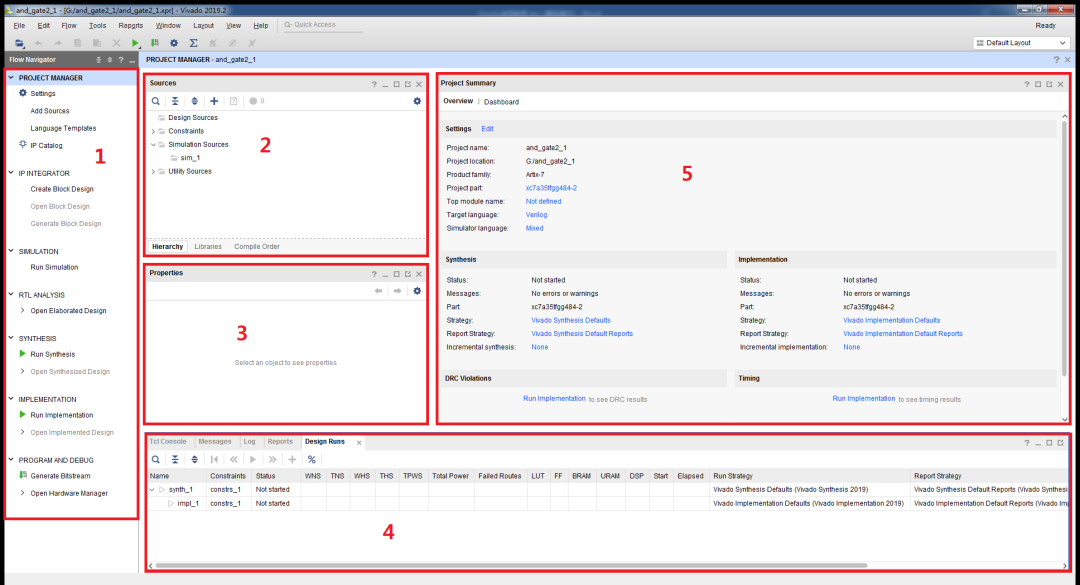

我們把整個界面分為5個區域,如上圖所示。

1、菜單;

軟件的常用功能全在此區域,方便我們進行后續操作。每一項的作用,會在后續的講解中為大家介紹。

2、源文件;

新建文件可以在此區域,在這個窗口下面,有三個選項,我們在第一個選項中可以看到代碼文件的層次結構。

3、屬性;

窗口會顯示所選內容的具體信息

4、信息;

展示任務進度,編譯信息等內容。

5、報告;

展示工程信息以及狀態。此外編寫代碼也是在此區域。

通過以上的介紹,我們明白了各個區域的作用,接下來我們就新建文件開始編寫代碼:

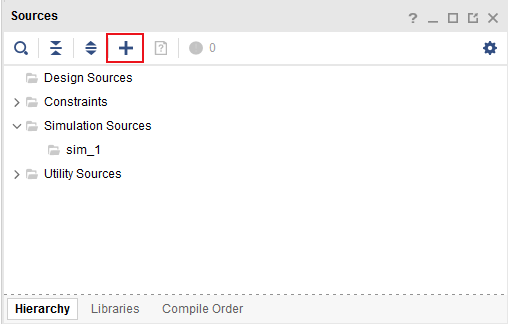

在源文件窗口,點擊+號。如下圖:

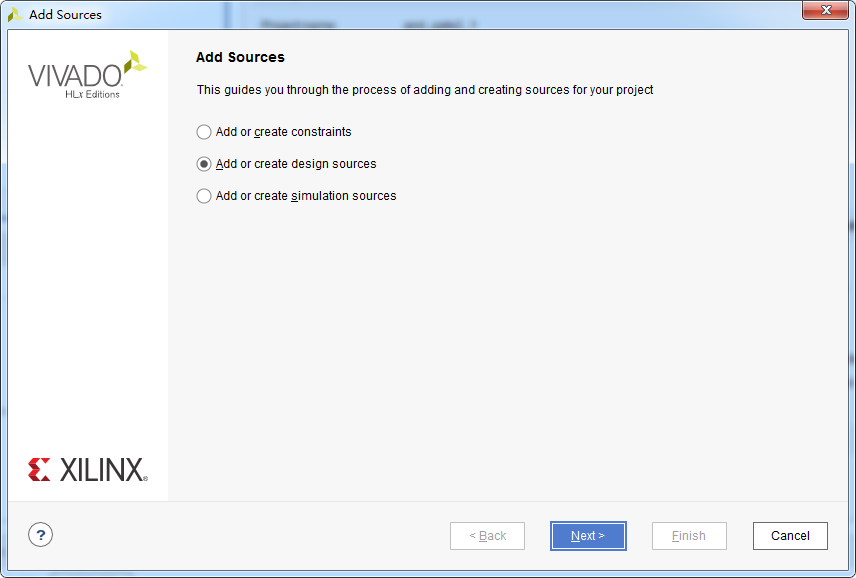

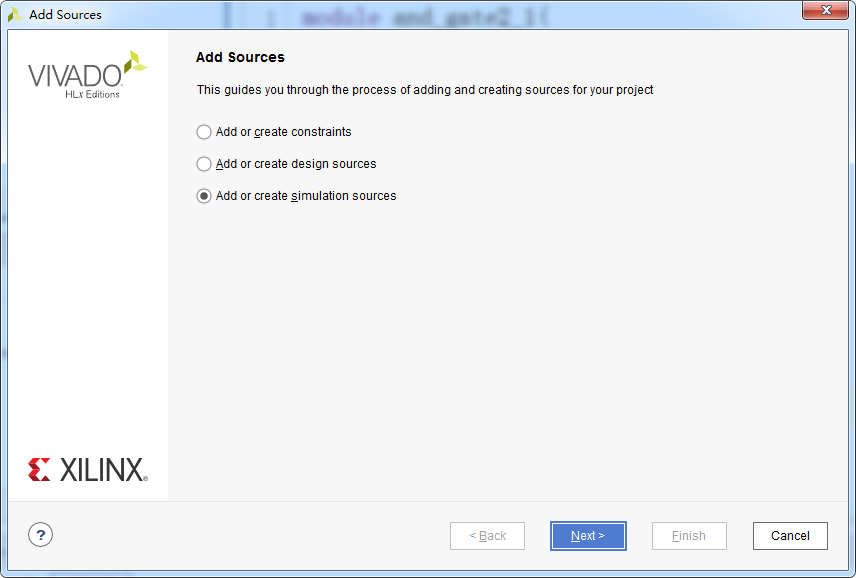

三個選項,第一個是添加或者新建管腳約束文件,第二個是添加或者新建源文件,第三個是添加或者新建仿真文件。那么我們選擇第二個選項。

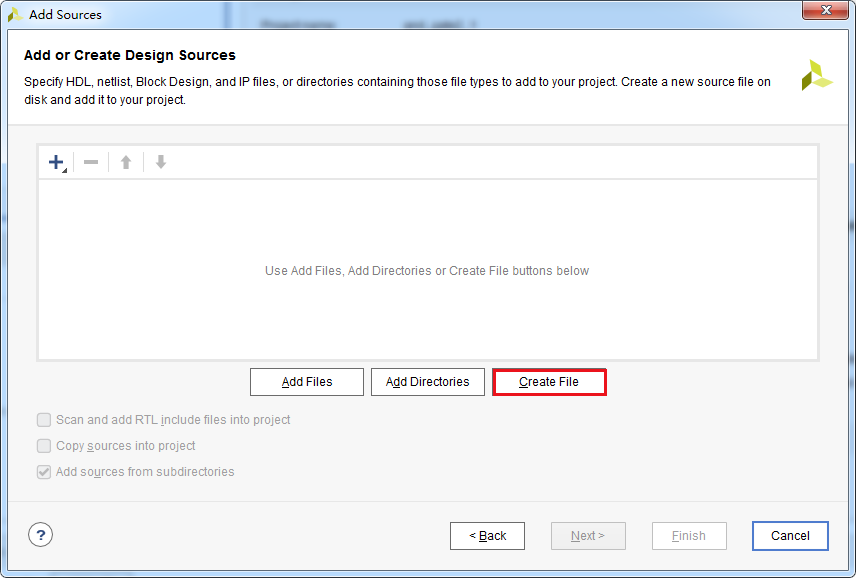

選擇好之后,點擊NEXT。然后按照上圖中所示,點擊Creat File;

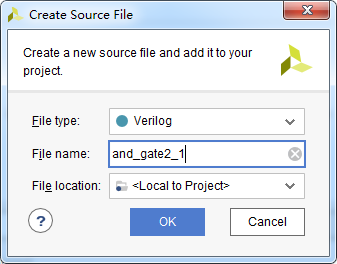

在File name一項中,填入文件名,其他保持默認,然后點擊OK,再點擊Finish。

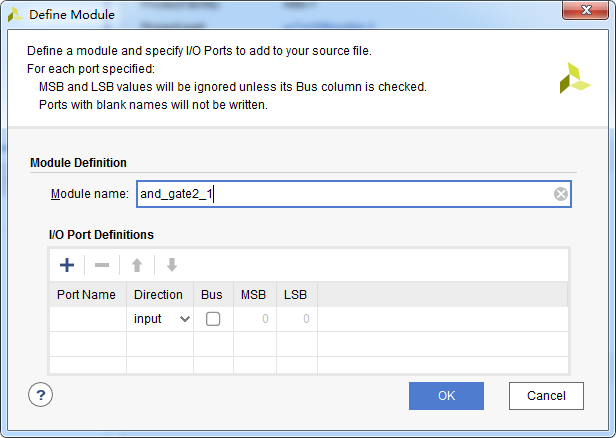

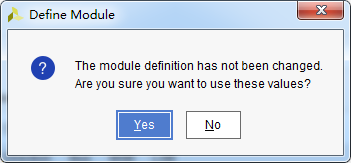

此界面我們可以提前填入端口,選擇好端口方向以及位寬。然后軟件就可以幫我們寫好代碼的端口定義部分。如果不需要可以直接點擊OK。

再點擊YES。

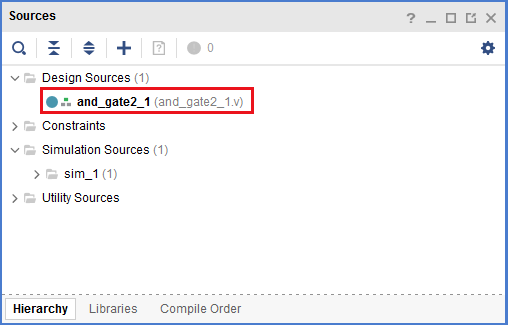

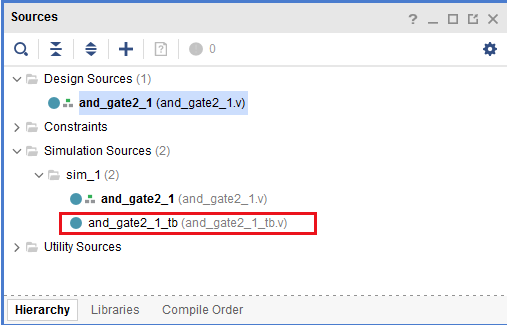

新建好之后,會出現如下圖:

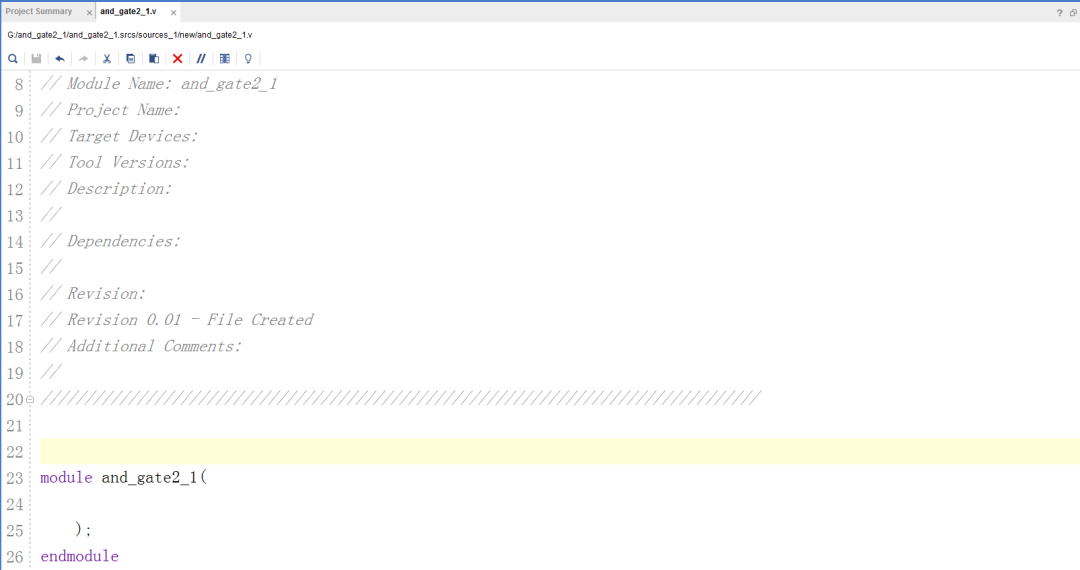

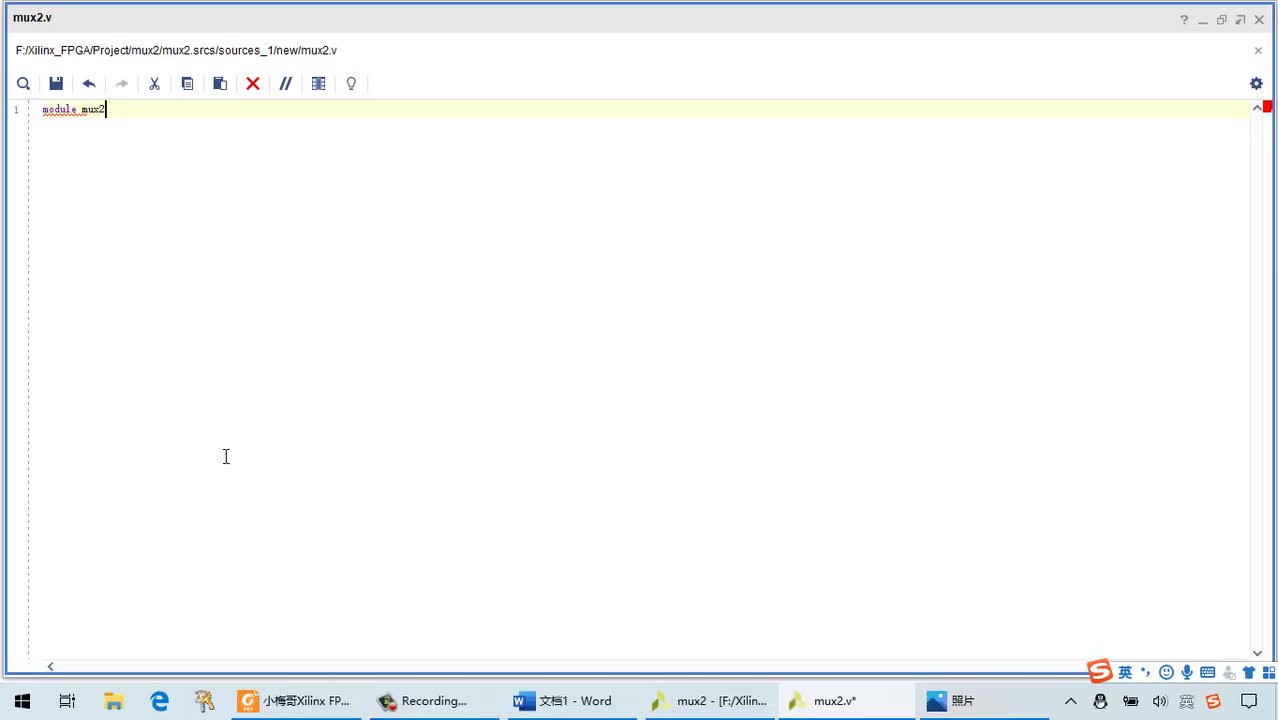

在Design Sources中,可以看到我們新建的文件。雙擊打開開始寫代碼。自動生成的代碼如下:

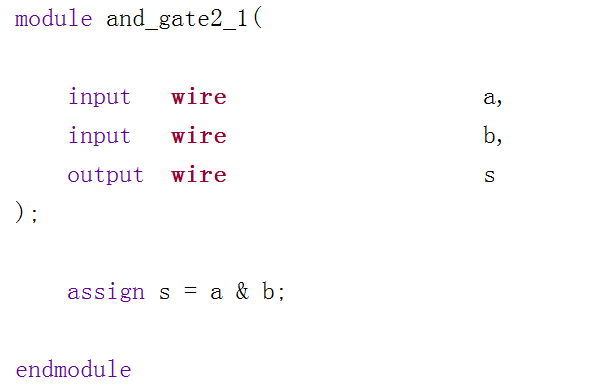

為了更好的向大家展示,我將代碼文件中的注釋先刪除掉。代碼如下:

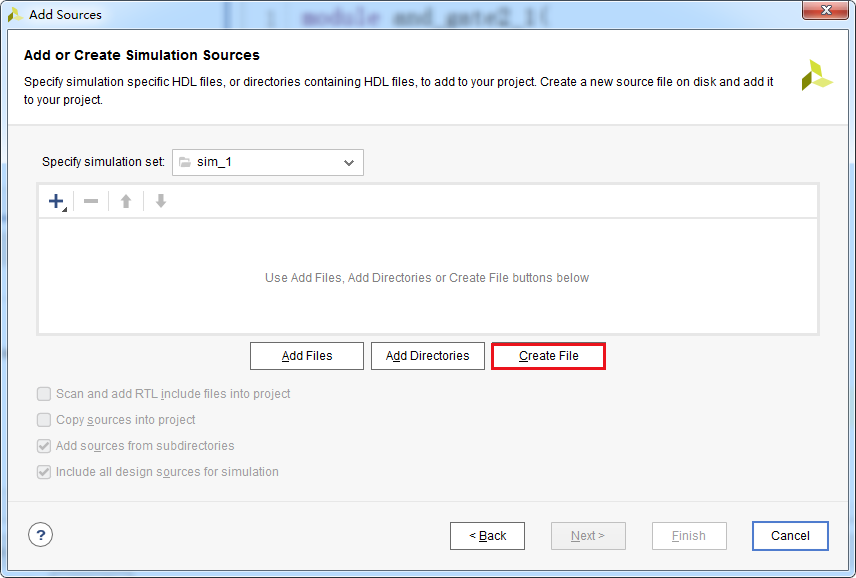

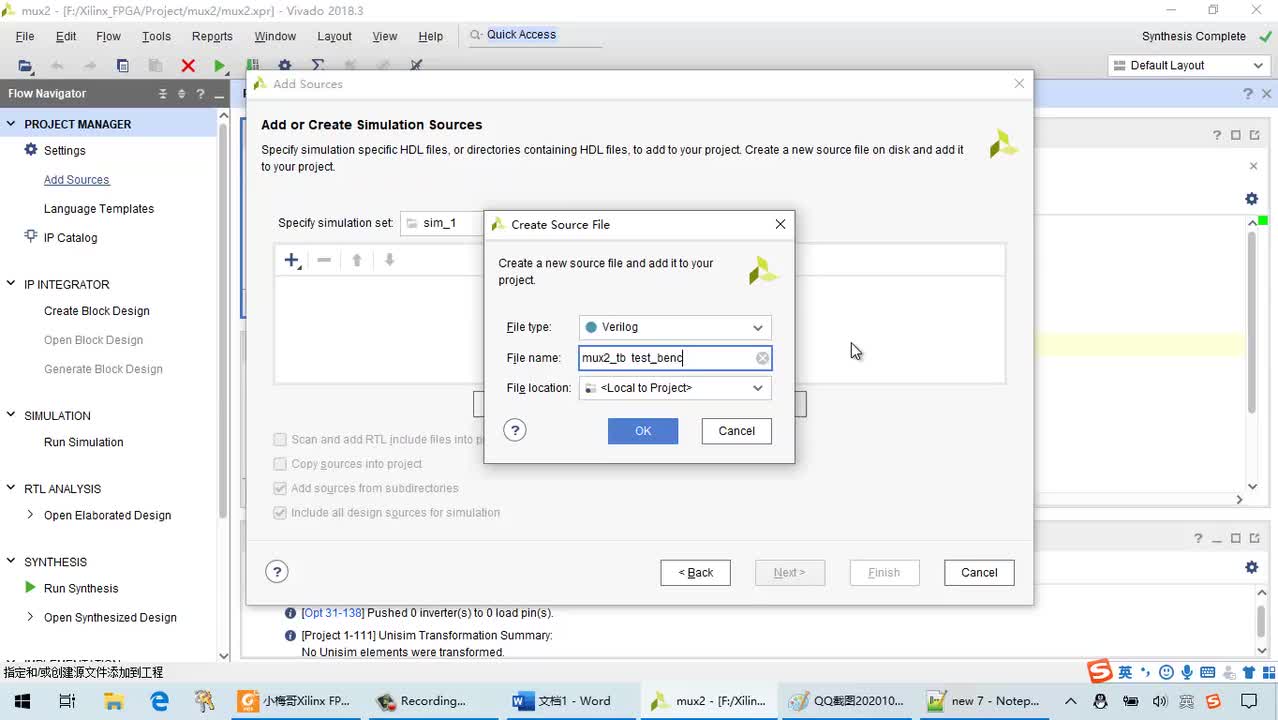

為了驗證代碼的正確性,還需要寫測試文件進行仿真測試。仍然點擊+號新建文件,只不過這次我們選擇第三個選項:

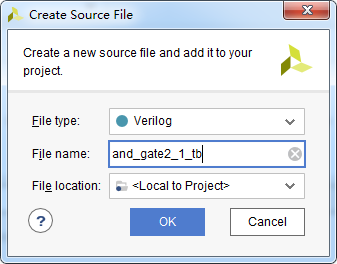

點擊NEXT;選擇Creat File:

點擊OK,點擊Finish。定義端口界面直接跳過,因為我們的仿真文件沒有端口。

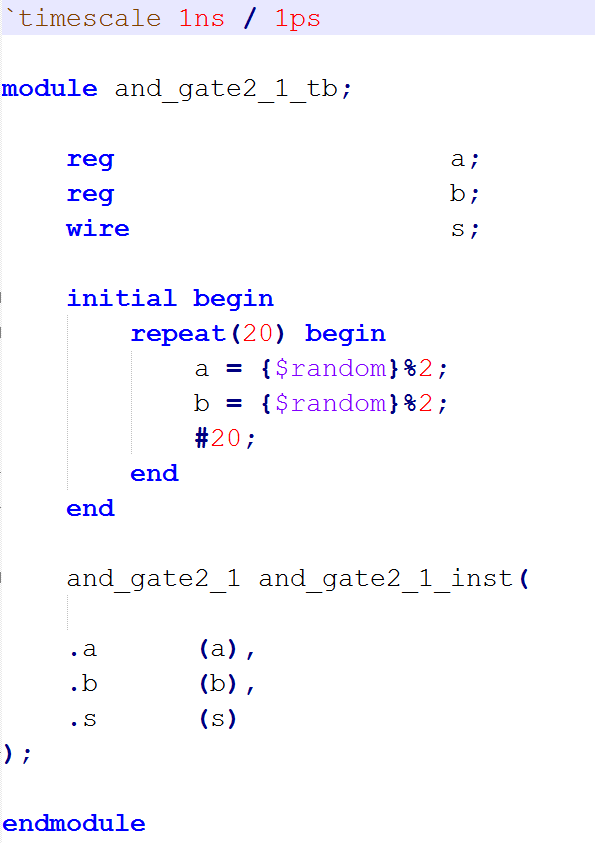

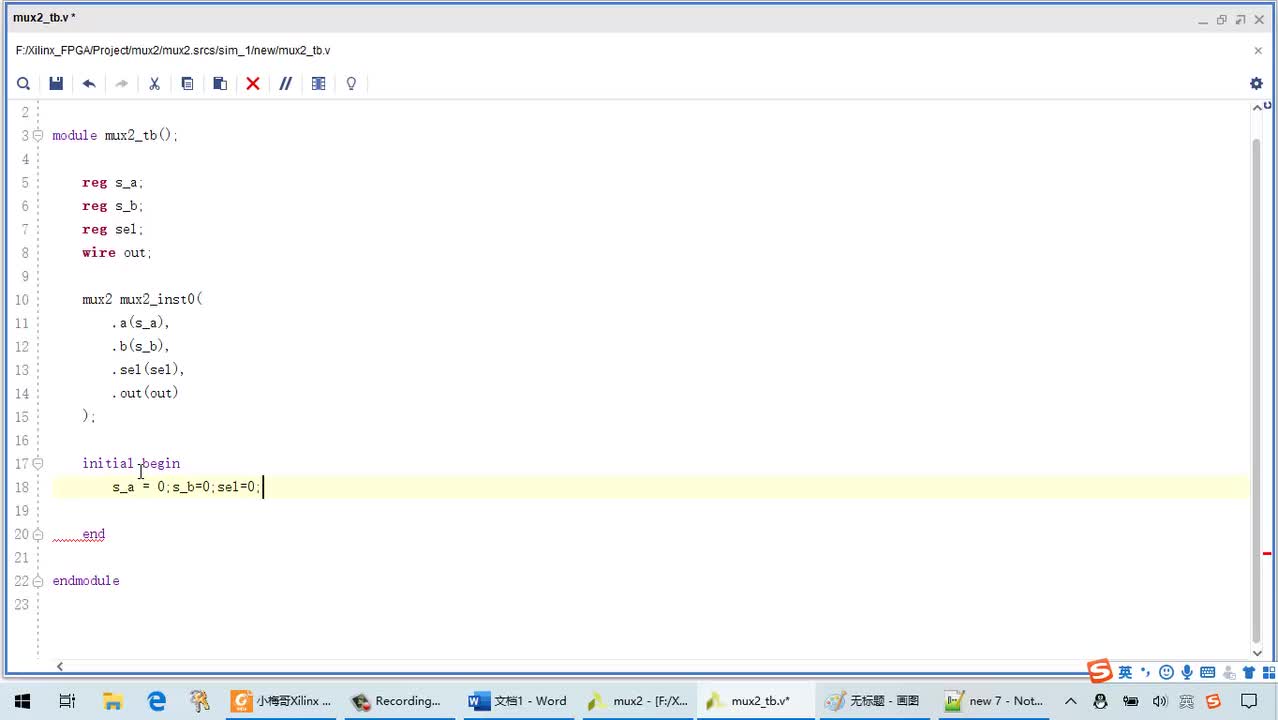

新建好之后,按照上圖所示,雙擊打開文件。代碼如下:

我們可以使用隨機數來產生我們需要的輸入,代碼寫完之后,我們可以直接打開仿真。

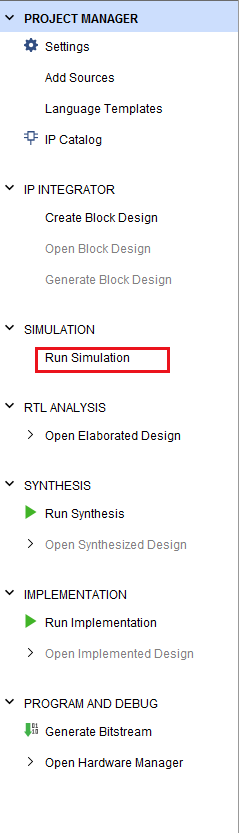

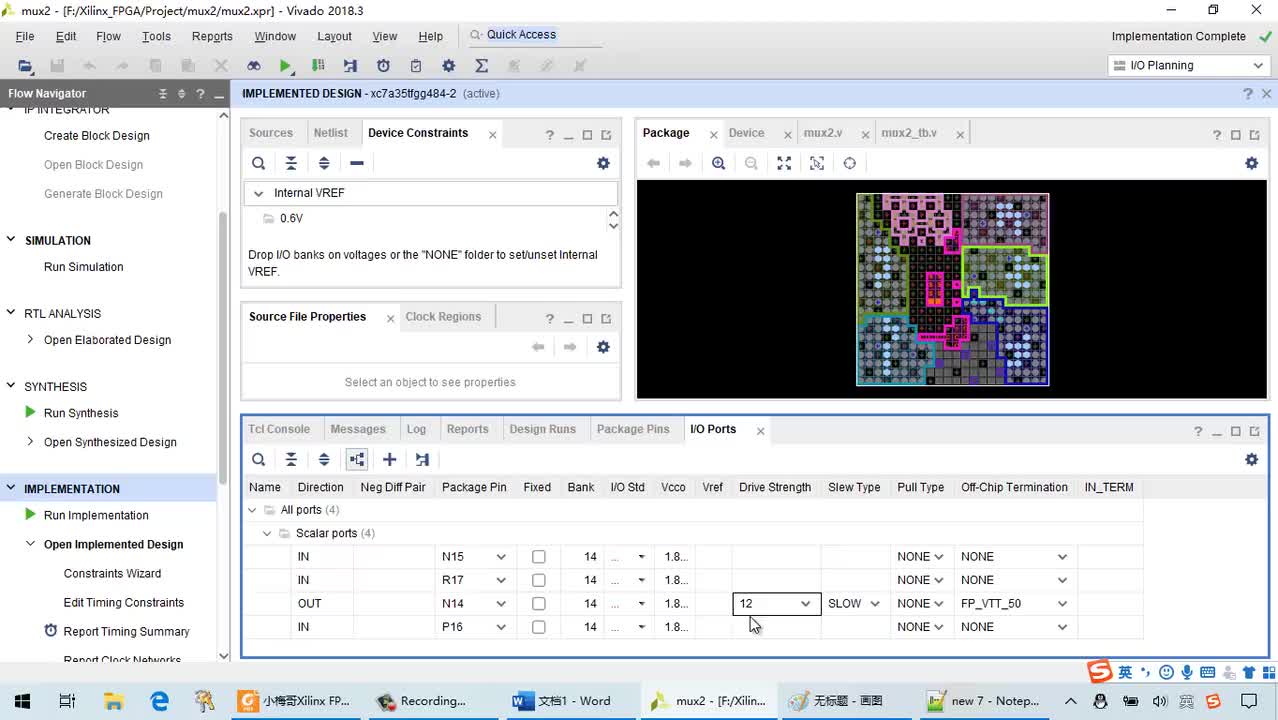

點擊如圖所示的選項,打開軟件的仿真器。

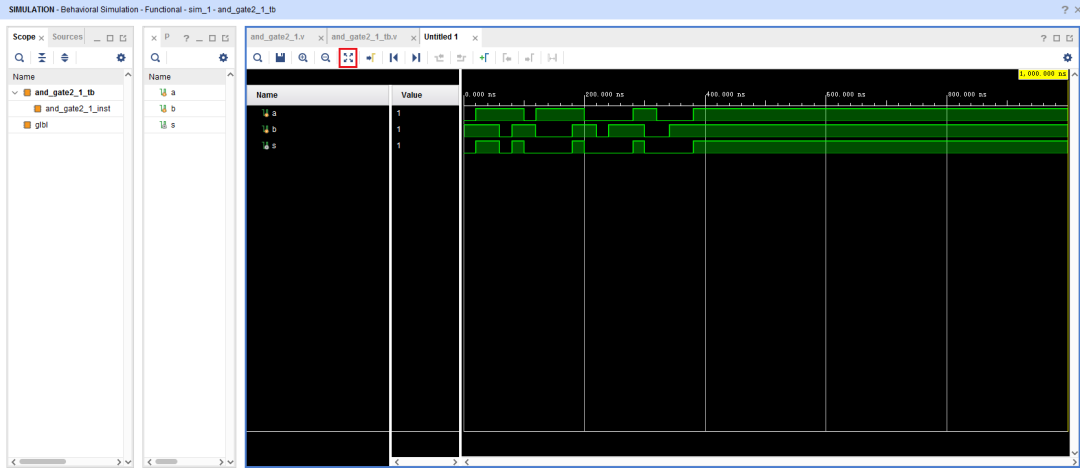

仿真圖打開后,我們點擊如圖所示的按鈕,可以看到全部波形。在仿真圖中,我們可以看到后半部分波形沒有變化,這是因為我們隨機數生成了20組,每組20ns,所以總時長為400ns。但是仿真軟件是默認運行1us的,所以就看到了如圖所示的情況,在此,大家可以隨意生成隨機數的個數。我們驗證仿真時,只需要看前400ns的波形就可以了。按照波形顯示,我們可以驗證到波形輸出與與門真值表相同,所以最終結果是正確的。至于下板驗證后續再出相關文章說明。

-

FPGA

+關注

關注

1643文章

21925瀏覽量

612559 -

Xilinx

+關注

關注

73文章

2179瀏覽量

124000 -

Quick

+關注

關注

0文章

17瀏覽量

12545 -

開發軟件

+關注

關注

1文章

25瀏覽量

13103 -

Vivado

+關注

關注

19文章

826瀏覽量

67998

原文標題:Xilinx FPGA Vivado 開發流程

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

評論