按照最終外形來看,現在有無數種封裝方式,這個實在是太多了,比如 QFP,QFN,SOT,DIP,BGA 等等,所以我們今天不以這種方式介紹。所以現在按照封裝的發展歷史來介紹,以封裝工藝的方式來分類。

第 1 代封裝:wire bond(俗稱,打線)

這種封裝方式是最早出現的,雖然是第一代技術,但是直到現在也有很多芯片使用這種方式來封裝,就是因為技術成熟,成本低。最后封裝成的模樣就是這樣子的。

先聊一下這種封裝流程

1切割

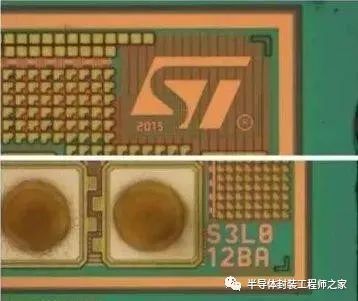

在封裝廠拿到 wafer 之后,先把 wafer 進行切割,得到一顆一顆的芯片,將那些 CP 測試(下一次我們再聊測試)通過的芯片單獨拿出來。這里要說一個問題,一顆芯片從在沒有做任何處理之前,那些引腳是長這個樣子的,如下圖左下角的方形圖案(你先忽略那兩個圓形的東西,后面我就知道那兩個圓形是怎么來的了),這些引腳也有一個名字,叫做 pad。

2固定在 lead frame 上

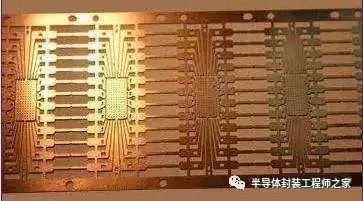

將芯片放到 lead frame 上,并且用銀漿固化,其實就是將芯片和 lead frame 的底部粘住啦。lead frame 可以理解為引線框架,他是一個陣列結構,如下圖

就是將芯片放到中間的凹槽,四周都是我們最終看到的引腳。在最終結束工藝之后,就把這些引腳“剪開”,然后掰彎,最終形成我們看到的樣子。所以第二步完成之后,從側面看的話是下圖這個樣子。

這里要注意,就是芯片必須是正面朝向,當正面朝上的時候,pad 也是朝上的。lead frame 的引腳在兩側。

3打線

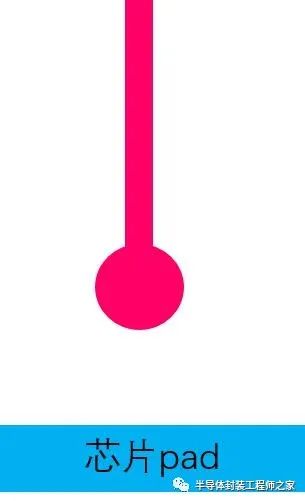

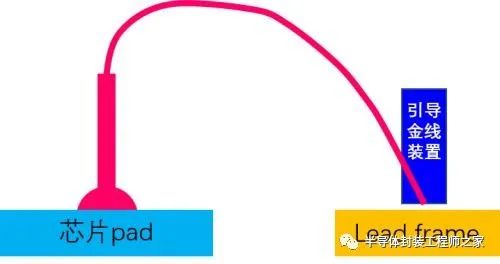

用金線(或者是銅線,鋁線)將芯片的 pad 和 lead frame 連接起來。線的種類會根據芯片的不同制程,或者是根據芯片 pad 的不同結構來決定使用金線或者是銅線。在打線時,先讓金線在低端形成一個金球。

然后將金球壓倒芯片的 pad 上,然后通過施壓壓力或者改變溫度來焊接到 pad 上,這就會在 pad 上形成一個圓點,上面第二張圖中的圓點就是這么形成的。

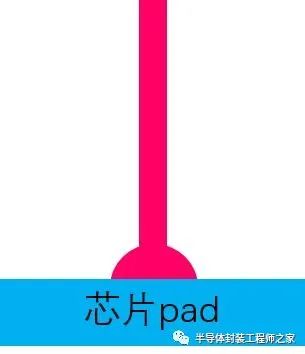

然后將金線拉升,并且移動到 lead frame 上方。當然不要擔心金線會斷,因為金線不是固定長度。可以在上面自動生成金線。所以是這個樣子的。

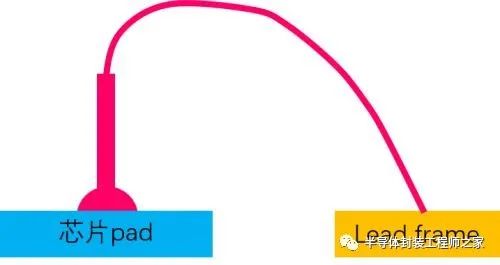

然后再將末端的金線壓到 lead frame 上,再側向劃開,切斷金線,所以會在 lead frame 上會形成切斷金線后的魚尾形狀(我畫不出魚尾形狀啦)。最終是這個樣子。

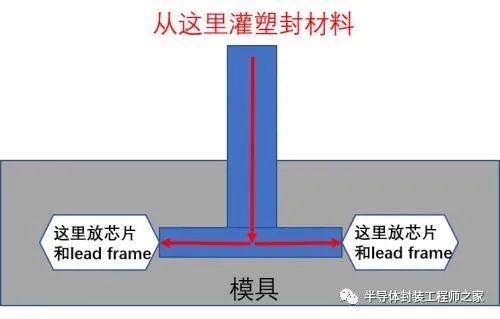

4注塑

也叫塑封。就是將連接好的芯片和 lead frame 放到模具中。然后將塑封材料灌進去。加熱之后這些材料變成液體,再把芯片,金線和 lead frame 都包住。

5包裝

注塑完成后,工作就比較簡單了,比如在芯片頂部打字,打 logo。除去 lead frame 上多余的塑封材料。在 lead frame 上電鍍一層特殊材料,防止外部環境對于引腳的破壞(比如潮濕,高溫等等)。最后將 lead frame 剪開,得到我們想要的引腳方式。

上面這五部就是 wire bond 封裝方式最簡單的流程。這一套工藝在現代封裝技術中已經很成熟了,成本也低。但是里面的很多細節還是比較關鍵的。比如這些制程里面對溫度的控制,特別是在拉線過程中,金線的弧度,高度以及拉力,金球的大小等等。這些參數直接影響芯片的質量,甚至會使芯片無法使用。

第 1.5 代封裝:CSP(Chipe-Size Package)

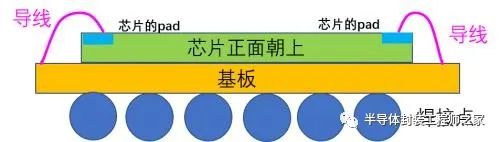

在上面的 wire bond 中,有一個很大的問題,就是最終出來的芯片比實際的芯片要大很多,因為 lead frame 和芯片之間是有距離的。為了解決這個問題,人們發明了 CSP 封裝技術。它的思想很簡單,就是去掉 lead frame,用一塊基板代替。

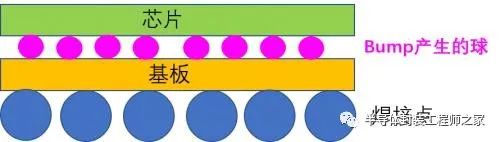

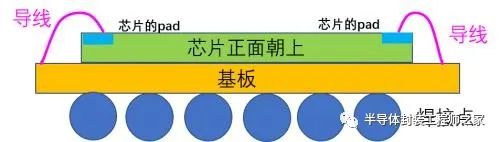

基板的作用就是將導線從 pad 引過來之后,基板里面有自己的一些電路,將這些導線引到下面的焊接點上(焊接點也是球型)。這樣就形成了外部電壓通過焊接點,基板(導線)與芯片的 pad 交流。

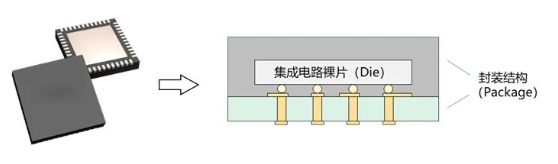

所以最終出現的芯片是這樣的。當然下面的芯片有可能不是用這種方式封裝,但是最終的樣子是一樣的。

第 2 代封裝:flip chip(倒裝封裝)

在聊完上面兩種方式之后。我們會發現一個問題,不能批量化操作,也就是必須在晶圓切割成每個芯片之后才能封裝,成本太高。為了解決這個問題,發明了 flip chip 這種方式。

只所以叫做倒裝,是因為在前面的封裝方式中,芯片是正面朝上放到基板上面的。而 flip chip 是正面朝下放置。

這種封裝方式有一個特殊的工藝流程,就是 bump。大家可以理解為長金球(錫球)。

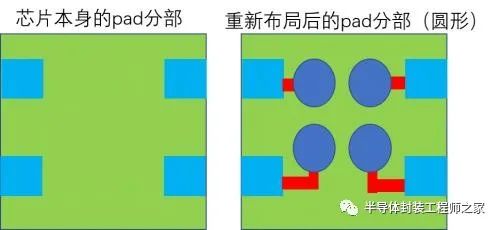

要想長金球,首先要做的就是重新布局芯片 pad 的的位置,利用和芯片制造中相同的后段技術,將邊緣部位的 pad,安排到芯片中央來。這句話就是 bump 的核心目的。

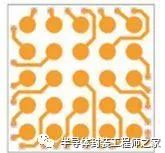

大體思路就是將芯片的 pad 通過導線(紅色)借接出來,然后在想要的位置上重新做一個 pad,實際圖形長這樣子,中間的哪些深色部分就是導線。

大家可能會問,為什么不在芯片的 pad 上直接長錫球呢?因為當芯片的引腳太多時,直接長金球的方式危險系數會大大提高,很容出現兩個引腳短接的情況。這樣重新分配 pad 布局的過程叫做 RDL(re-distribution layer)。準確的說它是指連接新 pad 和舊 pad 的這一層,但是大家在使用的時候,就不再區分,直接把這個過程叫做 RDL。

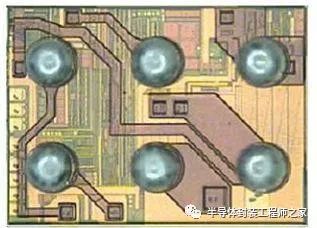

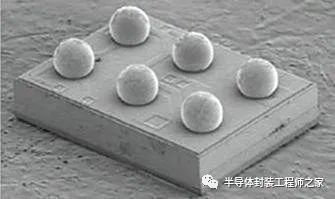

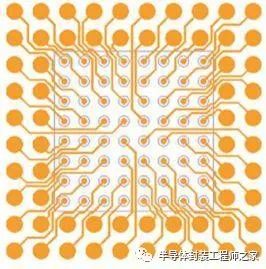

到這里之后,后面一步就是 bump,也就是長金球(錫球)。長金球的過程就不再多說了,和芯片制造工藝中的曝光,刻蝕差不多。最終形成的是這個樣子。

直到長完球(bump)之后,整個 wafer 還沒有被切割,所以這些都是批量操作,成本特別低。這些操作完成后再進行晶圓級測試。也正是因為 bump 過程是在 wafer 上制作的,所以大家都把它叫做 WLCSP(wafer level CSP)。

測試完成之后再切割,把好的芯片拿出來。最后倒扣到基板上面。就這樣,外部電壓通過焊接點以及 bump 產生的球與芯片交流。

這種封裝方式,最省面積,封裝出來的芯片大小和原始大小相差不大。所以這種方式也是比較主流的封裝方式,一般用在高端產品上。在這一套流程中,bump 的過程是最為關鍵的,包括球的大小,導電性等等。

第 3 代封裝技術:InFO,HBM,CoWos

通過上面兩代封裝技術的發展,芯片封裝技術已經可以滿足大部分的需求了,但市場往往是解決一個需求之后,又會產生最新的需求。通過 flip chip 技術,我們解決了芯片封裝的大小問題。但是這種技術隨著 pin 角增多也會出現很多麻煩,主要有下面兩個方面。

1面積縮小,但是 pin 角增多

因為芯片在盡量縮小,pin 角在增多,芯片的面積已經不能裝下這么多焊接點了。因為 flip chip 的封裝方式是將所有的 pin 腳都集中在一顆芯片的下方,所以我們把這種方式另外取一個名字,叫做 FanIn 方式的封裝,又叫扇入型封裝方式。如下圖

所以當 pin 角在增加的時候,芯片下面的面積根本不夠擺放這么多焊接點

2時序要求高

高性能芯片需要多個芯片集成封裝。現在高性能的芯片對于時序(Timing)的要求特別高,所以兩顆芯片不能相距太遠,這樣的話會更利于兩顆芯片進行信息交流,提高數據處理速度,降低發熱。

在這兩個需求下,產生了 InFO(integrated Fan-out)的封裝方式。我們先看 Fan-Out 是什么意思。上面我們了解了 FanIn,那 fanout 就是剛好反過來。它是把引腳的焊接點引到芯片的外部,如下圖。這樣的話,即使芯片的 pin 角增多,也不會帶來上面的困擾。

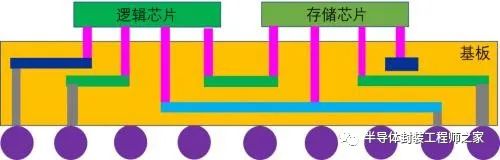

那 integrated 是什么意思呢?就是多個芯片集成封裝。說白了,就是將多個芯片放在一起封裝。將這兩種技術合成在一起就是 InFO 封裝方式。

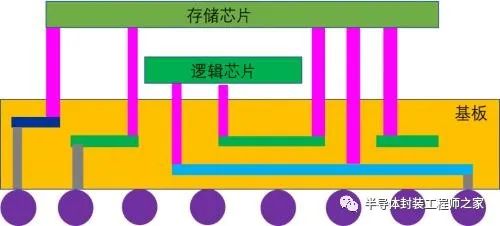

我自己畫了一個圖來向大家稍微介紹一下吧。

假設有兩個芯片,一個是邏輯芯片,一個是存儲芯片。現在需要把這兩個芯片封裝在一起,而且這兩個芯片的某些引腳是可以接在一起的。于是就運用了芯片制作里面的金屬層布線的原理,在基板里面布線,然后將需要的連接在基板就完成,最后在基板的底部連接處焊接球。這樣就可以達到,既可以將多個芯片封裝在一起,也可以應付 pin 腳多的情況。上面這種兩個芯片平行放置的方式較 Multi InFo 工藝。

如果像上面這種,兩個芯片是垂直放置,這種叫做 InFO-PoP 結構。

很多人會問,這種封裝方式不是面積增加了嗎,畢竟占用了芯片以外的地方。其實從得到的好處來說,還是值的的。況且,InFo 的封裝面積可能比各個分別封裝的面積總和要少。

現在這種封裝技術只是使用在高端芯片中,比如蘋果的 A12 等,普通芯片是享受不了這種待遇的,因為真的很貴。臺積電封裝業務的很大一部分盈利都是靠 InFO 來的。

還有一種封裝方式是叫 CoWos(Chip-on-Wafer-on-Substrate),是一種將芯片和硅片(基底)集成在一起的封裝方式。這種封裝方式只有臺積電能做,而且是高度商業機密,技術不外露,所以我也知之甚少,在這里就不和大家介紹了。如果以后我了解到,再和大家更新。

當然第三代封裝技術還有 AMD 推出的 HBM 技術,美光的 HMC 技術,其實都是大同小異。這里也不做介紹了。

審核編輯 :李倩

-

芯片

+關注

關注

456文章

50886瀏覽量

424173 -

半導體

+關注

關注

334文章

27432瀏覽量

219277 -

封裝

+關注

關注

126文章

7933瀏覽量

143042 -

先進封裝

+關注

關注

2文章

411瀏覽量

250

原文標題:半導體先進封裝技術(各代半導體封裝技術簡介)

文章出處:【微信號:半導體封裝工程師之家,微信公眾號:半導體封裝工程師之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

臺積電將持續提供業界領先的CMOS logic技術

多位產學研界大咖齊聚深圳,論劍半導體先進封裝發展之道!

韓國政府聯合三星電子、SK海力士等開發半導體先進封裝技術

半導體先進封裝技術之CoWoS

第1波嘉賓劇透!六大院士專家精彩分享:AEMIC第三代半導體及先進封裝技術創新大會暨先進半導體展

半導體先進封裝技術

半導體先進封裝技術

評論