今天要介紹的是DDR3和DDR4最關鍵的一些技術,write leveling以及DBI功能。

一、Write leveling功能與Fly_by拓撲

Write leveling功能和Fly_by拓撲密不可分。Fly_by拓撲主要應用于時鐘、地址、命令和控制信號,該拓撲可以有效的減少stub的數量和他們的長度,但是卻會導致時鐘和Strobe信號在每個芯片上的飛行時間偏移,這使得控制器(FPGA或者CPU)很難保持tDQSS、tDSS 和tDSH這些參數滿足時序規格。

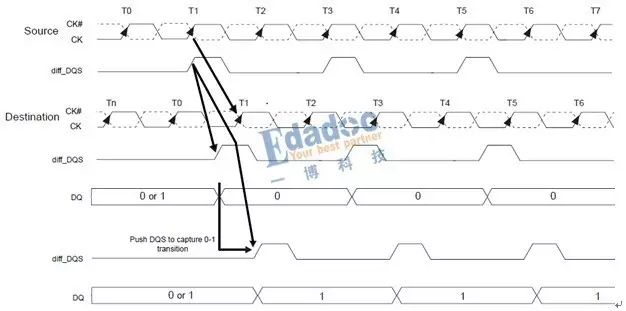

因此write leveling應運而生,這也是為什么在DDR3里面使用fly_by結構后數據組可以不用和時鐘信號去繞等長的原因,數據信號組與組之間也不用去繞等長,而在DDR2里面數據組還是需要和時鐘有較寬松的等長要求的。DDR3控制器調用Write leveling功能時,需要DDR3 SDRAM顆粒的反饋來調整DQS與CK之間的相位關系,具體方式如下圖一所示。

圖一、 Write leveling

Write leveling 是一個完全自動的過程。控制器(CPU或FPGA)不停的發送不同時延的DQS 信號,DDR3 SDRAM 顆粒在DQS-DQS#的上升沿采樣CK 的狀態,并通過DQ 線反饋給DDR3 控制器。控制器端反復的調整DQS-DQS#的延時,直到控制器端檢測到DQ 線上0 到1 的跳變(說明tDQSS參數得到了滿足),控制器就鎖住此時的延時值,此時便完成了一個Write leveling過程;同時在Leveling 過程中,DQS-DQS#從控制器端輸出,所以在DDR3 SDRAM 側必須進行端接;同理,DQ 線由DDR3 SDRAM顆粒側輸出,在控制器端必須進行端接;

需要注意的是,并不是所有的DDR3控制器都支持write leveling功能,所以也意味著不能使用Fly_by拓撲結構,通常這樣的主控芯片會有類似以下的描述:

二、DBI功能與POD電平

DBI的全稱是Data Bus Inversion數據總線反轉/倒置,它與POD電平密不可分,它們也是DDR4區別于DDR3的主要技術突破。

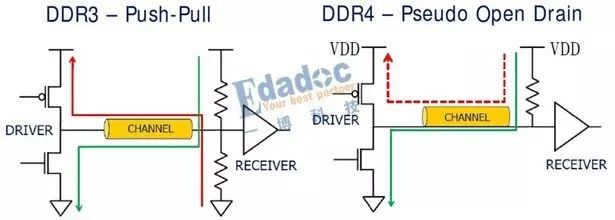

POD電平的全稱是Pseudo Open-Drain 偽漏極開路,其與DDR3對比簡單的示例電路如下圖二所示。

圖二 POD示意電路

從中可以看到,當驅動端的上拉電路導通,電路處于高電平時(也即傳輸的是“1”),此時兩端電勢差均等,相當于回路上沒有電流流過,但數據“1”還是照樣被傳輸,這樣的設計減少了功率消耗。

正是由于POD電平的這一特性,DDR4設計了DBI功能。當一個字節里的“0”比特位多于“1”時,可以使能DBI,將整個字節的“0”和“1”反轉,這樣“1”比“0”多,相比原(反轉前)傳輸信號更省功耗,如下表一所示。

表一 DBI示例

以上就是DDRx的一些主要的關鍵技術介紹,可以用如下表二所示來總結下DDRx的特性對比。

表二 DDRx SDRAM特性對比

審核編輯:劉清

-

控制器

+關注

關注

112文章

16350瀏覽量

177938 -

DDR3

+關注

關注

2文章

276瀏覽量

42257 -

DDR4

+關注

關注

12文章

321瀏覽量

40790 -

SDRAM控制器

+關注

關注

0文章

28瀏覽量

8138 -

dqs

+關注

關注

0文章

7瀏覽量

2281

原文標題:技術分享 | DDRx的關鍵技術介紹

文章出處:【微信號:Ithingedu,微信公眾號:安芯教育科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DDR4與DDR3的不同之處 DDR4設計與仿真案例

ddr3及ddr4的差異對比

ddr4和ddr3內存的區別,可以通用嗎

SDRAM,DDR3,DDR2,DDR4,DDR1的區別對比及其特點分析

DDR4相比DDR3的變更點

DDR,DDR2,DDR3,DDR4,LPDDR區別

PI2DDR3212和PI3DDR4212在DDR3/DDR4中應用

介紹DDR3和DDR4最關鍵的一些技術

介紹DDR3和DDR4最關鍵的一些技術

評論