2001年,英特爾公布了第三代I/O技術(shù)——3GIO技術(shù)(后更名為PCI Express,即PCIe),以高性能、高擴(kuò)展性、高可靠性及出色的兼容性取代了包括AGP和PCI在內(nèi)所有的內(nèi)部總線并且不斷升格。例如,2019年5月底公布的PCIe 5.0,其以32Gb/s的單通道帶寬與32GT/s(Giga Transmission per second)每通道數(shù)據(jù)傳輸速率,滿足了現(xiàn)今絕大多數(shù)的需求。但應(yīng)對數(shù)據(jù)TB級增長、異構(gòu)計算大行其道的當(dāng)下,PCIe在內(nèi)存使用效率、延遲和數(shù)據(jù)吞吐量等方面,已經(jīng)面臨壓力。

二十年后,在如今這個數(shù)據(jù)爆炸式增長,異構(gòu)計算大行其道的當(dāng)下,曾經(jīng)的“未來之星“PCI-e 已經(jīng)開始出現(xiàn)后繼無人的現(xiàn)象,無法成為 CPU、GPU、FPGA 以及其他 AI 計算設(shè)備之間溝通的橋梁。為了達(dá)到最佳的計算效果,我們越來越期待一種以內(nèi)存為中心的、富有變革性的新技術(shù)出現(xiàn),基于PCI-e協(xié)議的CXL技術(shù)便在此環(huán)境下出世。

2019年,英特爾推出的CXL技術(shù)似乎殺出了重圍。短短幾年時間,CXL便成為業(yè)界公認(rèn)的先進(jìn)設(shè)備互聯(lián)標(biāo)準(zhǔn),其最為強(qiáng)勁的競爭對手Gen-Z、OpenCAPI都紛紛退出了競爭,并將Gen-Z協(xié)議、OpenCAPI協(xié)議轉(zhuǎn)讓給CXL。

1、**什么是CXL?**

CXL全稱為Compute Express Link,作為一種全新的開放式互聯(lián)技術(shù)標(biāo)準(zhǔn),其能夠讓CPU與GPU、FPGA或其他加速器之間實現(xiàn)高速高效的互聯(lián),從而滿足高性能異構(gòu)計算的要求,并且其維護(hù)CPU內(nèi)存空間和連接設(shè)備內(nèi)存之間的一致性。總體而言,其優(yōu)勢高度概括在極高兼容性和內(nèi)存一致性兩方面上。

** 2、CXL 協(xié)議**

CXL 標(biāo)準(zhǔn)定義了 3 個協(xié)議,這些協(xié)議在通過標(biāo)準(zhǔn) PCIe 5.0 PHY 以 32 GT/s 傳輸之前一起動態(tài)復(fù)用:

CXL.io 協(xié)議本質(zhì)上是經(jīng)過一定改進(jìn)的 PCIe 5.0 協(xié)議,用于初始化、鏈接、設(shè)備發(fā)現(xiàn)和列舉以及寄存器訪問。它為 I/O 設(shè)備提供了非一致的加載/存儲接口。

CXL.cache 協(xié)議定義了主機(jī)和設(shè)備之間的交互,允許連接的 CXL 設(shè)備使用請求和響應(yīng)方法以極低的延遲高效地緩存主機(jī)內(nèi)存。

CXL.mem 協(xié)議提供了主機(jī)處理器,可以使用加載和存儲命令訪問設(shè)備連接的內(nèi)存,此時主機(jī) CPU 充當(dāng)主設(shè)備,CXL 設(shè)備充當(dāng)從屬設(shè)備,并且可以支持易失性和持久性存儲器架構(gòu)。

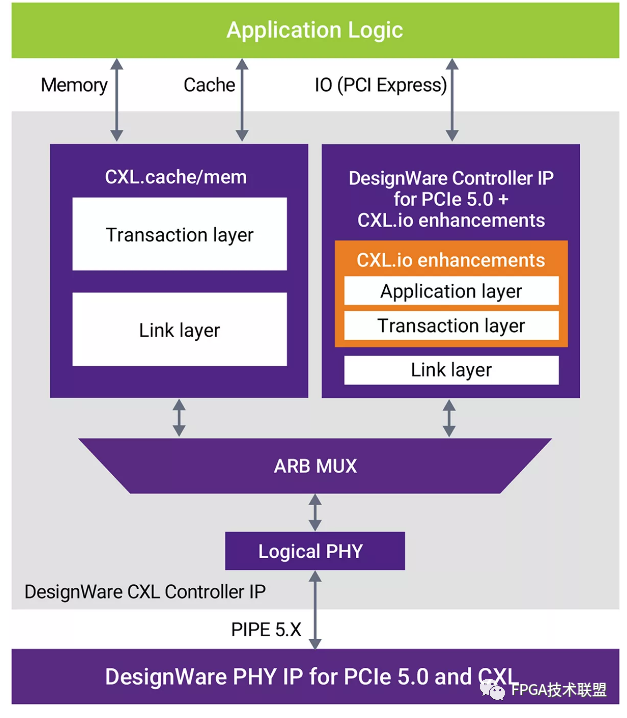

如圖 1 所示,CXL.cache 和 CXL.mem 合并且共享一個公共鏈路和事務(wù)層,而 CXL.io 有自己的鏈路和事務(wù)層。

三個協(xié)議產(chǎn)生的數(shù)據(jù)都通過仲裁和多路復(fù)用 (ARB/MUX) 模塊一起動態(tài)復(fù)用,然后被移交到 PCIe 5.0 PHY,進(jìn)而以 32GT/s 的速度進(jìn)行傳輸。ARB/MUX 在 CXL 鏈路層(CXL.io 和 CXL.cache/mem)發(fā)出的請求之間進(jìn)行仲裁,并根據(jù)仲裁結(jié)果復(fù)用數(shù)據(jù),仲裁結(jié)果使用加權(quán)循環(huán)仲裁,權(quán)重由主機(jī)設(shè)置。ARB/MUX 還處理鏈路層發(fā)出的功耗狀態(tài)轉(zhuǎn)換請求,向物理層創(chuàng)建實現(xiàn)有序降耗操作的單個請求。

CXL 通過固定寬度的 528 位微片傳輸數(shù)據(jù),該微片由四個 16 字節(jié)時隙組成,并添加了兩個字節(jié) CRC:(4 x 16 + 2 = 66 字節(jié)= 528 位)。插槽采用多種格式定義,可專用于 CXL.cache 協(xié)議或 CXL.mem 協(xié)議。片頭定義了插槽格式,并攜帶允許事務(wù)層將數(shù)據(jù)正確路由到預(yù)期協(xié)議的信息。

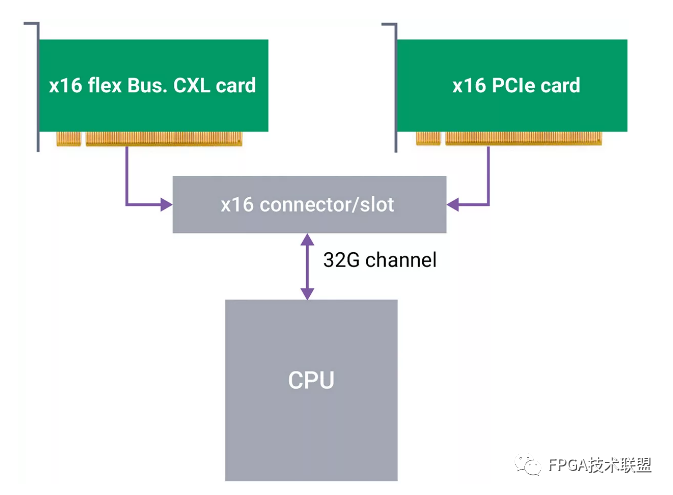

由于 CXL 使用 PCIe 5.0 PHY 和電氣元件,它可以有效地插入到任何可以通過 Flex Bus 使用 PCIe 5.0 的系統(tǒng)中。Flex Bus 是一個靈活的高速端口,可以靜態(tài)配置為支持 PCIe 或 CXL。圖 2 舉例顯示了 Flex Bus 鏈路。這種方法使 CXL 系統(tǒng)能夠利用 PCIe 重定時器;但是,目前 CXL 僅定義為直連 CPU 鏈路,因此無法利用 PCIe 交換機(jī)。隨著標(biāo)準(zhǔn)的逐步完善,交換功能可能會被添加到標(biāo)準(zhǔn)中;如果是這樣,則需要創(chuàng)建新的 CXL 交換機(jī)。

3、CXL 設(shè)備類型

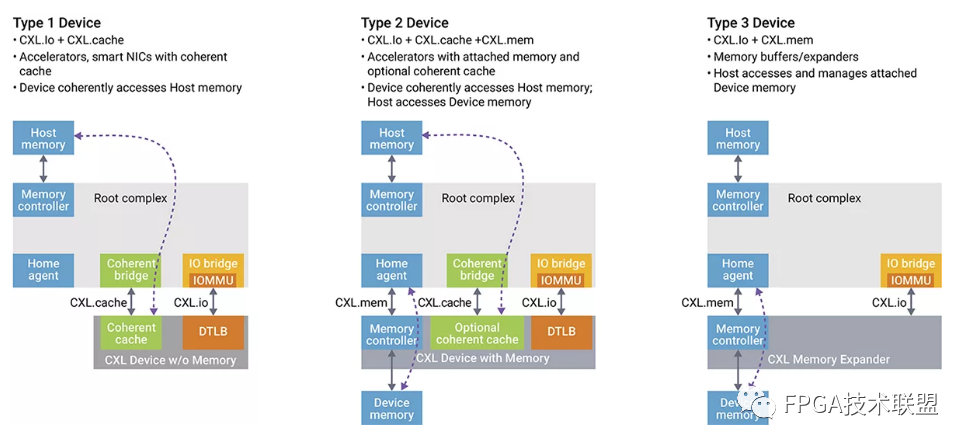

CXL.io 協(xié)議用于初始化和鏈接,所以必須獲得所有 CXL 設(shè)備的支持,如果 CXL.io 協(xié)議發(fā)生故障,鏈接就無法運(yùn)行。其他兩個協(xié)議的不同組合產(chǎn)生了總共三種被定義并受 CXL 標(biāo)準(zhǔn)支持的獨(dú)特 CXL 設(shè)備類型。

圖 3 顯示了三種已定義的 CXL 設(shè)備類型及其相應(yīng)的協(xié)議、典型應(yīng)用以及支持的存儲器訪問類型。

對于 2 型設(shè)備,CXL 定義了兩個一致性“偏置”,用于控制 CXL 對主機(jī)和設(shè)備連接存儲器之間的一致性數(shù)據(jù)的處理方式。偏置模式指主機(jī)偏置和設(shè)備偏置,并且操作模式可以根據(jù)需要發(fā)生改變,從而在鏈路操作期間優(yōu)化給定任務(wù)的性能。

2 型設(shè)備(例如,加速器)處理提交給主機(jī)的工作時間及其后續(xù)完成之間的數(shù)據(jù)時,設(shè)備偏置模式用于確保設(shè)備可以直接訪問其設(shè)備連接的存儲器,而無需與主機(jī)的一致性引擎通信。因此,設(shè)備可保證主機(jī)沒有緩存線路。這為設(shè)備提供了最優(yōu)的延遲性能,使得設(shè)備偏置成為加速器執(zhí)行工作的主要操作模式。主機(jī)處于設(shè)備偏置模式時,主機(jī)仍然可以訪問設(shè)備連接的存儲器,但性能卻不是最優(yōu)。

主機(jī)偏置模式優(yōu)先考慮從主機(jī)到設(shè)備連接存儲器的一致性訪問。該模式通常在工作提交期間使用,此時數(shù)據(jù)會從主機(jī)寫入設(shè)備連接的存儲器,而且在主機(jī)將數(shù)據(jù)從設(shè)備連接的存儲器中導(dǎo)出后,可使用該模式完成工作。在主機(jī)偏置模式下,設(shè)備連接的存儲器對于設(shè)備而言就像主機(jī)連接的存儲器一樣,如果設(shè)備需要訪問,就通過一條發(fā)送到主機(jī)的請求進(jìn)行處理。

可以使用軟件或硬件,通過軟件輔助和硬件自治這兩種受支持的模式管理機(jī)制來控制偏置模式。加速器或其他 2 型設(shè)備可以選擇偏置模式,如果兩種模式均未選擇,則系統(tǒng)默認(rèn)為主機(jī)偏置模式,這樣就必須通過主機(jī)路由對設(shè)備連接存儲器進(jìn)行所有訪問。偏置模式可以使用 4KB 頁面的顆粒度進(jìn)行更改,并通過 2 型設(shè)備中執(zhí)行的偏置表進(jìn)行跟蹤。

CXL 標(biāo)準(zhǔn)的一個重要特征是一致性協(xié)議是不對稱的。Home 緩存代理僅停留在主機(jī)中。因此,主機(jī)控制存儲器的緩存,從而解決連接的 CXL 設(shè)備請求的給定地址的整個系統(tǒng)的一致性問題。這完全不同于正在使用的現(xiàn)有專有和公開的一致性協(xié)議,特別是那些用于 CPU 到 CPU 連接的協(xié)議,因為它們通常是對稱的,會使得所有互連設(shè)備都變得對等。

雖然這樣有一些優(yōu)點,但是對稱的高速緩存一致性協(xié)議更加復(fù)雜,并且所有設(shè)備都必須處理由此產(chǎn)生的復(fù)雜性。具有不同架構(gòu)的設(shè)備可以采用不同的方法來實現(xiàn)在微架構(gòu)級別優(yōu)化的一致性,而這一情況可能會為實現(xiàn)廣泛的行業(yè)采用增加難度。通過使用主機(jī)控制的非對稱方法,可以將不同的 CPU 和加速器輕松納入新興 CXL 生態(tài)系統(tǒng)。

** 4、CXL的未來**

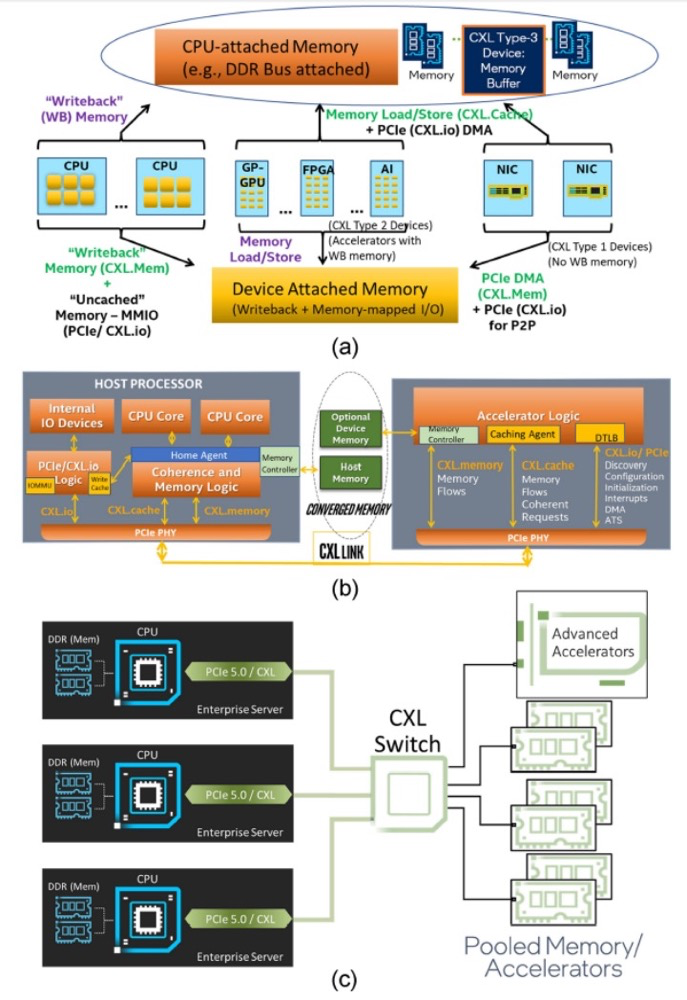

可以設(shè)想在具有內(nèi)存一致性的大型系統(tǒng)中同時使用多個協(xié)議來處理 CPU 到 CPU、CPU 到連接設(shè)備以及更長距離的機(jī)箱到機(jī)箱要求。目前,CXL 致力于為服務(wù)器提供經(jīng)過優(yōu)化的解決方案。CXL 固有的不對稱性意味著它可能不適用于 CPU 到 CPU 或加速器到加速器的連接。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603009 -

cpu

+關(guān)注

關(guān)注

68文章

10854瀏覽量

211587 -

gpu

+關(guān)注

關(guān)注

28文章

4729瀏覽量

128890

發(fā)布評論請先 登錄

相關(guān)推薦

關(guān)于Gen-Z語義存儲(memory-semantic)體系架構(gòu)探討

如何創(chuàng)建最佳的網(wǎng)絡(luò)和架構(gòu) 一文解析Gen-Z架構(gòu)

一窺CXL協(xié)議

CXL事務(wù)層的結(jié)構(gòu)是由哪些部分組成的

CXL內(nèi)存協(xié)議介紹

DirectCXL內(nèi)存分解原型設(shè)計實現(xiàn)

一文詳解CXL鏈路層格式的定義

DesignWare CXL為SoC提供優(yōu)化的多芯片IP堆棧

Saniffer開放實驗室?guī)齑娌⑻峁y試工具

瀾起科技發(fā)布全球首款CXL? 內(nèi)存擴(kuò)展控制器芯片

一文讀懂CXL協(xié)議

CXL協(xié)議和標(biāo)準(zhǔn)介紹, CXL2.0和3.0有什么新功能?

SMART Modular 世邁科技推出高性能服務(wù)器專用全新CXL? 內(nèi)存擴(kuò)充卡系列

打造異構(gòu)計算新標(biāo)桿!國數(shù)集聯(lián)發(fā)布首款CXL混合資源池參考設(shè)計

如何利用CXL協(xié)議實現(xiàn)高效能的計算架構(gòu)

什么是CXL協(xié)議

什么是CXL協(xié)議

評論