點(diǎn)擊藍(lán)字關(guān)注我們

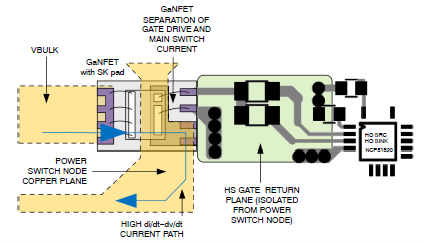

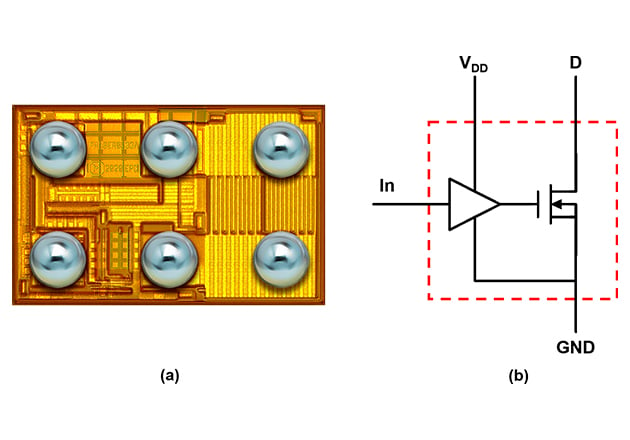

本設(shè)計(jì)文檔其余部分引用的布線示例將使用含有源極開爾文連接引腳的 GaNFET 封裝。

VDD 電容

VDD 引腳應(yīng)有兩個(gè)盡可能靠近 VDD 引腳放置的陶瓷電容。如圖 7 所示,較低值的高頻旁路電容(通常為 0.1 μF)應(yīng)與第二個(gè)并聯(lián)電容(1 μF)一起放在最靠近 VDD 引腳的位置。

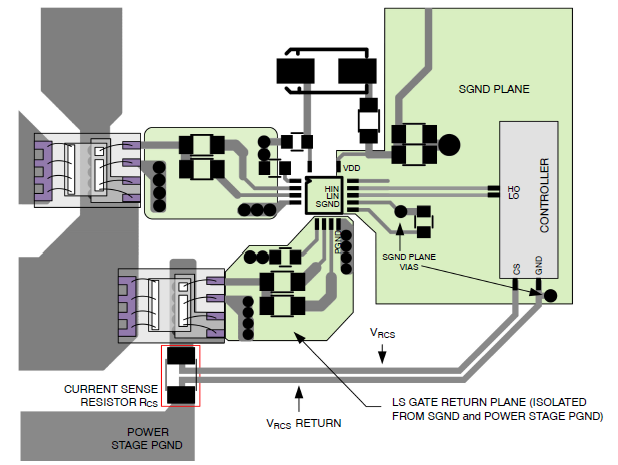

圖1. NCP51820 VDD 電容布局和布線

所有走線須盡可能短而直。可以使用過孔,因?yàn)?VDD 電流相對(duì)較低。SGND 返回平面對(duì)于其屏蔽特性以及讓所有信號(hào)側(cè)接地回路保持相同電位很有好處,建議使用。SGND 平面位于第 2 層,使其靠近信號(hào)側(cè)元器件和 NCP51820。所有信號(hào)側(cè)元器件都放在 SGND 平面上,并通過過孔連接。VDD 引腳和 VDD 電容之間應(yīng)建立直接連接,最好使用過孔作為 SGND 平面的返回連接。

如圖1所示,兩個(gè) VDD 電容的接地連接并在一起,并通過單個(gè)過孔連接到 SGND 平面。如果可能,最好使用不間斷的實(shí)心 SGND 接地平面,以免形成接地環(huán)路。建議將“安靜”的 SGND 平面延伸到 NCP51820 下方,以幫助屏蔽驅(qū)動(dòng)器 IC,使其不受噪聲影響。注意在圖1中,SGND 平面沒有延伸到 NCP51820 柵極驅(qū)動(dòng)器輸出引腳下方。這是有意為之,目的是避免噪聲從柵極驅(qū)動(dòng) di/dt 峰值拉電流和灌電流耦合到 SGND 平面中。

VBST 電容和二極管、

VDDH 和 VDDL 旁路電容

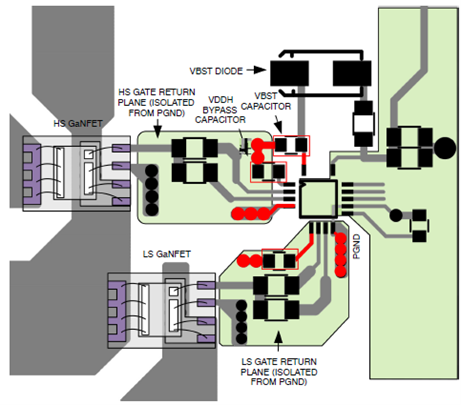

VBST 電容應(yīng)盡可能靠近 VBST 引腳放置。VBST 電容返回引腳應(yīng)連接到 GaNFET 的驅(qū)動(dòng)器 SW 引腳、VDDH 返回引腳和源極開爾文引腳。每個(gè)連接都是通過過孔接到 HS 柵極返回平面,如圖2所示。務(wù)必注意,不應(yīng)從功率級(jí)開關(guān)節(jié)點(diǎn)接回到 NCP51820。請(qǐng)勿將 VBST 電容連接到功率級(jí)開關(guān)節(jié)點(diǎn)。“開關(guān)節(jié)點(diǎn)”的唯一連接是通過 HS GaNFET 源極開爾文引腳。

HS 柵極返回平面的設(shè)計(jì)應(yīng)注意,不得與功率級(jí)開關(guān)節(jié)點(diǎn)發(fā)生重疊或相互作用。同樣,LS 柵極返回平面的設(shè)計(jì)應(yīng)注意,不得與 LS GaNFET 電源地發(fā)生重疊或相互作用。請(qǐng)勿將 SGND 平面放在 VBST 二極管或 VBST 電容下方,因?yàn)?VBST 二極管的陰極上存在高 dV/dt,它可能會(huì)將噪聲注入 SGND 平面。

圖2. NCP51820 VBST 電容和二極管、VDDH 和 VDDL 電容

VDDH 電容應(yīng)盡可能靠近 VDDH 引腳放置。如圖2所示,VDDH 電容返回引腳應(yīng)通過過孔連接到 HS 柵極返回平面(與 VBST 電容共用一個(gè)雙過孔連接)。

VDDL 電容應(yīng)盡可能靠近 VDDL 引腳放置。如圖2所示,VDDL 電容返回引腳應(yīng)通過過孔連接到 LS 柵極返回平面。VDDL 電容返回引腳必須連接到驅(qū)動(dòng)器上的 PGND 引腳。VDDL 電容返回引腳通過過孔連接到 LS 柵極返回平面,該平面也通過過孔連接到驅(qū)動(dòng)器 PGND 引腳。

由于柵極驅(qū)動(dòng)電流峰值很高,并且為了降低過孔寄生電感,VBST、VDDH 和 VDDL 需要多個(gè)過孔。在此示例中,每個(gè) GaNFET 柵極返回連接使用四個(gè)過孔。這是一個(gè)合理的折衷考慮,一方面能在 NCP51820 柵極驅(qū)動(dòng)器返回引腳與 GaNFET 返回引腳之間獲得低阻抗連接,另一方面能保持實(shí)心返回平面和良好的屏蔽完整性。如果可能,最好使用導(dǎo)電材料填充的過孔,因?yàn)槠湎嚓P(guān)電感更低。

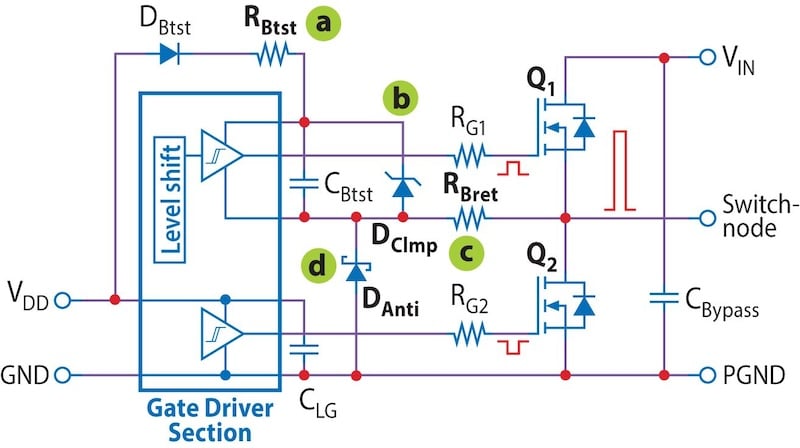

柵極驅(qū)動(dòng)布線

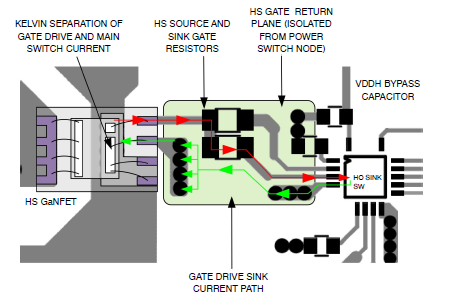

當(dāng) NCP51820 向 HS GaNFET 柵極提供電流時(shí),該柵極電流來自 VDDH 調(diào)節(jié)器旁路電容中儲(chǔ)存的電荷。如圖3所示,拉電流流經(jīng) HO 驅(qū)動(dòng)器源極阻抗和柵源電阻,進(jìn)入 GaNFET 柵極。然后,電流從 GaNFET 源極開爾文引腳返回,又回到 VDDH 旁路電容。

圖3. 高壓側(cè)柵極驅(qū)動(dòng)拉電流

當(dāng) NCP51820 從 HS GaNFET 吸收電流時(shí),該電流來自柵源電容中儲(chǔ)存的能量。如圖4所示,灌電流從 HS GaNFET 柵極流出,經(jīng)過柵極灌電流電阻、HO SINK 驅(qū)動(dòng)器阻抗和 SW 引腳,回到 GaNFET 源極開爾文引腳。

圖4. 高壓側(cè)柵極驅(qū)動(dòng)灌電流

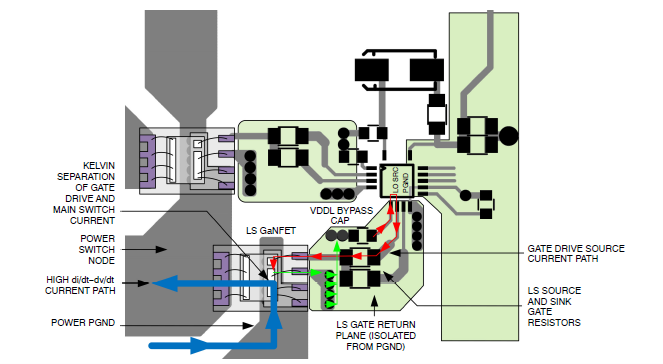

當(dāng) NCP51820 向 LS GaNFET 柵極提供電流時(shí),該柵極電流來自 VDDL 調(diào)節(jié)器旁路電容中儲(chǔ)存的電荷。如圖5所示,拉電流流經(jīng) LO 驅(qū)動(dòng)器源極阻抗和柵源電阻,進(jìn)入 GaNFET 柵極。然后,電流從 GaNFET 源極開爾文引腳返回,又回到 VDDL 旁路電容。

圖5. 低壓側(cè)柵極驅(qū)動(dòng)拉電流

當(dāng) NCP51820 從 LS GaNFET 吸收電流時(shí),該電流來自柵源電容中儲(chǔ)存的能量。如圖6所示,灌電流從 LS GaNFET 柵極流出,經(jīng)過柵極灌電流電阻、LO SINK 驅(qū)動(dòng)器阻抗和 PGND 引腳,回到 GaNFET 源極開爾文引腳。

圖6. 低壓側(cè)柵極驅(qū)動(dòng)灌電流

GaNFET 能以高開關(guān)頻率工作,漏源切換期間會(huì)出現(xiàn)高 dV/dt(100 V/ns 及更高)。GaN 的柵源導(dǎo)通閾值較低 (<2 V),因此柵極驅(qū)動(dòng)拉電流和灌電流路徑必須盡可能保持短而直,以減輕走線寄生電感的不良影響。柵極環(huán)路中的過大寄生電感可能導(dǎo)致超過柵源閾值電壓的柵極振蕩或高頻振鈴。柵極驅(qū)動(dòng)和返回路徑中的過孔只有在絕對(duì)必要時(shí)才應(yīng)使用。最好使用導(dǎo)電材料填充的過孔,因?yàn)槊總€(gè)這種過孔的電感要小得多。在柵極電阻和相關(guān)布線下方使用載流返回平面,以在拉電流和灌電流路徑正下方提供一個(gè)返回路徑,有助于減少環(huán)路電感。

NCP51820 高壓側(cè)和低壓側(cè)驅(qū)動(dòng)在內(nèi)部相互隔離。對(duì)于高壓端,SW 引腳必須與功率開關(guān)節(jié)點(diǎn)隔離,以防止開關(guān)噪聲注入柵極驅(qū)動(dòng)路徑,并且它只能連接到高壓側(cè) GaNFET 上的 SK 引腳。源極開爾文引腳和電源引腳之間的開爾文連接是 NCP51820 SW 引腳和功率級(jí)開關(guān)節(jié)點(diǎn)之間的唯一電氣連接,如圖3和圖4所示。同樣,低壓側(cè)柵極驅(qū)動(dòng)的布線應(yīng)使 NCP51820 PGND 引腳與功率級(jí) PGND 隔離,并且只能連接到低壓側(cè) GaNFET 的 SK。設(shè)計(jì)目標(biāo)是避免電源 PGND 噪聲注入低壓側(cè)柵極驅(qū)動(dòng)路徑。在低壓側(cè) GaNFET 內(nèi)部,SK 引腳和電源引腳之間存在開爾文連接,它是 NCP51820 PGND 和電源 PGND 之間的實(shí)際連接,如圖5和圖6所示。

在設(shè)計(jì)允許的范圍內(nèi),HS 和 LS 柵極走線的長(zhǎng)度應(yīng)盡可能相等。這有助于確保兩個(gè) GaNFET 具有相似的柵極驅(qū)動(dòng)阻抗。高壓側(cè)和低壓側(cè) GaNFET 交錯(cuò)對(duì)齊具有雙重作用:一是使得柵極驅(qū)動(dòng)布線接近對(duì)稱且等距,二是允許使用更大、更高電流的功率開關(guān)節(jié)點(diǎn)銅觸點(diǎn)。

最好將 HS 和 LS 返回平面分配至第 2 層,并將它們直接放置在柵極驅(qū)動(dòng)電阻和走線下方,這樣有助于減少柵極驅(qū)動(dòng)環(huán)路電感。對(duì)于高壓側(cè) GaNFET,由于 VDDH 旁路電容返回引腳和 NCP51820 SW 引腳被 HO 拉電流和 HO 灌電流走線分開,因此可以使用無填充的過孔通過 HS 柵極返回平面連接到 GaNFET 的源極開爾文引腳。建議使用多個(gè)過孔以幫助減少過孔電感。請(qǐng)注意,柵極驅(qū)動(dòng)電流路徑與功率開關(guān)節(jié)點(diǎn)電流路徑隔離,盡可能避免主電流路徑中的噪聲注入柵極驅(qū)動(dòng)電流路徑。

對(duì)于低壓側(cè) GaNFET,由于 VDDL 旁路電容返回引腳和 NCP51820 PGND 引腳被 LO 拉電流和 LO 灌電流走線分開,因此可以使用無填充的過孔通過 LS 柵極返回平面連接到 GaNFET 的源極開爾文引腳。建議使用多個(gè)過孔以幫助減少過孔寄生電感。請(qǐng)注意,柵極驅(qū)動(dòng)電流路徑與電源 PGND 電流路徑隔離,盡可能避免主電流路徑中的噪聲注入柵極驅(qū)動(dòng)電流路徑。

信號(hào)接地 (SGND) 和電源接地 (PGND)

SGND 是所有內(nèi)部控制邏輯和數(shù)字輸入接地。在內(nèi)部,SGND 和 PGND 引腳相互隔離。PGND 用作低壓側(cè)柵極驅(qū)動(dòng)和返回基準(zhǔn)。

對(duì)于半橋電源拓?fù)浠蛉魏问褂?a target="_blank">電流檢測(cè)變壓器的應(yīng)用,NCP51820 SGND 和 PGND 應(yīng)在 PCB 上連接在一起。在此類應(yīng)用中,建議在 PCB 上通過一條低阻抗短走線將 SGND 和 PGND 引腳連接在一起,并且讓它們盡可能靠近 NCP51820。NCP51820 正下方是建立 SGND 至 PGND 連接的理想位置,如圖7所示。

圖7. PGND 至 SGND,0 Ω 單點(diǎn)連接

對(duì)于低功耗應(yīng)用,例如有源箝位反激式或正激式轉(zhuǎn)換器,通常會(huì)在低壓側(cè) GaN FET 源極支路中使用一個(gè)電流檢測(cè)電阻 RCS。在此類應(yīng)用中,NCP51820 PGND 和 SGND 引腳不得在 PCB 上連接,因?yàn)?RCS 會(huì)通過此連接短路。NCP51820 低壓側(cè)驅(qū)動(dòng)電路能夠承受 -3.5 V 至 +3.5 V 的共模電壓。大多數(shù)電流檢測(cè)電壓信號(hào)小于 1 V,因此低壓側(cè)驅(qū)動(dòng)級(jí)很容易“浮動(dòng)”到電流檢測(cè)所產(chǎn)生的電壓 VRCS 以上。如圖8所示,整個(gè)低壓側(cè)柵極驅(qū)動(dòng)浮動(dòng)到 VRCS 以上。這一點(diǎn)很重要,因?yàn)樗_保柵極驅(qū)動(dòng)幅度不會(huì)有損失,因此完整的 VDDL 電壓會(huì)出現(xiàn)在低壓側(cè) GaN FET 柵源端子。

按照上文所述布置電路時(shí),連接到 NCP51820 HIN 和 LIN 的控制器 HO/LO 路徑必須返回到控制器 GND 以形成完整電路。因此,NCP51820 SGND 和控制器 GND 必須相連。這是通過使用過孔將 NCP51820 SGND 和控制器 GND 連接到 SGND 平面來實(shí)現(xiàn)的,如圖 14 所示。SGND 平面僅用于信號(hào)和信號(hào)側(cè) VDD 返回,也會(huì)充當(dāng)信號(hào)的屏蔽層。VRCS 返回引腳還必須連接到控制器 GND,這應(yīng)該使用單條低阻抗走線來完成,該走線應(yīng)盡可能靠近 VRCS 走線(或位于其下方)。這會(huì)將功率級(jí) PGND 單點(diǎn)連接到 SGND,并將功率級(jí) PGND 上的高 dV/dt 和 di/dt 與 SGND 平面隔離開來。

圖8. LS 柵極返回隔離和 VRCS 連接

開關(guān)性能驗(yàn)證

在利用 NCP51820 驅(qū)動(dòng) GaNFET 的半橋功率級(jí)布局中使用了本文介紹的 PCB 設(shè)計(jì)技術(shù)。

圖9. 650 V,18 A,HEMT,GaNFET,350 V,10 APK

圖9顯示了驅(qū)動(dòng)兩個(gè) 650 V、18 A、90 mΩ GaNFET 的穩(wěn)態(tài)波形。通道 1(黃色)是高壓側(cè)柵源電壓,通道 2(紅色)是低壓側(cè)柵源電壓,通道 3(藍(lán)色)是開關(guān)節(jié)點(diǎn)電壓(低壓側(cè) GaN VDS),通道 4(綠色)是電感電流。高壓側(cè)柵源電壓(通道 1,黃色)顯示存在輕微過沖和欠沖,這是使用高壓探針測(cè)量低壓浮動(dòng)信號(hào)(在柵極和功率開關(guān)節(jié)點(diǎn)之間測(cè)量)的附帶結(jié)果。通道 2(紅色)顯示了柵源電壓的“更真實(shí)”測(cè)量結(jié)果,其中低壓側(cè) GaNFET 柵源電壓在柵極和 PGND 之間測(cè)得。可以看到,柵極驅(qū)動(dòng)邊沿非常銳利且干凈。同樣,開關(guān)節(jié)點(diǎn)電壓(通道 3,藍(lán)色)沒有振鈴、過沖或欠沖。

圖10. 600 V,26 A,HEMT,GIT,GaNFET,dV/dt = 75 V/ns,320 V,20 APK

圖10所示波形是驅(qū)動(dòng)兩個(gè) HEMT、GIT、600 V、26 A、56 mΩ GaNFET 的結(jié)果,其電流能力比圖9中使用的器件要高。要實(shí)現(xiàn)高 dV/dt,需要相當(dāng)大的漏極電流 ID。例如,所示測(cè)量是在 ID = 20 APK 下進(jìn)行的,導(dǎo)致實(shí)測(cè) VDS dV/dt = 75 V/ns。三角形峰值電感電流顯示為純直流,這是進(jìn)行此測(cè)量所需的時(shí)基 (2 ns/div) 造成的。VSW 波形的 100 V 欠沖是用于顯示高 dV/dt 的測(cè)量技術(shù)的結(jié)果,在開關(guān)節(jié)點(diǎn)上并不真正存在。

在高電壓、高頻率 PCB 設(shè)計(jì)中,為了成功運(yùn)用寬禁帶半導(dǎo)體,需要更好地了解寄生電感和電容的負(fù)面影響。透徹理解電氣返回平面、屏蔽、電流分離、隔離和精心布線的重要性,對(duì)于充分發(fā)揮 GaN 技術(shù)的性能優(yōu)勢(shì)至關(guān)重要。本文重點(diǎn)說明在利用 NCP51820 驅(qū)動(dòng)高速電源拓?fù)渲惺褂玫?GaN 功率開關(guān)設(shè)計(jì)中,實(shí)現(xiàn)成功設(shè)計(jì)必須采用的重要 PCB 設(shè)計(jì)準(zhǔn)則。這些技術(shù)已通過實(shí)測(cè)波形得到了驗(yàn)證,表明其能夠獲得出色的結(jié)果。

掃描下方二維碼填寫信息

獲取英文原版文檔

點(diǎn)個(gè)星標(biāo),茫茫人海也能一眼看到我

原文標(biāo)題:劃重點(diǎn) | 幾個(gè)氮化鎵GaN驅(qū)動(dòng)器PCB設(shè)計(jì)必須掌握的要點(diǎn)

文章出處:【微信公眾號(hào):安森美】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

安森美

+關(guān)注

關(guān)注

32文章

1674瀏覽量

91997

原文標(biāo)題:劃重點(diǎn) | 幾個(gè)氮化鎵GaN驅(qū)動(dòng)器PCB設(shè)計(jì)必須掌握的要點(diǎn)

文章出處:【微信號(hào):onsemi-china,微信公眾號(hào):安森美】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

第三代半導(dǎo)體氮化鎵(GaN)基礎(chǔ)知識(shí)

氮化鎵晶圓在劃切過程中如何避免崩邊

WBG 器件給柵極驅(qū)動(dòng)器電源帶來的挑戰(zhàn)

碳化硅 (SiC) 與氮化鎵 (GaN)應(yīng)用 | 氮化硼高導(dǎo)熱絕緣片

氮化鎵和砷化鎵哪個(gè)先進(jìn)

氮化鎵(GaN)技術(shù)的迅猛發(fā)展與市場(chǎng)潛力

氮化鎵(GaN)的最新技術(shù)進(jìn)展

集成柵極驅(qū)動(dòng)器的GaN ePower超快開關(guān)

調(diào)整MOSFET柵極驅(qū)動(dòng)器以用于GaN FETs

劃重點(diǎn) | 幾個(gè)氮化鎵GaN驅(qū)動(dòng)器PCB設(shè)計(jì)必須掌握的要點(diǎn)

劃重點(diǎn) | 幾個(gè)氮化鎵GaN驅(qū)動(dòng)器PCB設(shè)計(jì)必須掌握的要點(diǎn)

評(píng)論