1題目說明

在許多(較舊的)串行通信協議中,每個數據字節都與一個起始位和一個停止位一起發送,以幫助接收器從位流中分隔字節。一種常見的方案是使用一個起始位 (0)、8 個數據位和 1 個停止位 (1)。當沒有傳輸任何內容(空閑)時,該線路也處于邏輯 1。

設計一個有限狀態機,當給定比特流時,該機器將識別何時正確接收了字節。它需要識別起始位,等待所有 8 個數據位,然后驗證停止位是否正確。如果停止位沒有按預期出現,則 FSM 必須等到它找到停止位,然后才能嘗試接收下一個字節。

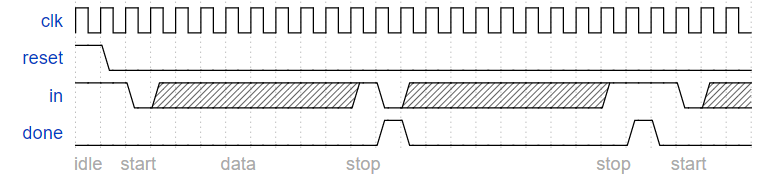

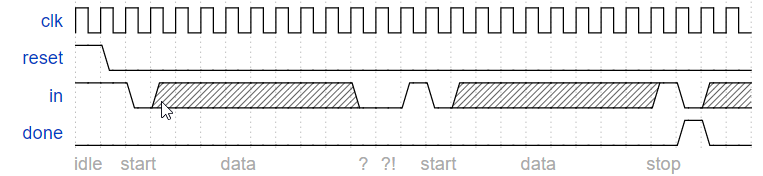

一些時序圖

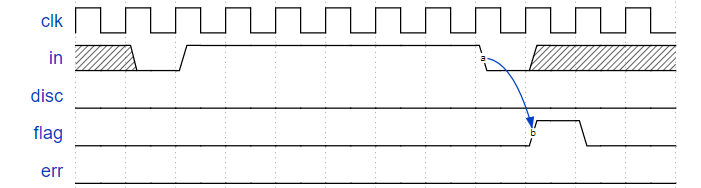

無錯誤:

未找到停止位。第一個字節被丟棄:

模塊端口聲明

moduletop_module( inputclk, inputin, inputreset,//Synchronousreset outputdone );

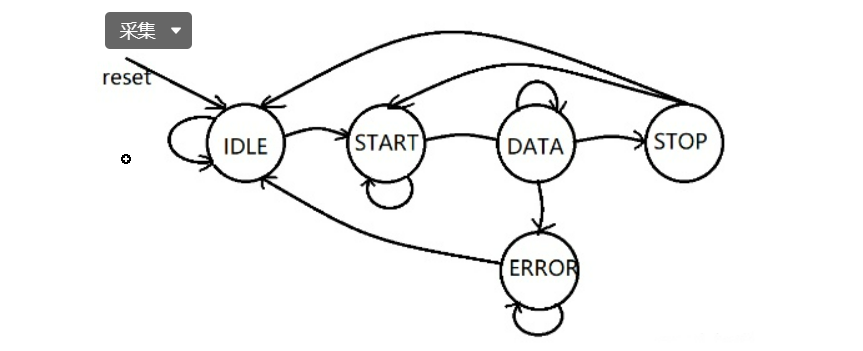

2題目解析

串口接收問題,題目沒給狀態圖,需要自己繪制:

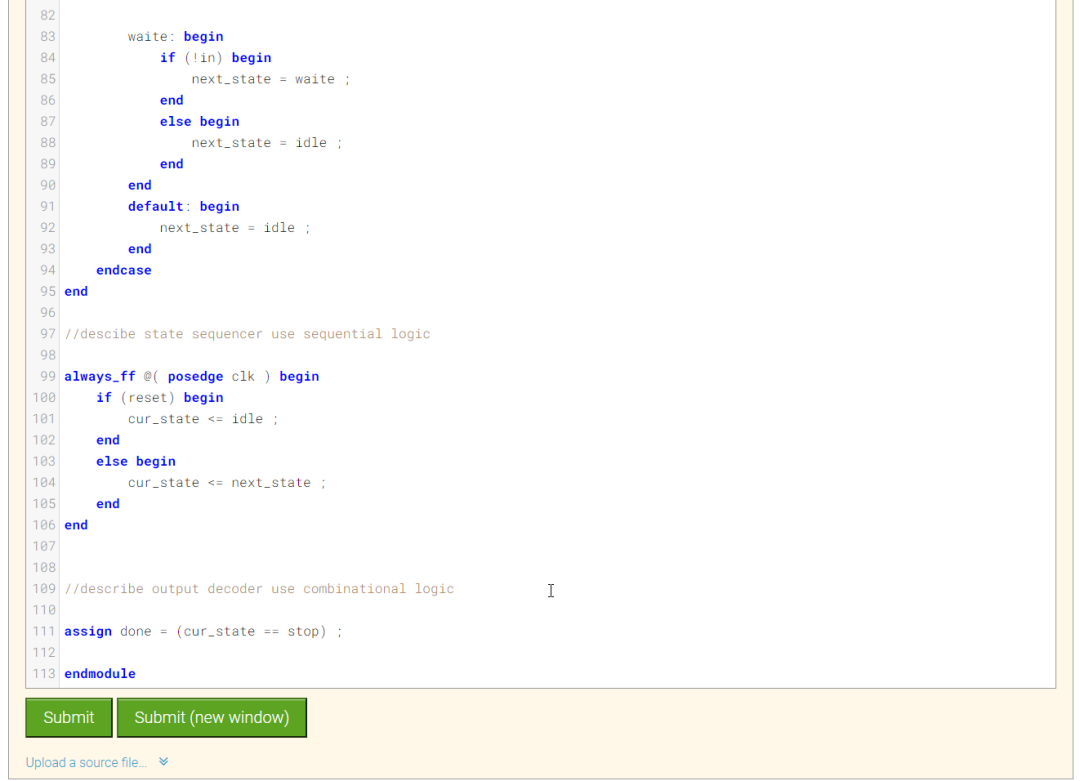

moduletop_module( inputlogicclk, inputlogicin, inputlogicreset,//Synchronousreset outputlogicdone ); //definestate typedefenumlogic[3:0]{idle=4'd0,start=4'd1, receive_1=4'd2,receive_2=4'd3, receive_3=4'd4,receive_4=4'd5, receive_5=4'd6,receive_6=4'd7, receive_7=4'd8,receive_8=4'd9, stop=4'd10,waite=4'd11 }state_def; state_defcur_state,next_state; varlogic[3:0]state_cout; //describestatetransitionlogicusecombinationallogic always_combbegin case(cur_state) idle:begin if(!in)begin next_state=start; end elsebegin next_state=idle; end end start:begin next_state=receive_1; end receive_1:begin next_state=receive_2; end receive_2:begin next_state=receive_3; end receive_3:begin next_state=receive_4; end receive_4:begin next_state=receive_5; end receive_5:begin next_state=receive_6; end receive_6:begin next_state=receive_7; end receive_7:begin next_state=receive_8; end receive_8:begin if(!in)begin next_state=waite; end elsebegin next_state=stop; end end stop:begin if(!in)begin next_state=start; end elsebegin next_state=idle; end end waite:begin if(!in)begin next_state=waite; end elsebegin next_state=idle; end end default:begin next_state=idle; end endcase end //descibestatesequencerusesequentiallogic always_ff@(posedgeclk)begin if(reset)begin cur_state<=?idle?; ????end???? ????else?begin ????????cur_state?<=?next_state?; ????end end //describe?output?decoder?use?combinational?logic assign?done?=?(cur_state?==?stop)?;? endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

Part3Problem 135-Fsm_serialdata

3題目說明

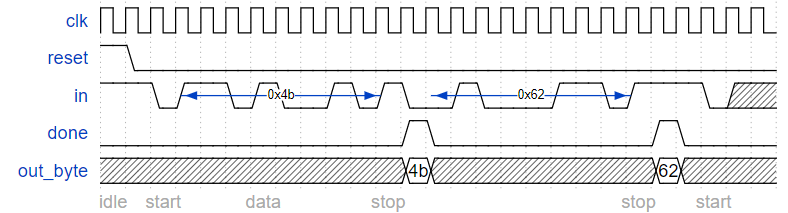

上一題用一個有限狀態機可以識別串行比特流中的字節何時被正確接收,添加一個數據路徑將輸出正確接收的數據字節。out_byte在done為1時需要有效,否則不關心。

請注意,串行協議首先發送最低有效位。

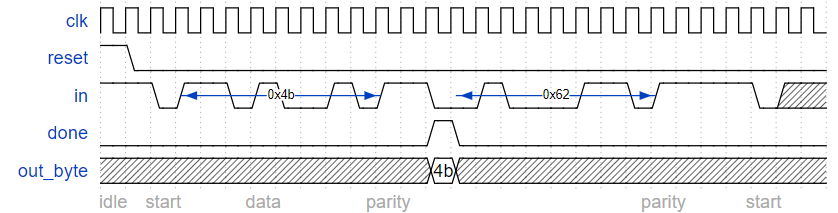

一些時序圖

無錯誤:

模塊端口聲明

moduletop_module( inputclk, inputin, inputreset,//Synchronousreset output[7:0]out_byte, outputdone );

4題目解析

狀態機與上題一致。

moduletop_module(

inputlogicclk,

inputlogicin,

inputlogicreset,//Synchronousreset

output[7:0]out_byte,

outputlogicdone

);

//definestate

typedefenumlogic[3:0]{idle=4'd0,start=4'd1,

receive_1=4'd2,receive_2=4'd3,

receive_3=4'd4,receive_4=4'd5,

receive_5=4'd6,receive_6=4'd7,

receive_7=4'd8,receive_8=4'd9,

stop=4'd10,waite=4'd11

}state_def;

state_defcur_state,next_state;

varlogic[3:0]state_cout;

//describestatetransitionlogicusecombinationallogic

always_combbegin

case(cur_state)

idle:begin

if(!in)begin

next_state=start;

end

elsebegin

next_state=idle;

end

end

start:begin

next_state=receive_1;

end

receive_1:begin

next_state=receive_2;

end

receive_2:begin

next_state=receive_3;

end

receive_3:begin

next_state=receive_4;

end

receive_4:begin

next_state=receive_5;

end

receive_5:begin

next_state=receive_6;

end

receive_6:begin

next_state=receive_7;

end

receive_7:begin

next_state=receive_8;

end

receive_8:begin

if(!in)begin

next_state=waite;

end

elsebegin

next_state=stop;

end

end

stop:begin

if(!in)begin

next_state=start;

end

elsebegin

next_state=idle;

end

end

waite:begin

if(!in)begin

next_state=waite;

end

elsebegin

next_state=idle;

end

end

default:begin

next_state=idle;

end

endcase

end

//descibestatesequencerusesequentiallogic

always_ff@(posedgeclk)begin

if(reset)begin

cur_state<=?idle?;

????end????

????else?begin

????????cur_state?<=?next_state?;

????end

end

//describe?output?decoder?use?combinational?logic

assign?done?=?(cur_state?==?stop)?;

assign?out_byte?=?done???out_bytes_temp?:?8'd0?;

var?logic?[7:0]?out_bytes_temp?;

always_ff?@(?posedge?clk?)?begin?

????if?(next_state?==?receive_1)?begin

????????out_bytes_temp[0]?<=?in?;

????end

????else?if?(next_state?==?receive_2)?begin

????????out_bytes_temp[1]?<=?in?;

????end

????else?if?(next_state?==?receive_3)?begin

????????out_bytes_temp[2]?<=?in?;

????end

????else?if?(next_state?==?receive_4)?begin

????????out_bytes_temp[3]?<=?in?;

????end?

????else?if?(next_state?==?receive_5)?begin

????????out_bytes_temp[4]?<=?in?;

????end

????else?if?(next_state?==?receive_6)?begin

????????out_bytes_temp[5]?<=?in?;

????end

????else?if?(next_state?==?receive_7)?begin

????????out_bytes_temp[6]?<=?in?;

????end

????else?if?(next_state?==?receive_8)?begin

????????out_bytes_temp[7]?<=?in?;

????end

????

end

endmodule

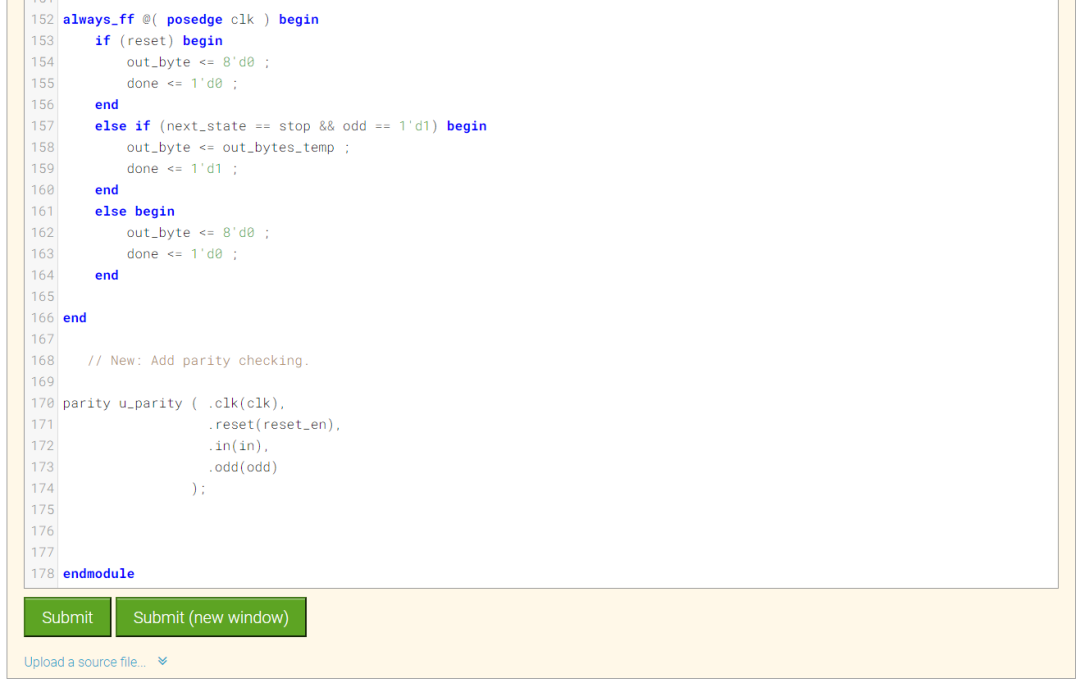

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

Part4Problem 136-Fsm_serialdp

5題目說明

這題仍然是在前面的基礎上進行進化,增添了奇偶校驗位。奇偶校驗(Parity Check)是一種校驗代碼傳輸正確性的方法。根據被傳輸的一組二進制代碼的數位中“1”的個數是奇數或偶數來進行校驗。采用奇數的稱為奇校驗,反之,稱為偶校驗。奇偶校驗是在傳輸中保障數據接收正確的常用方法,也是最初級的校驗方式。

該題采用的是奇校驗的方式,并且提供了奇偶校驗模塊。原本 start 和 stop 位之間的8 bit 變為了9 bit,新增的1 bit 為奇校驗位,從而使得這9 bit 中“1”的數量為奇數個,即題目中提供的奇偶校驗模塊輸出為1時表面數據正確,否則數據錯誤不予接收。波形圖如下所示。

moduleparity( inputclk, inputreset, inputin, outputregodd); always@(posedgeclk) if(reset)odd<=?0; ????????else?if?(in)?odd?<=?~odd; endmodule

請注意,串行協議首先發送最低有效位,然后在 8 個數據位之后發送奇偶校驗位。

一些時序圖

模塊端口聲明

moduletop_module( inputclk, inputin, inputreset,//Synchronousreset output[7:0]out_byte, outputdone );

6題目解析

moduletop_module(

inputlogicclk,

inputlogicin,

inputlogicreset,//Synchronousreset

output[7:0]out_byte,

outputlogicdone

);

//ModifyFSManddatapathfromFsm_serialdata

//definestate

typedefenumlogic[3:0]{idle=4'd0,start=4'd1,

receive_1=4'd2,receive_2=4'd3,

receive_3=4'd4,receive_4=4'd5,

receive_5=4'd6,receive_6=4'd7,

receive_7=4'd8,receive_8=4'd9,

stop=4'd10,waite=4'd11,parity=4'd12

}state_def;

state_defcur_state,next_state;

wirelogicodd;

//describestatetransitionlogicusecombinationallogic

always_combbegin

case(cur_state)

idle:begin

if(!in)begin

next_state=start;

end

elsebegin

next_state=idle;

end

end

start:begin

next_state=receive_1;

end

receive_1:begin

next_state=receive_2;

end

receive_2:begin

next_state=receive_3;

end

receive_3:begin

next_state=receive_4;

end

receive_4:begin

next_state=receive_5;

end

receive_5:begin

next_state=receive_6;

end

receive_6:begin

next_state=receive_7;

end

receive_7:begin

next_state=receive_8;

end

receive_8:begin

next_state=parity;

end

parity:begin

if(!in)begin

next_state=waite;

end

elsebegin

next_state=stop;

end

end

stop:begin

if(!in)begin

next_state=start;

end

elsebegin

next_state=idle;

end

end

waite:begin

if(!in)begin

next_state=waite;

end

elsebegin

next_state=idle;

end

end

default:begin

next_state=idle;

end

endcase

end

//descibestatesequencerusesequentiallogic

always_ff@(posedgeclk)begin

if(reset)begin

cur_state<=?idle?;

????end????

????else?begin

????????cur_state?<=?next_state?;

????end

end

//describe?output?decoder?use?combinational?logic

assign?reset_en?=?(reset?==?1'd1)?||?(next_state?==?stop)?||?(next_state?==?idle)?||?(next_state?==?start)?;

wire?logic?reset_en?;

var?logic?[7:0]?out_bytes_temp?;

always_ff?@(?posedge?clk?)?begin?

????if?(next_state?==?receive_1)?begin

????????out_bytes_temp[0]?<=?in?;

????end

????else?if?(next_state?==?receive_2)?begin

????????out_bytes_temp[1]?<=?in?;

????end

????else?if?(next_state?==?receive_3)?begin

????????out_bytes_temp[2]?<=?in?;

????end

????else?if?(next_state?==?receive_4)?begin

????????out_bytes_temp[3]?<=?in?;

????end?

????else?if?(next_state?==?receive_5)?begin

????????out_bytes_temp[4]?<=?in?;

????end

????else?if?(next_state?==?receive_6)?begin

????????out_bytes_temp[5]?<=?in?;

????end

????else?if?(next_state?==?receive_7)?begin

????????out_bytes_temp[6]?<=?in?;

????end

????else?if?(next_state?==?receive_8)?begin

????????out_bytes_temp[7]?<=?in?;

????end

????

end

always_ff?@(?posedge?clk?)?begin?

????if?(reset)?begin

????????out_byte?<=?8'd0?;

????????done?<=?1'd0?;

????end

????else?if?(next_state?==?stop?&&?odd?==?1'd1)?begin

????????out_byte?<=?out_bytes_temp?;

????????done?<=?1'd1?;

????end

????else?begin

????????out_byte?<=?8'd0?;

????????done?<=?1'd0?;

????end

????

end

???//?New:?Add?parity?checking.?

parity?u_parity?(?.clk(clk),

??????????????????.reset(reset_en),

??????????????????.in(in),

??????????????????.odd(odd)

????????????????);

????

endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

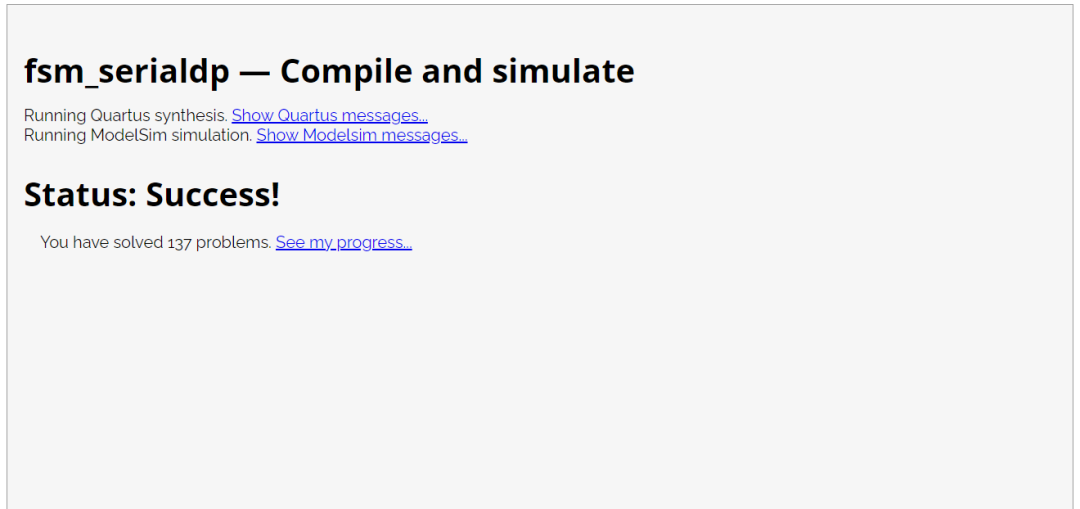

Part5Problem 137-Fsm_hdlc

7題目說明

同步HDLC幀涉及從連續的比特流中解碼尋找某一幀(即數據包)的開始和結束位置的位模式。(對位模式不太理解的可以參見https://zhuanlan.zhihu.com/p/46317118)。如果接收到連續的6個1(即01111110),即是幀邊界的“標志”。同時為了避免輸入的數據流中意外包含這個幀邊界“標志”,數據的發送方必須在數據中連續的5個1之后插入一個0,而數據的接收方必須將這個多余的0檢測出來并丟棄掉。同時,如果輸入檢測到了了連續7個或更多的1時,接收方還需要發出錯誤信號。

創建一個有限狀態機來識別這三個序列:

0111110 : 信號位需要被丟棄(disc)。

01111110:標記幀的開始/結束 ( flag )。

01111111...:錯誤(7 個或更多 1)(錯誤)。

當 FSM 被重置時,它應該處于一種狀態,就像之前的輸入為 0 一樣。

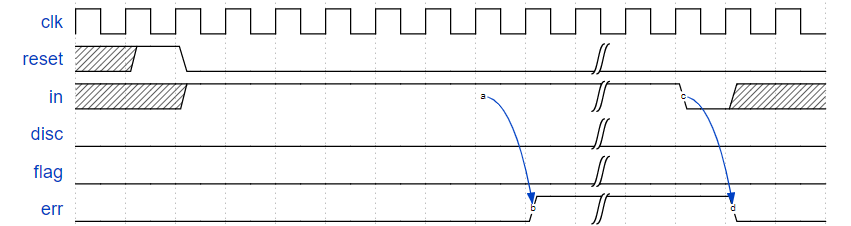

以下是說明所需操作的一些示例序列。

丟棄0111110:

圖片來自HDLBits

標志01111110:

圖片來自HDLBits

重置和錯誤01111111...:

圖片來自HDLBits

實現這個狀態機。

模塊端口聲明

moduletop_module( inputclk, inputreset,//Synchronousreset inputin, outputdisc, outputflag, outputerr);

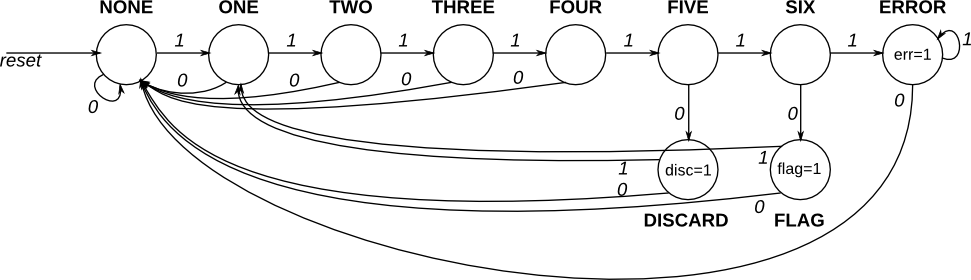

8題目解析

1、請使用10個狀態以內的摩爾機。

2、狀態圖:

moduletop_module(

inputlogicclk,

inputlogicreset,//Synchronousreset

inputlogicin,

outputlogicdisc,

outputlogicflag,

outputlogicerr

);

//definestate

typedefenumlogic[2:0]{detect_0=3'd0,receive_1=3'd1,

receive_2=3'd2,receive_3=3'd3,

receive_4=3'd4,receive_5=3'd5,

receive_6=3'd6,receive_7=3'd7

}state_def;

state_defcur_state,next_state;

//describestatetransitionlogicusecombinationallogic

always_combbegin

case(cur_state)

detect_0:begin

next_state=in?receive_1:detect_0;

end

receive_1:begin

next_state=in?receive_2:detect_0;

end

receive_2:begin

next_state=in?receive_3:detect_0;

end

receive_3:begin

next_state=in?receive_4:detect_0;

end

receive_4:begin

next_state=in?receive_5:detect_0;

end

receive_5:begin

next_state=in?receive_6:detect_0;

end

receive_6:begin

next_state=in?receive_7:detect_0;

end

receive_7:begin

next_state=in?receive_7:detect_0;

end

default:begin

next_state=detect_0;

end

endcase

end

//describestatesequecerusesequentiallogic

always_ff@(posedgeclk)begin

if(reset)begin

cur_state<=?detect_0?;

????????end

????????else?begin

????????????cur_state?<=?next_state?;

????????end

????end

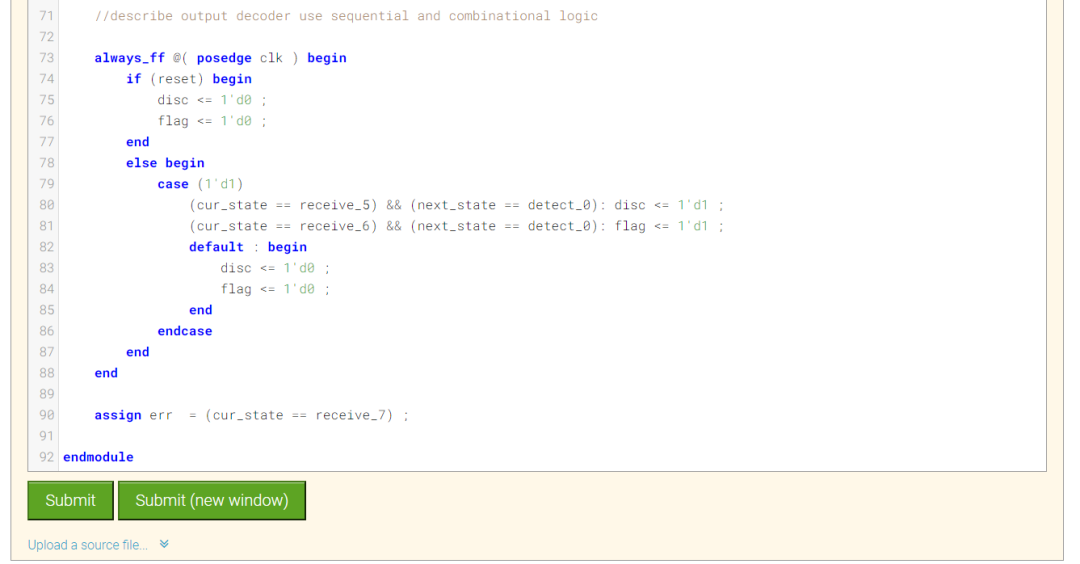

????//describe?output?decoder?use?sequential?and?combinational?logic

????always_ff?@(?posedge?clk?)?begin?

????????if?(reset)?begin

????????????disc?<=?1'd0?;

????????????flag?<=?1'd0?;

????????end

????????else?begin

????????????case?(1'd1)

????????????????(cur_state?==?receive_5)?&&?(next_state?==?detect_0):?disc?<=?1'd1?;

????????????????(cur_state?==?receive_6)?&&?(next_state?==?detect_0):?flag?<=?1'd1?;

????????????????default?:?begin

????????????????????disc?<=?1'd0?;

????????????????????flag?<=?1'd0?;

????????????????end

????????????endcase

????????end

????end

????assign?err??=?(cur_state?==?receive_7)?;

endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

Part6Problem 138-ece241_2013_q8

9題目說明

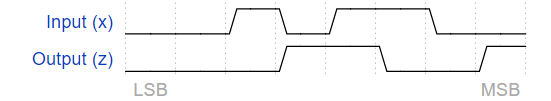

設計一個單輸入單輸出串行 2 的互補摩爾狀態機。輸入 (x) 是一系列位(每個時鐘周期一個),從數字的最低有效位開始,輸出 (Z) 是輸入的 2 的補碼。機器將接受任意長度的輸入數字。該電路需要異步復位。轉換在Reset釋放時開始,在Reset置位時停止。

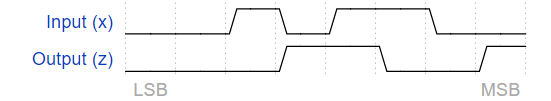

例如:

模塊端口聲明

moduletop_module( inputclk, inputareset, inputx, outputz );

10題目解析

米里型的輸出由當前狀態和輸入信號的組合邏輯實現,輸出信號與輸入信號同步。

而摩爾型狀態機的輸出僅由當前狀態決定,與輸入信號異步,往往存在延遲。

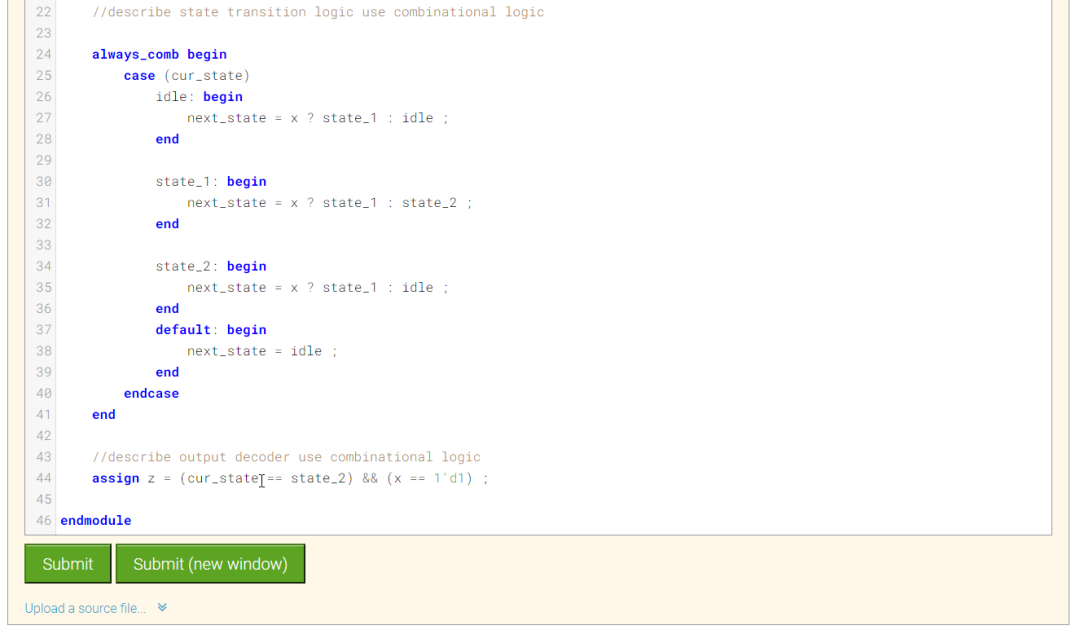

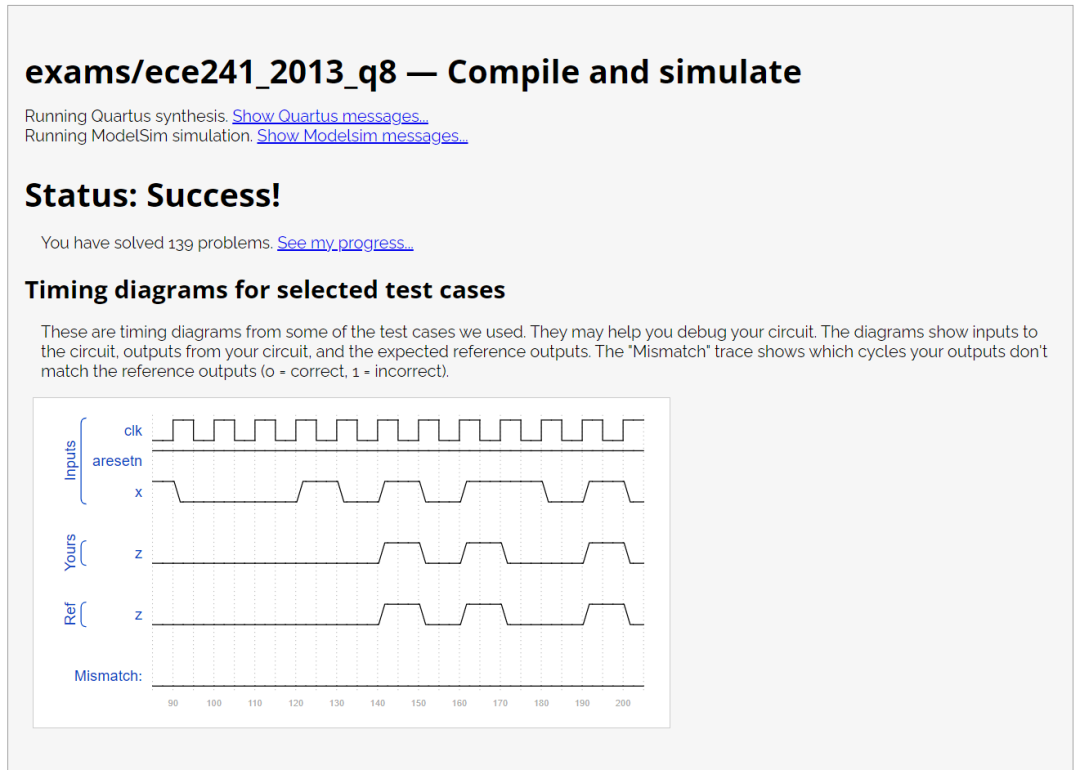

moduletop_module( inputlogicclk, inputlogicaresetn,//Asynchronousactive-lowreset inputlogicx, outputlogicz); //definestate typedefenumlogic[1:0]{idle=2'd0,state_1=2'd1,state_2=2'd2}state_def; state_defcur_state,next_state; //describestatesequecerusesequentiallogic always_ff@(posedgeclkornegedgearesetn)begin if(!aresetn)begin cur_state<=?idle?; ????????end ????????else?begin ????????????cur_state?<=?next_state?; ????????end ????end ????//describe?state?transition?logic?use?combinational?logic ????always_comb?begin? ????????case?(cur_state) ????????????idle:?begin ????????????????next_state?=?x???state_1?:?idle?; ????????????end? ????????????state_1:?begin ????????????????next_state?=?x???state_1?:?state_2?; ????????????end ????????????state_2:?begin ????????????????next_state?=?x???state_1?:?idle?; ????????????end ????????????default:?begin ????????????????next_state?=?idle?; ????????????end ????????endcase ????end ????//describe?output?decoder?use?combinational?logic ????assign?z?=?(cur_state?==?state_2)?&&?(x?==?1'd1)?; ???? endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

Part7Problem 139-ece241_2014_q5a

11題目說明

設計一個單輸入單輸出串行 2 的互補摩爾狀態機。輸入 (x) 是一系列位(每個時鐘周期一個),從數字的最低有效位開始,輸出 (Z) 是輸入的 2 的補碼。機器將接受任意長度的輸入數字。該電路需要異步復位。轉換在Reset釋放時開始,在Reset置位時停止。

例如:

圖片來自HDLBits

模塊端口聲明

moduletop_module( inputclk, inputareset, inputx, outputz );

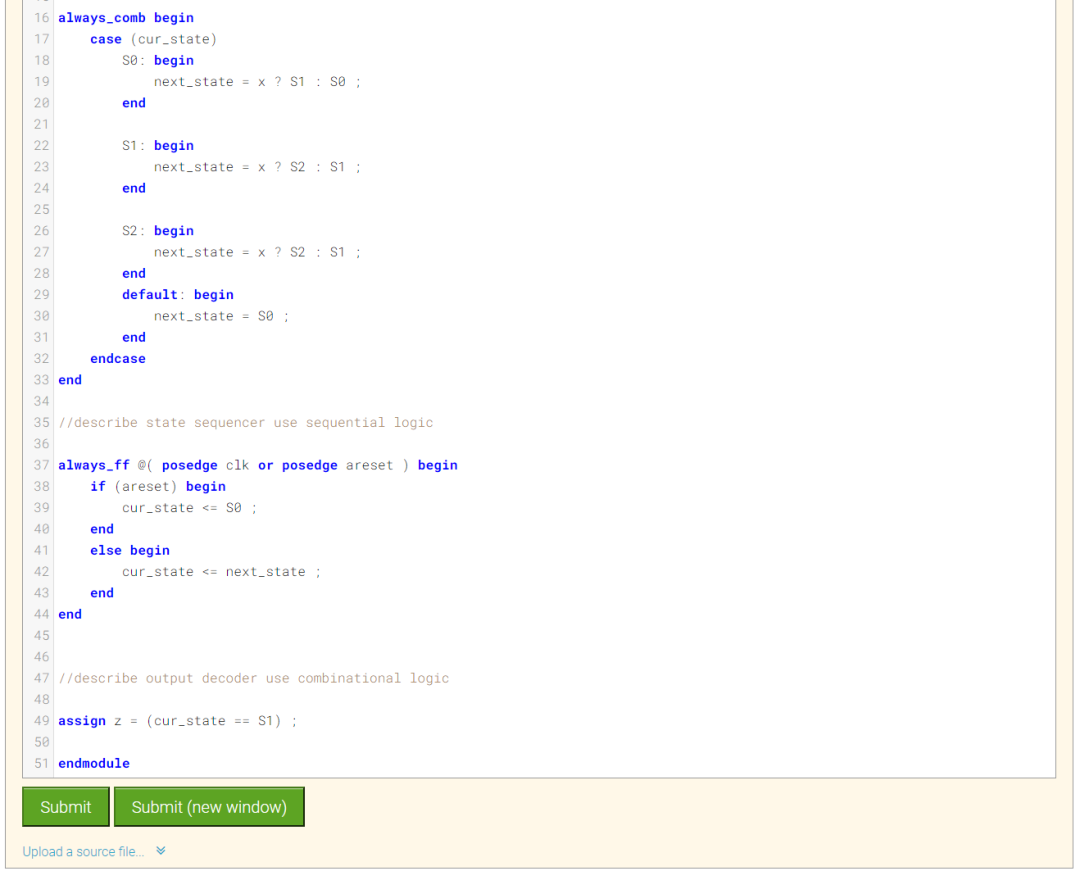

12題目解析

moduletop_module(

inputlogicclk,

inputlogicareset,

inputlogicx,

outputlogicz

);

//definestate

typedefenumlogic[1:0]{S0=2'd0,S1=2'd1,S2=2'd2}state_def;

state_defcur_state,next_state;

//describestatetransitionusecombinationallogic

always_combbegin

case(cur_state)

S0:begin

next_state=x?S1:S0;

end

S1:begin

next_state=x?S2:S1;

end

S2:begin

next_state=x?S2:S1;

end

default:begin

next_state=S0;

end

endcase

end

//describestatesequencerusesequentiallogic

always_ff@(posedgeclkorposedgeareset)begin

if(areset)begin

cur_state<=?S0?;

????end

????else?begin

????????cur_state?<=?next_state?;

????end

end

//describe?output?decoder?use?combinational?logic

assign?z?=?(cur_state?==?S1)?;

?

endmodule

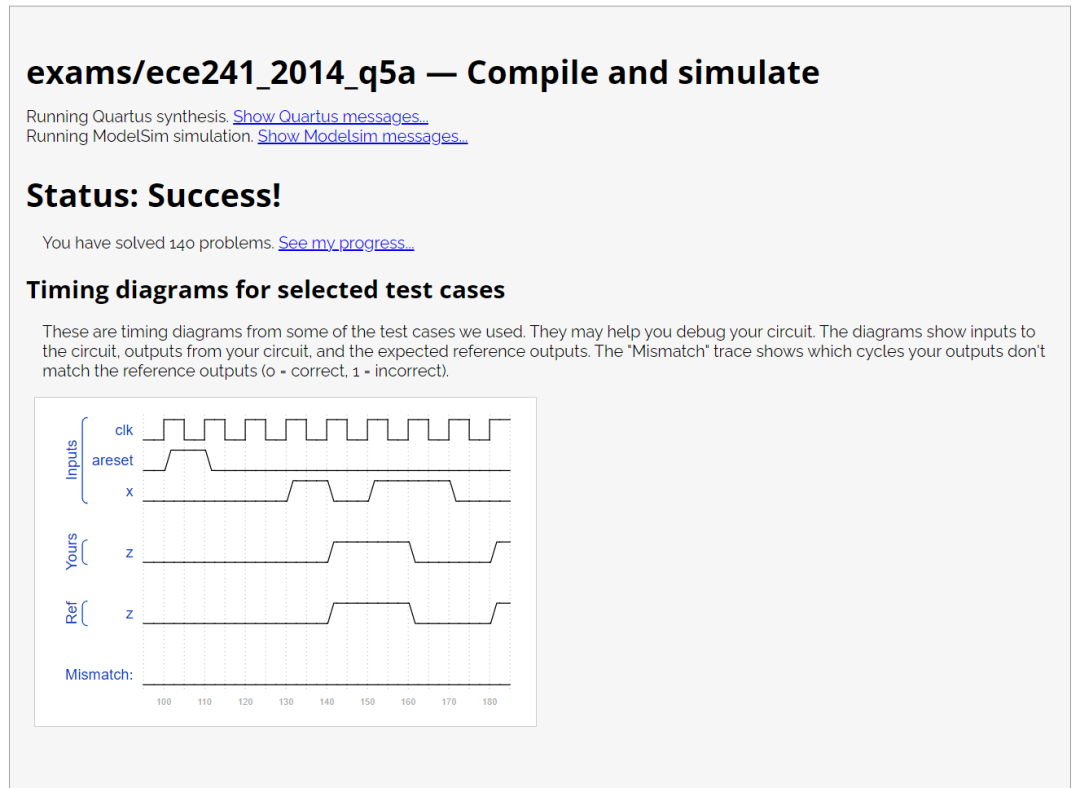

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

Part8Problem 140-23_ece241_2014_q5b

13題目說明

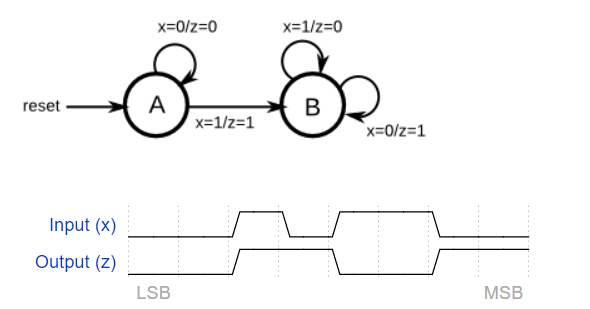

本題和上一題 Serial two's complementer (Moore FSM) 一樣,使用狀態機實現一個二進制補碼生成器,不同的是此題使用米里型狀態機實現。

圖片來自HDLBits

模塊端口聲明

moduletop_module( inputclk, inputareset, inputx, outputz );

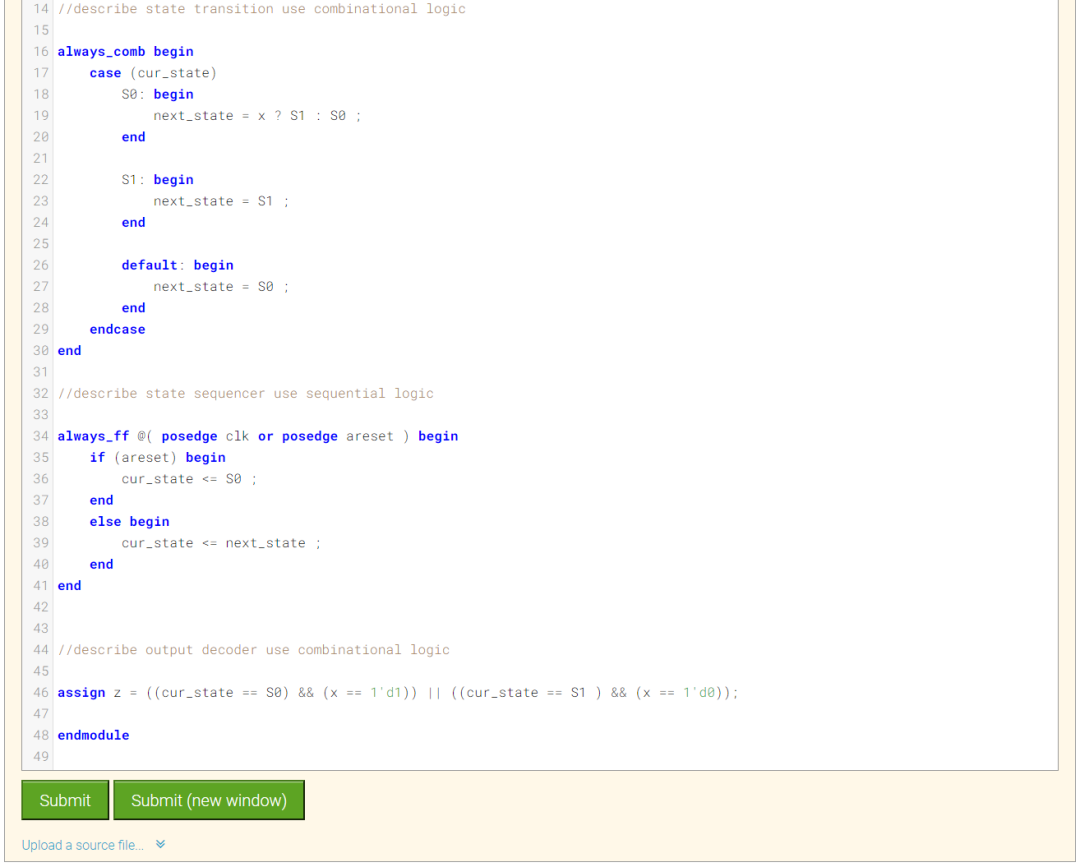

14題目解析

存在兩個狀態,復位狀態 A,在輸入 x 為 1 后狀態轉移為 B,并保持在狀態 B。

狀態 A 中輸出 z 與輸入 x 相同;狀態 B 中輸出 z 與輸入 x 相反。

moduletop_module(

inputlogicclk,

inputlogicareset,

inputlogicx,

outputlogicz

);

//definestate

typedefenumlogic{S0=1'd0,S1=1'd1}state_def;

state_defcur_state,next_state;

//describestatetransitionusecombinationallogic

always_combbegin

case(cur_state)

S0:begin

next_state=x?S1:S0;

end

S1:begin

next_state=S1;

end

default:begin

next_state=S0;

end

endcase

end

//describestatesequencerusesequentiallogic

always_ff@(posedgeclkorposedgeareset)begin

if(areset)begin

cur_state<=?S0?;

????end

????else?begin

????????cur_state?<=?next_state?;

????end

end

//describe?output?decoder?use?combinational?logic

assign?z?=?((cur_state?==?S0)?&&?(x?==?1'd1))?||?((cur_state?==?S1?)?&&?(x?==?1'd0));

?

endmodule

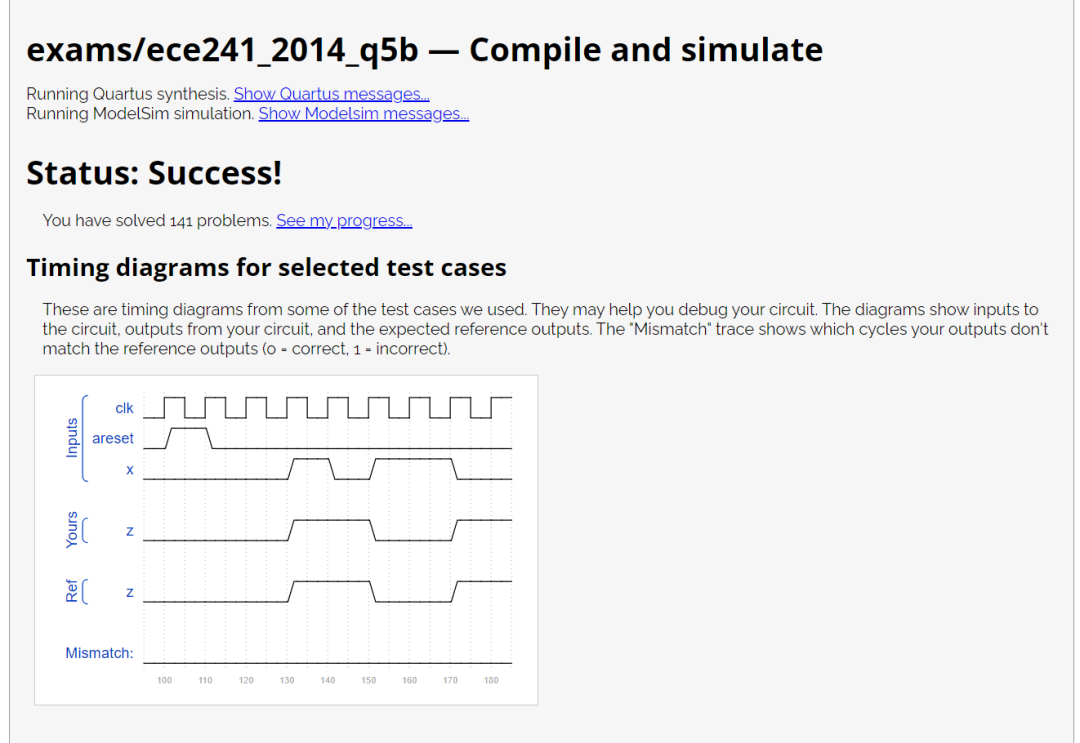

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

Part9Problem 141-2014_q3fsm

15題目說明

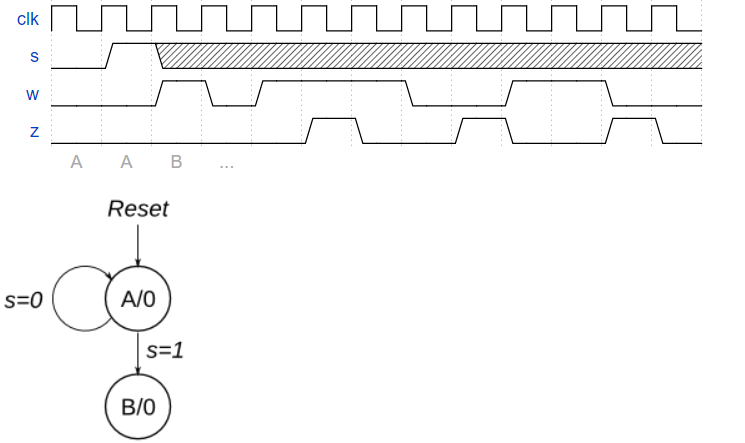

考慮具有輸入s和w的有限狀態機。假設 FSM 開始于稱為A的重置狀態,如下所示。只要s = 0, FSM 就保持在狀態A ,當s = 1 時,它會移動到狀態B。一旦進入狀態B,FSM在接下來的三個時鐘周期內檢查輸入w的值。如果在這些時鐘周期中恰好有兩個時鐘周期內w = 1,則 FSM 必須 在下一個時鐘周期內將輸出z設置為 1。否則z必須為 0。FSM 繼續檢查w對于接下來的三個時鐘周期,依此類推。下面的時序圖說明了不同w值所需的z值。

使用盡可能少的狀態。請注意,s輸入僅在狀態A中使用,因此只需考慮w輸入。

圖片來自HDLBits

模塊端口聲明

moduletop_module( inputclk, inputreset,//Synchronousreset inputs, inputw, outputz );

16題目解析

值得注意的是:需要三個周期中 exactly 兩個周期為 1 。

moduletop_module(

inputlogicclk,

inputlogicreset,//Synchronousreset

inputlogics,

inputlogicw,

outputlogicz

);

//definestate

typedefenumlogic{A=1'd0,B=1'd1}state_def;

state_defcur_state,next_state;

//describestatetransitionusecombinationallogic

always_combbegin

case(cur_state)

A:begin

next_state=s?B:A;

end

B:begin

next_state=B;

end

default:begin

next_state=A;

end

endcase

end

//describestatesequencerusesequentiallogic

always_ff@(posedgeclk)begin

if(reset)begin

cur_state<=?A?;

????end

????else?begin

????????cur_state?<=?next_state?;

????end

end

//define?counter?use?sequential?and?combinational?logic

var?logic?[1:0]?count?,?count_c;

wire?logic?resetn?;

assign?resetn?=?(count_c?==?2'd3)???1'd0?:?1'd1?;

always_ff?@(?posedge?clk?)?begin?

????if(reset)?begin

????????count?<=?2'd0?;

????end

????else?if?(!resetn)?begin

????????????if(w?==?1'd1)?begin

?????????????count?<=?2'd1?;

????????????end

????????????else?begin

????????????count?<=?2'd0?;

????????????end

????end

????else?begin

????????if?(cur_state?==?B?&&?w?==?1'd1)?begin

????????????count?<=?count?+?2'd1?;

????????end

????????else?begin

????????????count?<=?count?;

????????end

????????

????end

end

always_ff?@(?posedge?clk?)?begin?

????if?(reset)?begin

????????count_c?<=?2'd0?;

????end

????else?begin

????????if?(cur_state?==?B?&&?count_c?==?2'd3)?begin

????????count_c?<=?2'd1?;

????????end

????????else?if?(cur_state?==?B)?begin

????????????count_c?<=?count_c?+?2'd1?;

????????end

????????else?begin

????????count_c?<=?count_c?;

????????end

????end

????

end

//describe?output?decoder?use?combinational?logic

always_ff@(posedge?clk)?begin?

????if(reset)?begin

????????z?<=?1'd0?;

????end

????else?begin

??????case(?1'd1?)

??????(cur_state?==?B?&&?count_c?==?2'd2?&&?count?==?1?&&?w?==?1)?:?begin

????????z?<=?1'd1?;

??????end

??????(cur_state?==?B?&&?count_c?==?2'd2?&&?count?==?2?&&?w?==?0)?:?begin

????????z?<=?1'd1?;

??????end

??????default?:?begin

????????z?<=?1'd0?;

??????end

??????endcase

????end

end

endmodule

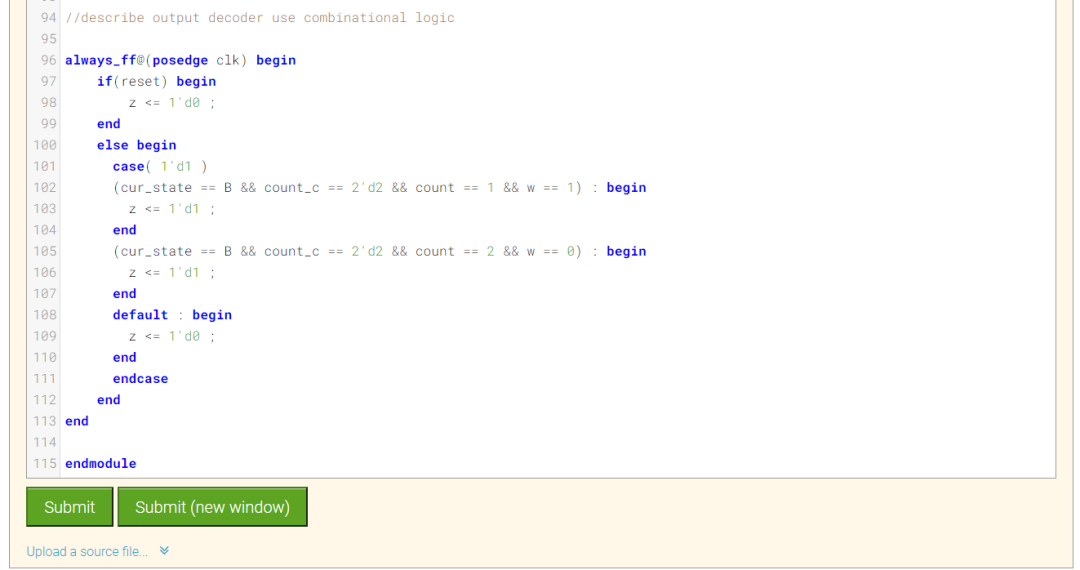

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

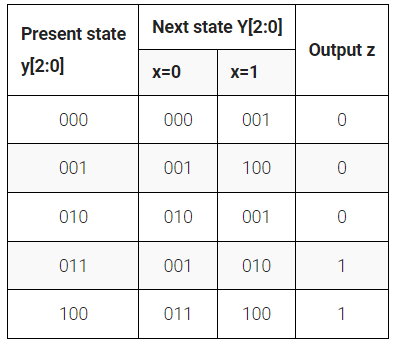

Part10Problem 142-2014_q3bfsm

17題目說明

這是一道簡單的根據狀態轉移實現狀態機的題目,實現完整的三段式狀態機

圖片來自HDLBits

模塊端口聲明

moduletop_module( inputclk, inputreset,//Synchronousreset inputx, outputz );

18題目解析

moduletop_module(

inputlogicclk,

inputlogicreset,//Synchronousreset

inputlogicx,

outputlogicz

);

//definestate

typedefenumlogic[2:0]{S0=3'b000,S1=3'b001,

S2=3'b010,S3=3'b011,

S4=3'b100

}state_def;

state_defcur_state,next_state;

//describestatetransitionusecombinationallogic

always_combbegin

case(cur_state)

S0:begin

next_state=x?S1:S0;

end

S1:begin

next_state=x?S4:S1;

end

S2:begin

next_state=x?S1:S2;

end

S3:begin

next_state=x?S2:S1;

end

S4:begin

next_state=x?S4:S3;

end

default:begin

next_state=S0;

end

endcase

end

//describestatesequencerusesequentiallogic

always_ff@(posedgeclk)begin

if(reset)begin

cur_state<=?S0?;

????end

????else?begin

????????cur_state?<=?next_state?;

????end

end

//describe?output?decoder?use?combinational?logic

assign?z?=?(cur_state?==?S3)?||?(cur_state?==?S4)?;

endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中無參考波形。

這一題就結束了。

Part11總結

今天的幾道題就結束了,對于狀態機的理解還是有益處的,三段式狀態機是題目一直推崇的,類似狀態機的公示,可以“套”進去。

審核編輯:劉清

-

通信協議

+關注

關注

28文章

892瀏覽量

40330 -

接收器

+關注

關注

14文章

2473瀏覽量

71980 -

數字電路

+關注

關注

193文章

1608瀏覽量

80677 -

狀態機

+關注

關注

2文章

492瀏覽量

27561

原文標題:HDLBits: 在線學習 SystemVerilog(二十)-Problem 134-142(狀態機三)

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA工程師:如何在FPGA中實現狀態機?

FPGA---如何寫好狀態機,詳細下載pdf

MCU裸機編程狀態機的定義與注意事項是什么

基于FPGA的狀態機設計

合理高效地使用狀態機是數字電路中的重要技能

合理高效地使用狀態機是數字電路中的重要技能

評論