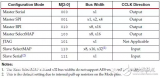

PCIE簡介

PCI Express 是用來互聯計算機和外圍設備的高速接口總線,是一種能夠應用于移動設備,臺式電腦,工作站,服務器,嵌入式計算機和通信平臺等。

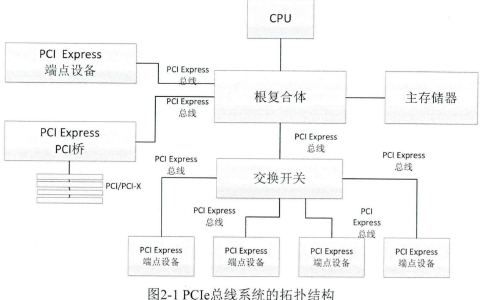

PCIe的兩個設備之間可以實現點對點的通信串行通信,如果是多臺設備需要通過交換器(Switch)進行互聯,這樣一個系統可以連接多個設備。

PCIe總線作為處理器系統的局部總線,其作用與PCI總線類似,主要目的是為了連接處理器系統中的外部設備,當然PCIe總線也可以連接其他處理器系統。

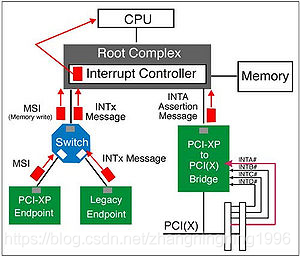

在不同的處理器系統中, PCIe體系結構的實現方法略有不同。但是在大多數處理器系統中,都使用了RC、 Switch和PCIe-to-PCI橋這些基本模塊連接PCIe和PCI設備。在PCIe總線中,基于PCIe總線的設備,也被稱為EP(Endpoint)。

計算機通信平臺中 , PCI Express體系結構代表作高性能的外圍組件互聯方法

1、 由PCI 和PCI-X 體系結構演變而來architectures

2、 PCI Express 以一種串行的點對點的方式互聯兩個設備

3、 信息傳輸基于數據包協議實現

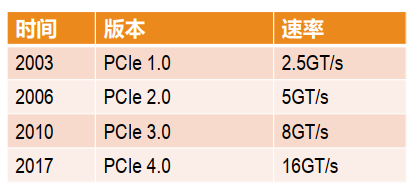

4、 PCI Express 互聯中可實現單通道或多通道的數據傳輸 5、 PCI Express 協議目前已經發布4個版本  ?

?

PCIE的特性如下:

1、點對點傳輸

2、 串行總線意味著使用更少的引腳

3、 通道數可選擇: x1, x2, x4, x8, x12, x16, x32

4、 全雙工通信

5、 2.5Gbps / 5.0Gbps

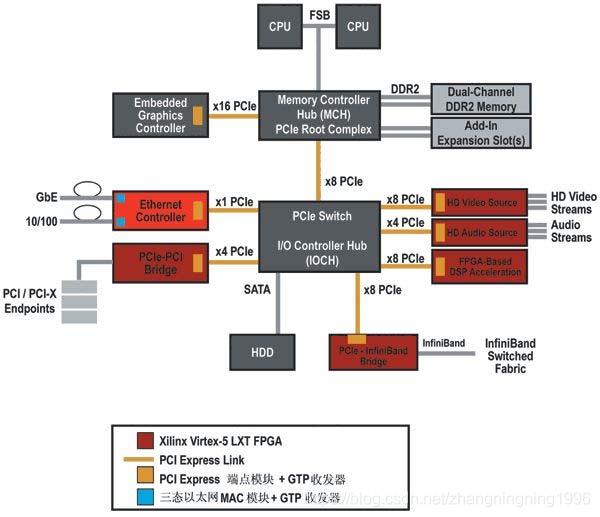

6、 基于數據包的傳輸協議 計算機體系結構中PCIe的應用架構如下:

?

?

從上面我們可以看出PCIE應用架構主要包括四部分:

1、FSB總線CPU交互總線:FSB總線(Front Side Bus)是CPU和DDR內存交互的總線

2、Root Complex:RC (Root complex)是PCIe結構體系中的一個重要的結構部件, RC的提出跟X86系統架構密切相關,實際上只有在x86架構中才有標準的RC規范定義,而在其他系統中并不存在標準定義的RC的全部功能。例如X86的架構中包含DDR控制器和FSB to PCIe的橋, 而ZynqSoc芯片架構中包含AXI to PCIe的橋和DDR控制器,PowerPc只包含一個PCIe總線控制器。這里需要注意Root complex包括root port。

3、PCIe Switch:Switch PCIe鏈路通過Switch進行鏈路擴展

4、PCIe End point:即常見的PCIE終端設備,FPGA最常用的也是End point。

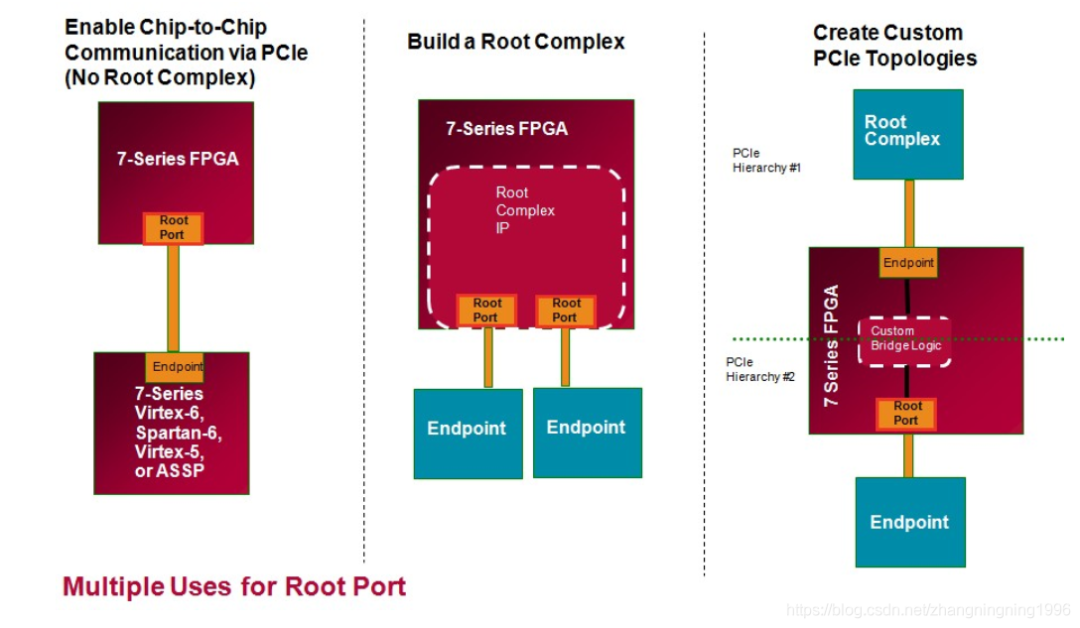

FPGA在PCIE中可以成為Root Complex、Switch和 End point:  ?

?

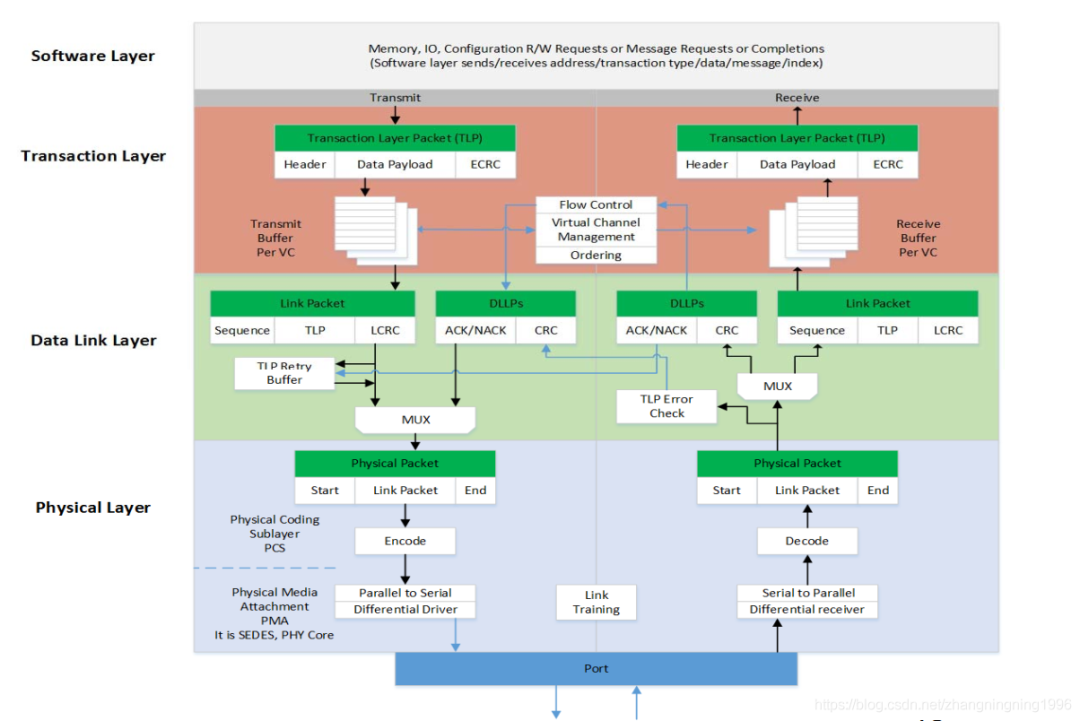

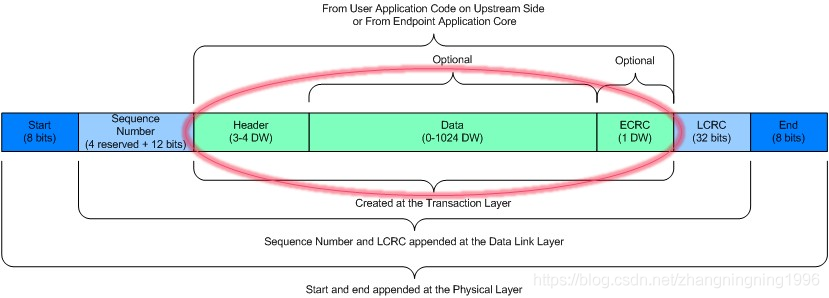

PCIe總線層次結構主要包括三層主要是事務層、數據鏈路層、物理層。

1、事務層:PCIe總線層次結構的最高層,該層次將接收PCIe設備核心層的數據請求,并將其轉換為PCIe總線事務, PCIe總線使用的這些總線事務在TLP頭中定義。PCIe總線使用的數據報文首先在事務層中形成, 這個數據報文也被稱之為事務層數據報 文,即TLP。(解釋:主要意思也就是事務層將數據封裝成TLP包發給下層使用)

2、數據連路層:TLP在經過數據鏈路層時被加上Sequence Number前綴和CRC后綴,然后發向物理層。

3、物理層:PCIe的電氣特性、電路等。在PCIe鏈路可以正常工作之前,需要對PCIe鏈路進行鏈路訓練,在這個過程中,就會用。

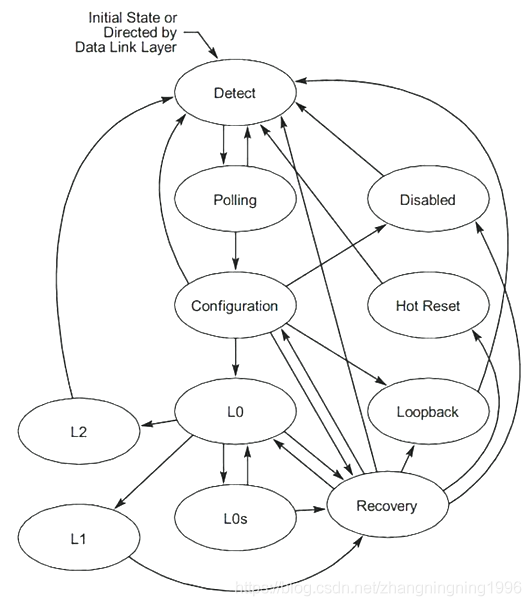

LTSSM狀態機。LTSSM全稱是Link Training and Status State Machine。這個狀態機在PCIe總線的物理層之中。狀態轉移圖如下:  ?

?

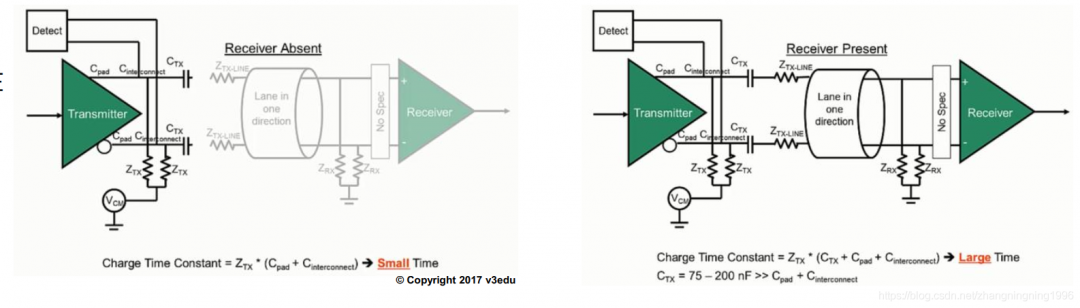

Detect狀態是PCIe鏈路訓練的開端。此外, Detect,顧名思義,需要實現檢測工作。因為在這個狀態時,發送端TX需要檢測接收端RX是否存在且可以正常工作,如果檢測正常,才能進入其他狀態。判斷RX是否存在的邏輯比較簡單,就是通過一個“Detect logic”電路比較RC時間常數的大小。  ?

?

從上圖可以發現PCIe終端連接上,時間常數會變大。多以也就以此決定Detect狀態是否進入下一個狀態。

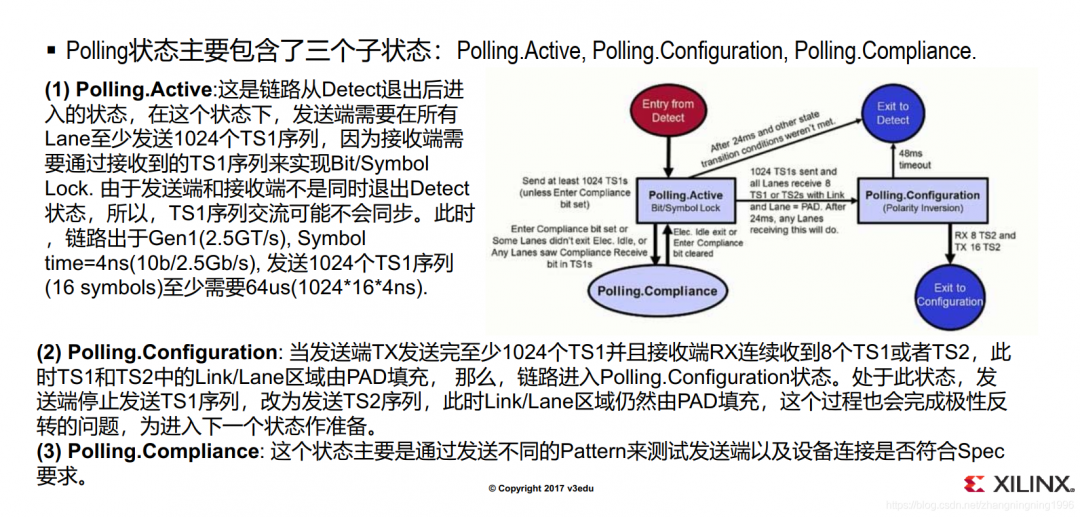

Polling 狀態的目的是"對暗號",實現無障礙溝通。進入這個狀態后, TX和RX之間通過發送TS1、 TS2 OS序列來確定Bit Lock, Symbol Lock以及解決Lane極性反轉的問題。

Bit Lock: 在Bit傳輸過程中, RX PLL鎖定TX Clock頻率,這個過程稱為RX實現"Bit Lock。(解釋:也就是位同步)

Symbol Lock: RX端串并轉化器知道如何區別一個有效的10-bit Symbol,這個過程稱為“Symbol Lock”. 這里用到的是COM控制符。(解釋:也就是幀同步)  ?

?

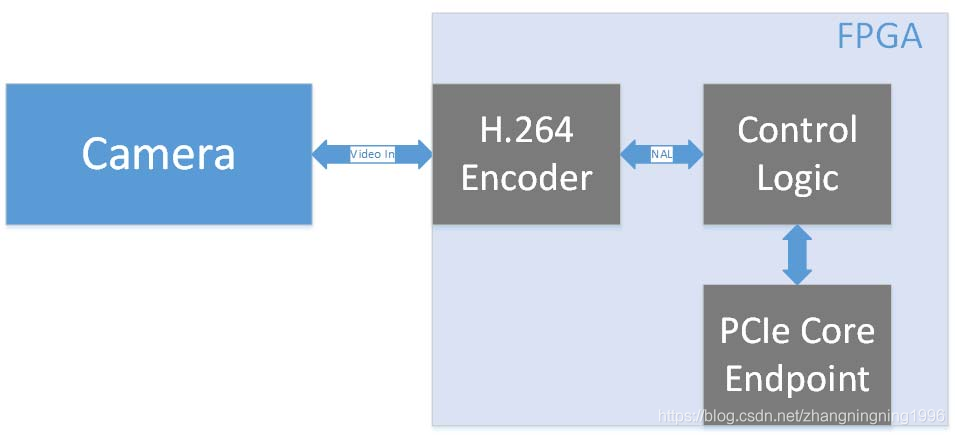

常見的視頻方案如下:

?

?

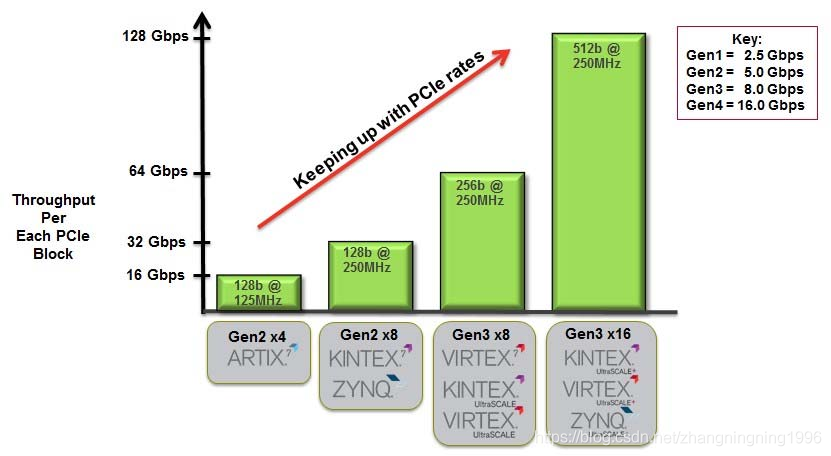

FPGA中PCIE的實現:

1、7系列FPGA支持實現Gen1與Gen2的PCIE協議

2、Virtex-7 FPGA支持實現Gen3的PCIE協議

3、UltraScale與UltraScale+支持Gen3的PCIE協議

4、支持x1,x2,x4,x8,x16lanes的通路

5、PCIE的硬核使用了GTP接口用來串行傳輸數據

PCIE的速度傳輸速度如下:

?

?

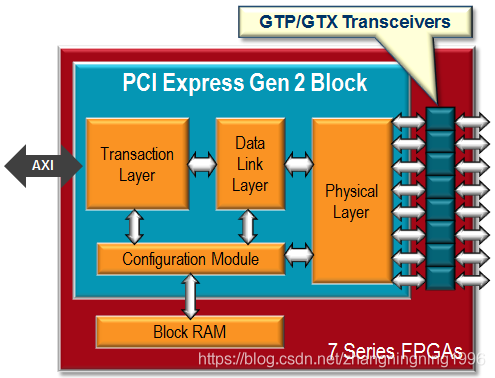

FPGA中PCIE硬核的介紹,整體框圖如下:  ?

?

1、該硬核PCIE支持Endpoint和Root Port

2、支持AXI4-Stream用戶接口: x1, x2, x4, 和x8 lanes; 64-bit 和128-bit位寬

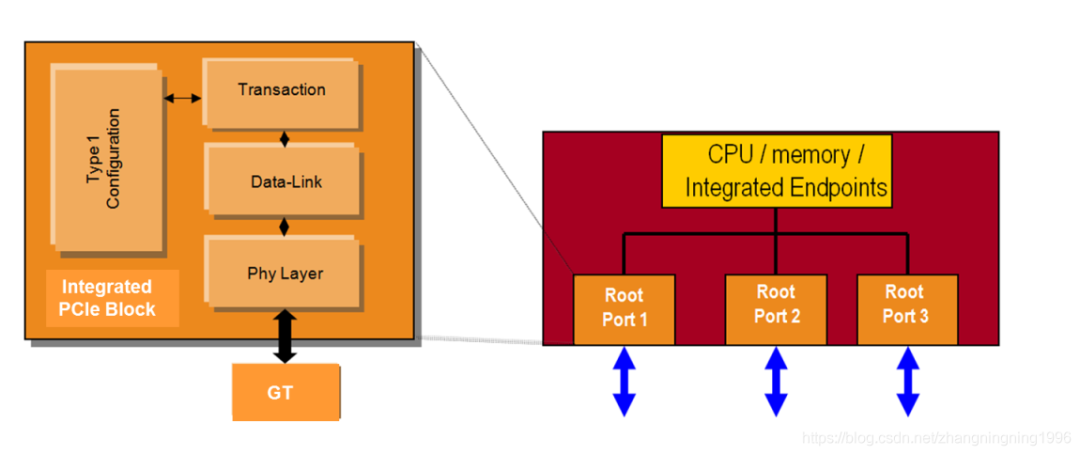

Root Port簡要介紹

Xilinx FPGAs支持硬核root port,但是沒有硬核root complex。root complex包括一個或多個root port、內存,IO子系統等等。root port只是提供給switch或者endpoint連接的端口。二者之間的關系如下:

?

?

root port經常使用在簡單的設計中,比如與單個的endpoint相連。root complex則有配套的軟件環境與復雜的設計。

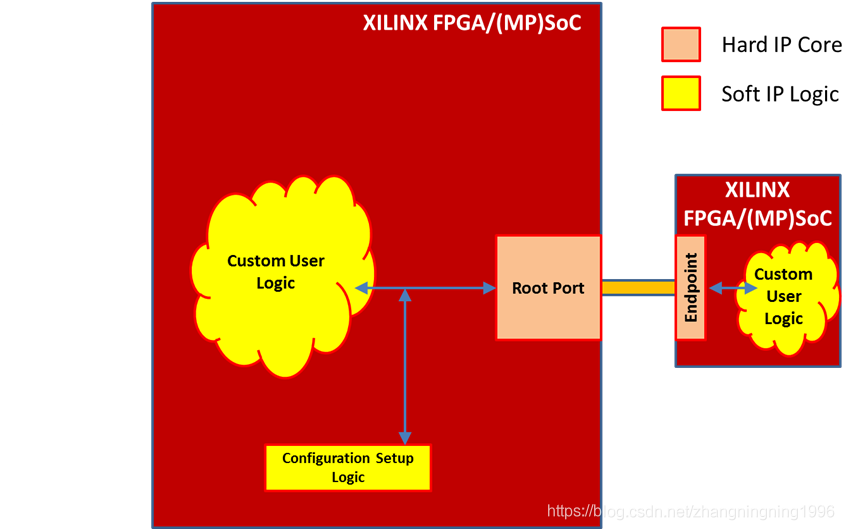

FPGA構建root port的常見案例如下:  ?

?

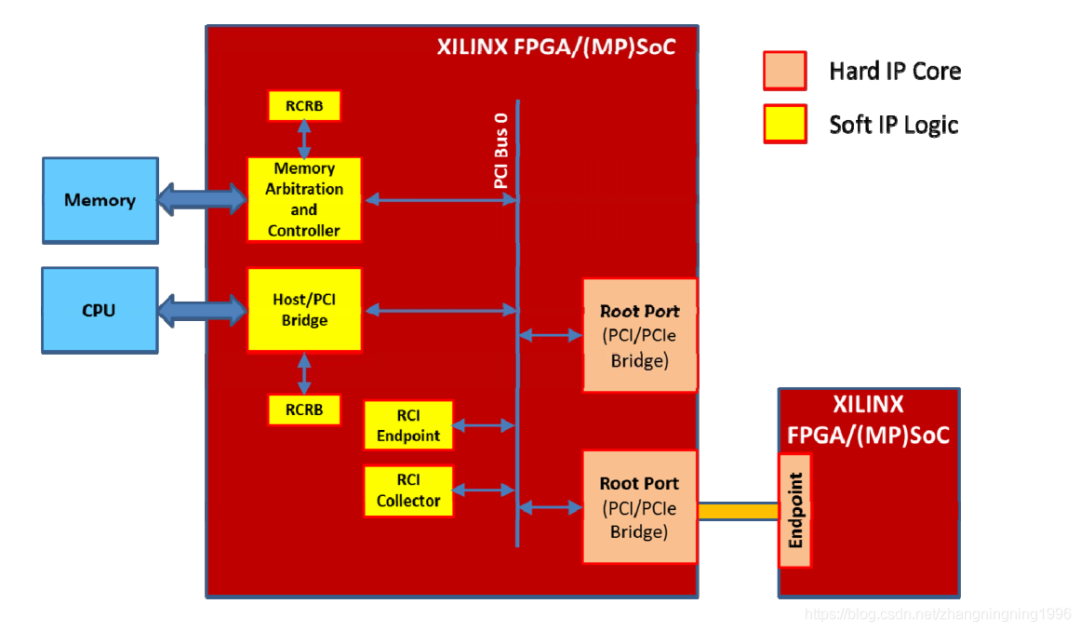

FPGA構建root complex的常見案例如下:  ?

?

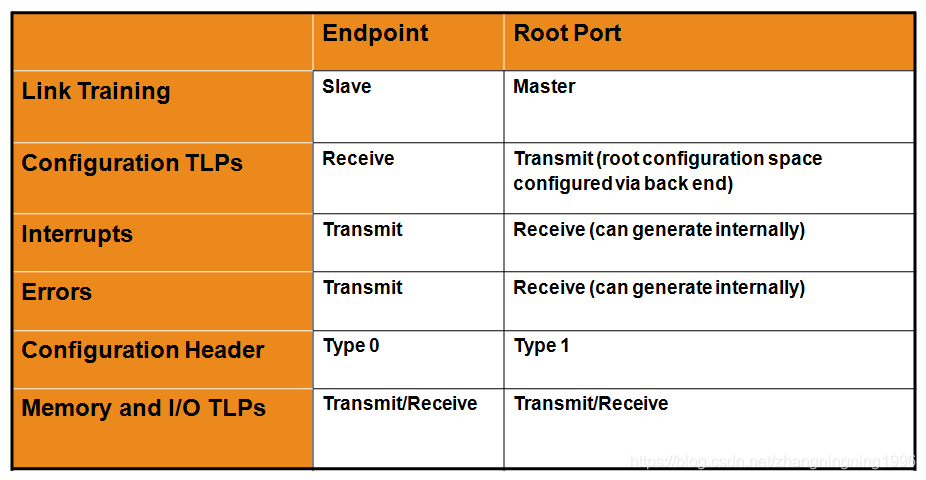

root port與endpoint也有許多不同點。root port使用Type 1配置頭空間。endpoint使用Type 0配置頭空間。兩者主要的區別如下:  ?

?

PCIE協議簡述

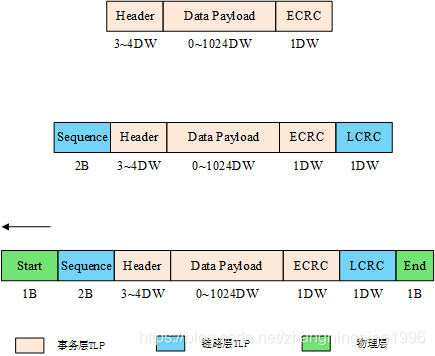

PCIE的地址空間

PCI Express實現了四種地址空間:

1、PCIe配置空間(多達4KB) – 必須有,每個PCI設備都有其映射到內存上的配置空間 – 前256字節與PCI兼容

2、PCIe內存映射空間 – 可選的,根據設備功能選擇是否需要映射內存空間

3、PCIe IO映射空間 – 可選的

4、PCIe消息空間

其中PCIe消息空間主要用于中斷的使用,內存映射空間用于大量數據的傳輸,IO映射空間用于少量數據的傳輸。  ?

?

Type0型: – 用于配置端點設備 – 由根復合體發起,配置預定義的PCI系統端點設備頭部區域 – 設備號/ID號 – BAR

Type1型: – 用于配置Switches/Bridges/end point

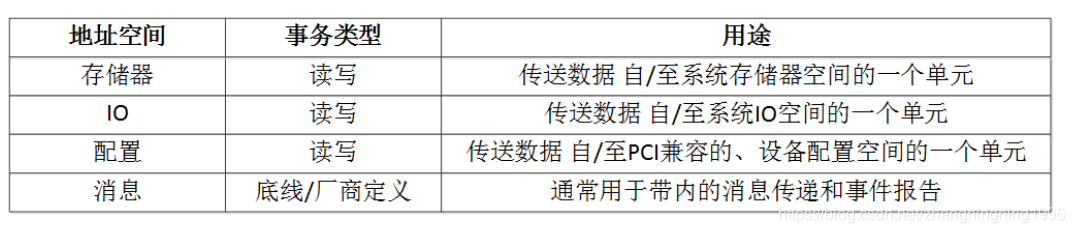

PCIE TLP包的數據類型

上面已經講解PCIE分別包括事務層、數據鏈路層、物理層,每一層對TLP包的作用如下:

?

?

這里的3DW與4DW其實是與地址是32位還是64位掛鉤。

具體TLP包在每層協議的情況如下:  ?

?

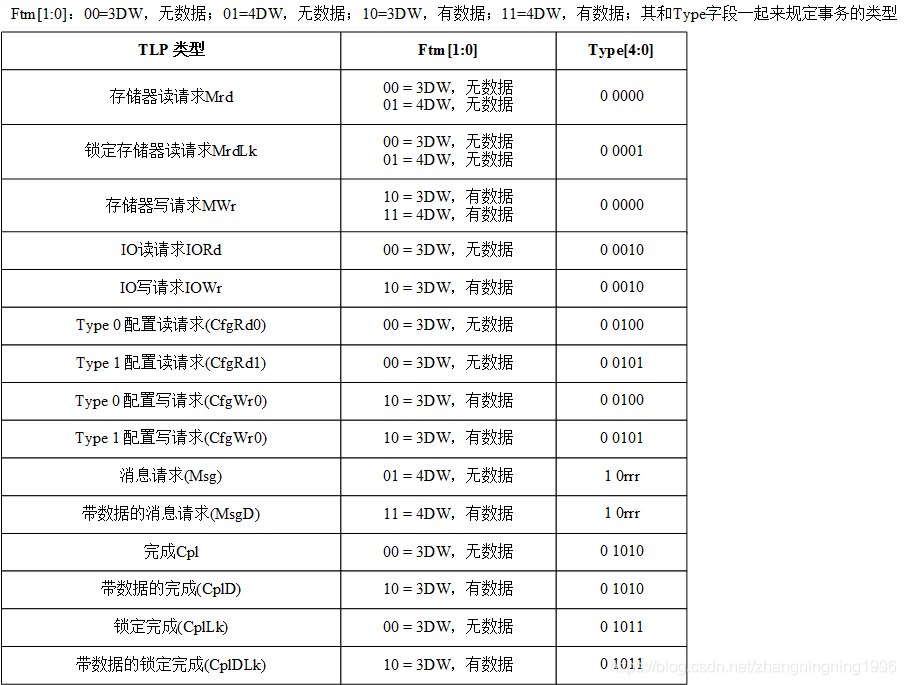

PCIE中TLP包的類型如下:

?

?

PCIE的路由類型

PCIE每一種請求或者完成報文頭都會有類型標注,每個數據包的路由都基于以下三種方式:

1、 地址路由

2、 ID 路由

3、 隱含式路由

端點的地址路由

端點設備檢查TLP包中的地址與BAR中所有地址進行比較,如果不屬于本端點范圍,則拒絕。

端點的ID路由

端點設備檢查TLP包里的 總線 ID 和 設備 ID 功能ID是否與本端點一致,這些信息在Type0的配置信息里可以捕獲。

不同類型的TLP包與路由類型的對應關系如下:

?

?

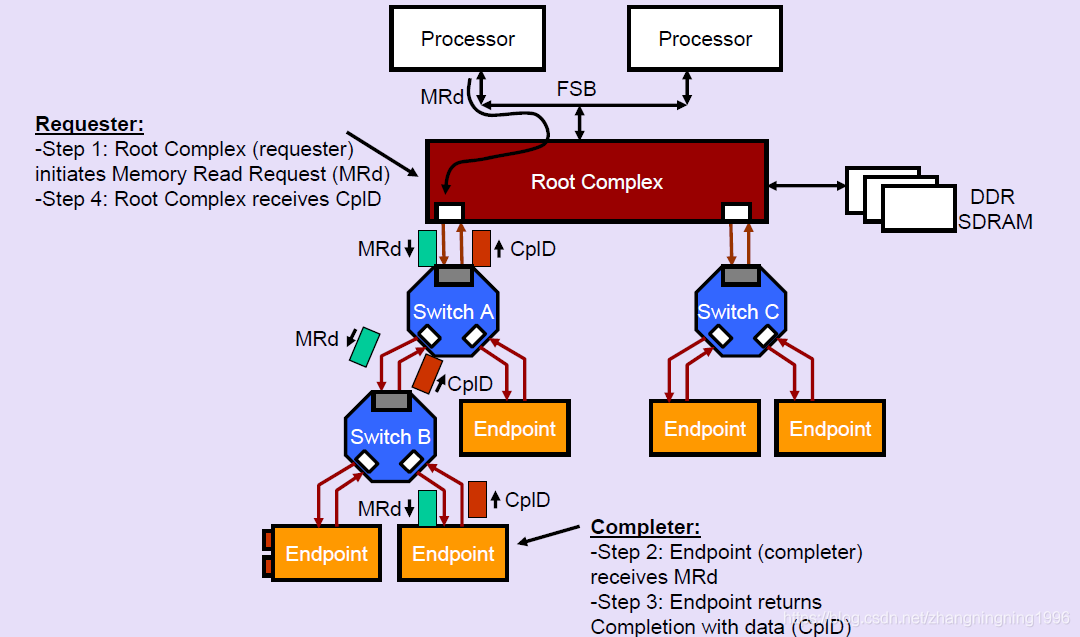

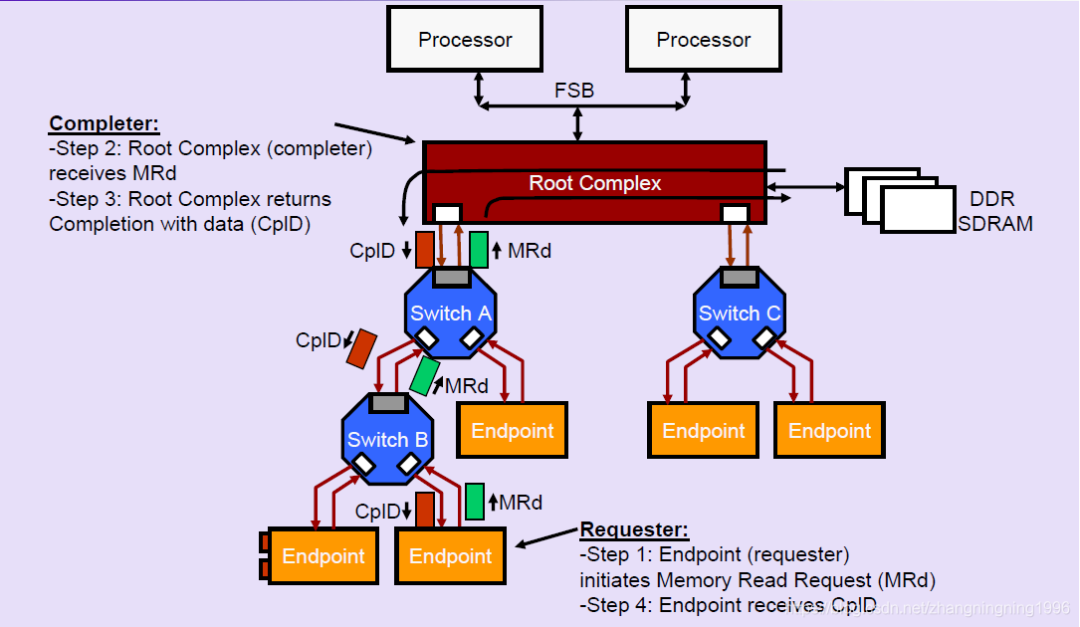

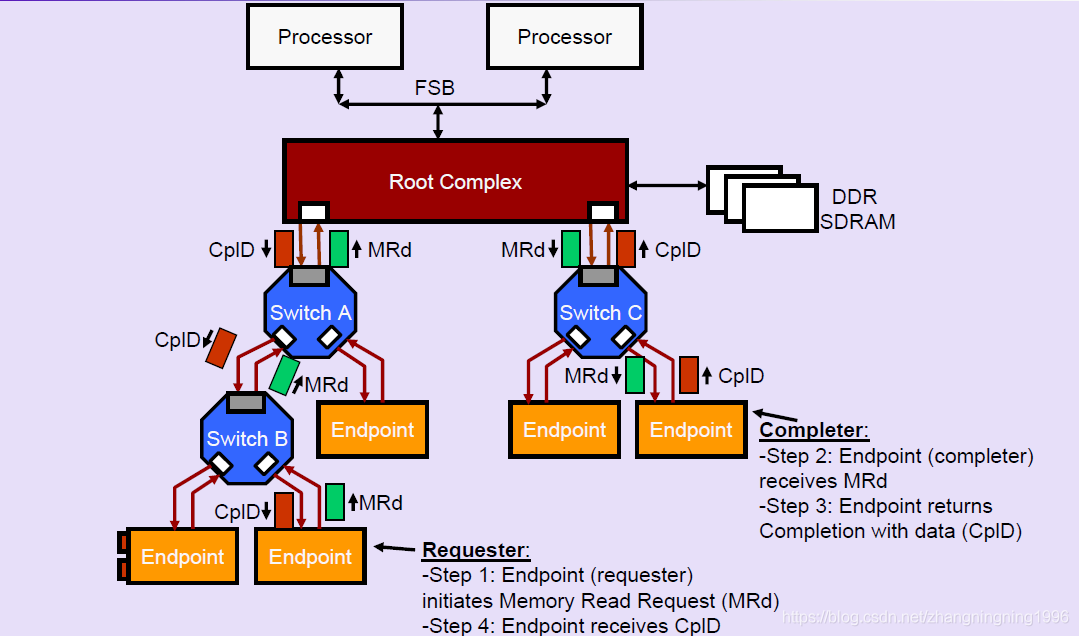

PCIE點對點的傳輸框圖

1、配置IO傳輸

?

?

2、DMA傳輸

?

?

3、end point與end piont之間的傳輸  ?

?

PCIE的中斷類型

PCIE的中斷類型主要有兩種:

1、MSI:消息中斷

2、INTx:引腳中斷 真正的PCIe設備:必須使用MSI發送中斷,可選擇性地支持INTx消息。

PCI設備:必須支持INTx消息

?

?

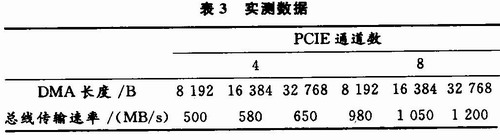

PCIE的理論帶寬

Gen2單向鏈路速率5Gbps

1、 使用8B/10B編碼,產生20%的數據開銷

2、 理論帶寬=鏈路速率 80% 通道數

3、 對于單通道: – Gen1: 2.5Gbps0.8=250MBps – Gen2: 5Gbps0.8=500MBps – Gen3: 8Gbps*1=1GBps

4、 更多的開銷是由協議導致 – 數據頭 – 校驗位 – 鏈路訓練 – 錯誤通信

TLP包格式簡述

上面我們已經講解了TLP包常見的類型,那么這部分內容講解每種TLP包的具體格式。

一個TLP包的格式如下:

?

?

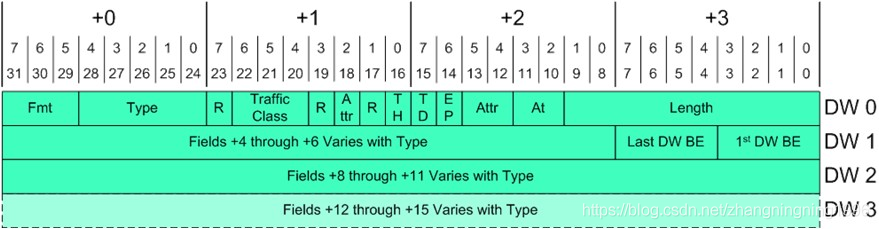

每位的詳細信息如下:

?

?

接下來對上面的每一位進行粗略的介紹。

1、Fmt:用來指明TLP包是3DW還是4DW

2、Type:用來確定TLP包的類型, Memory read or write Completion packet Configuration packet Message

3、Traffic Class:除了MemoryRead/Write TLPs必須是零,一般情況是默認為0

4、Attr:包含有關處理事務時核心行為的特定信息

5、TD:當該位位1是,TLP包中包括CRC檢驗,為零時不包括CRC校驗

6、EP:指示此TLP包含錯誤且應忽略

7、AT:地址類型,一般默認為零即可。 Default/Untranslated (00) Translation Request (10) Translated (11)

8、Length Field:描述TLP包種有效數據的長度,注意單位時DW,最大長度時1024個DW長度

9、First/Last Byte Enables:四位中的每一位分別對應TLP包中的第一個DW和最后一個DW中的每個字節是否有效。一個DW正好也是4個字節。

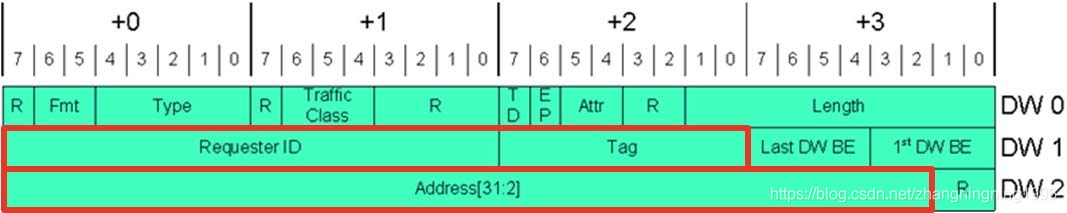

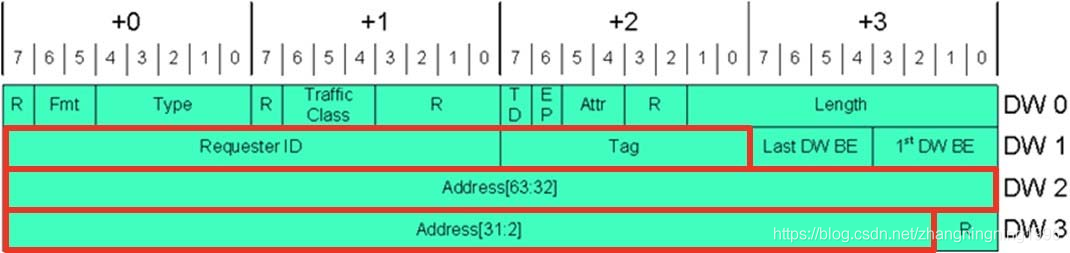

Memory Write TLP Header格式

Memory Write TLP Header格式如下:

3DW的TLP包頭:

?

?

4DW的TLP包頭:

?

?

1、Requester ID:包括bus, device, and function numbers這些在ID路由的時候時必備信息

2、Tag:由用戶定義,具體的內容與作用,用戶進行商議。

3、Address:byte address,最低的兩位總是零對齊到DWord尋址。

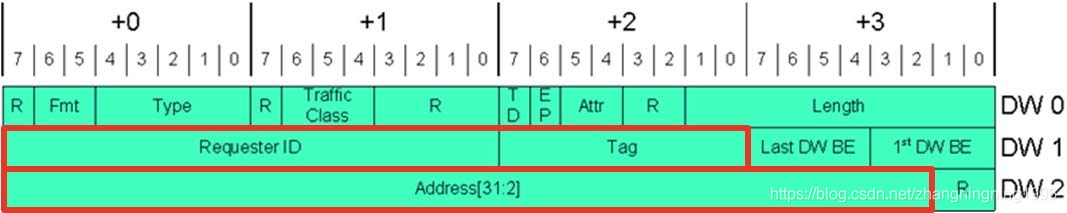

Memory Read TLP Header格式

Memory Read TLP Header格式如下:

3DW的TLP包頭:

?

?

4DW的TLP包頭:

?

?

1、Tag – 這里得Tag主要用于返回得CplDs包得重組,因為飯回來得完成包不一定是按照順序返回的。

這里沒有什么新的位介紹,在前面我們已經介紹完畢。

Memory Read 是 Non‐Posted: Non‐Posted的請求總是生成一個完成包來回應。除非出現錯誤,否則Posted的請求永遠不會生成完成包。一般的MRd會產生一個帶有數據包的完成。一個讀請求可以生成一個或多個完成包。

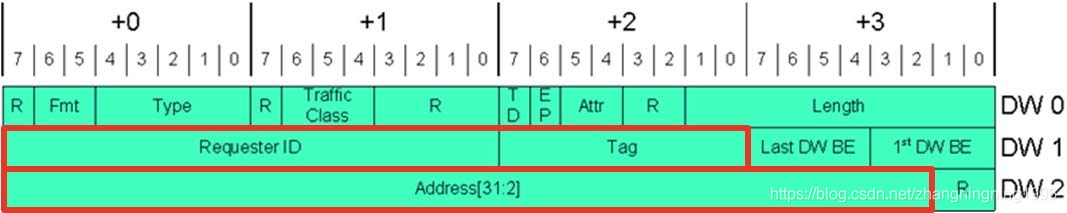

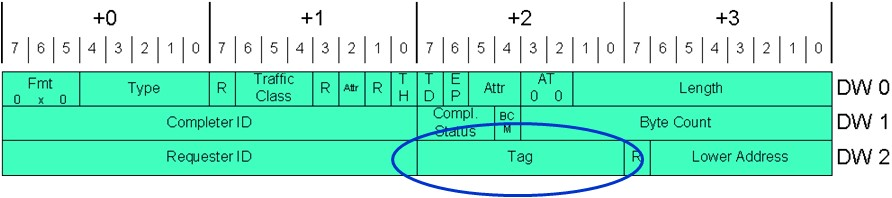

Completions TLPs格式

?

?

1、Tag:這里需要注意Tag標志主要是為了接收端按照發送的順序組包

2、Lower Address:指示第一個啟用的數據字節的字節地址的低位,較低的地址和長度不能跨越一個RCB RCB: Read Completion Boundary

3、Byte count:表示在滿足請求之前剩余的字節數

4、Completion status:只是完成包的狀態: Successful completion (“000”) Unsupported request (“001”) Configuration request retry status (“010”) Completer abort (“100”)

5、Requester ID:請求CplD的設備的ID(bus, device, function)

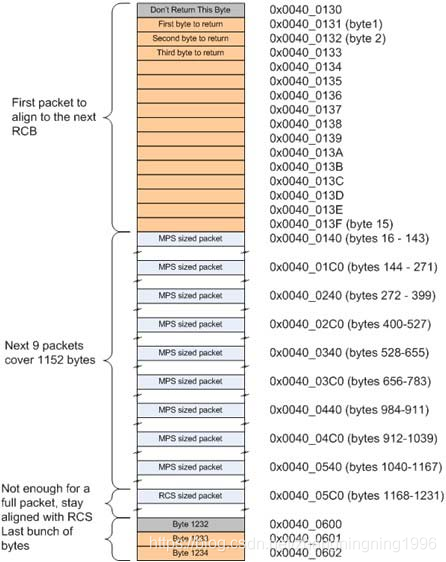

6、Completer ID:正在構建CplD的設備的ID(bus, device, function) 返回的時候必須是RCB的整數倍。而且第一個要與RCB對齊,且不能超過MPS,這里給出一個官方的示例:

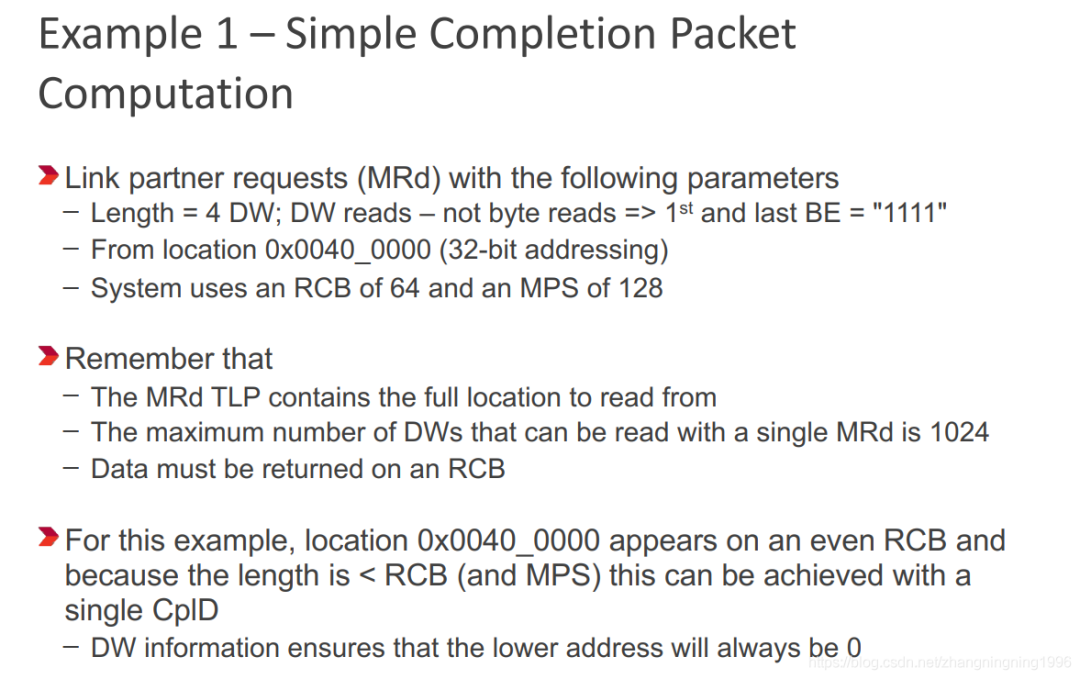

示例1:

?

?

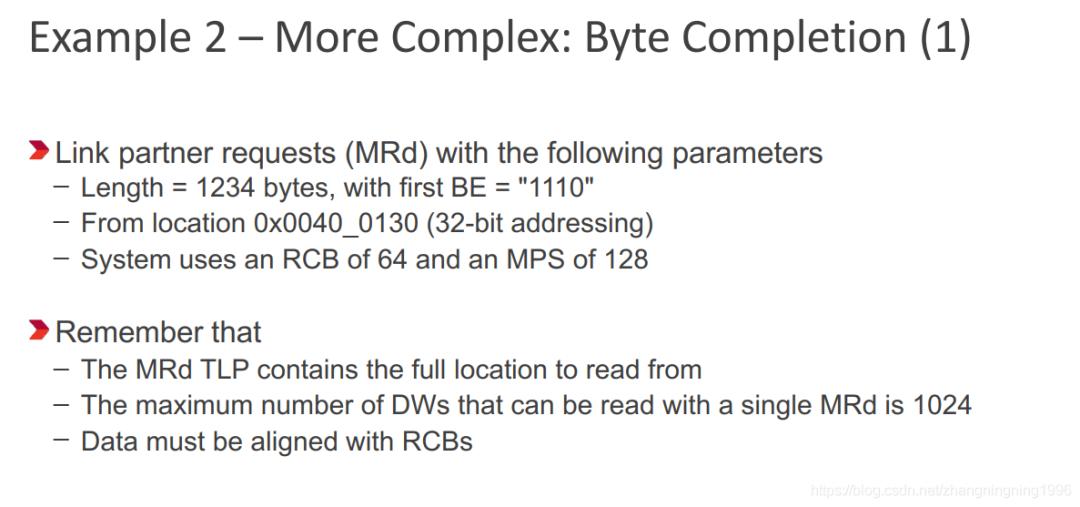

示例2:

題目:

?

?

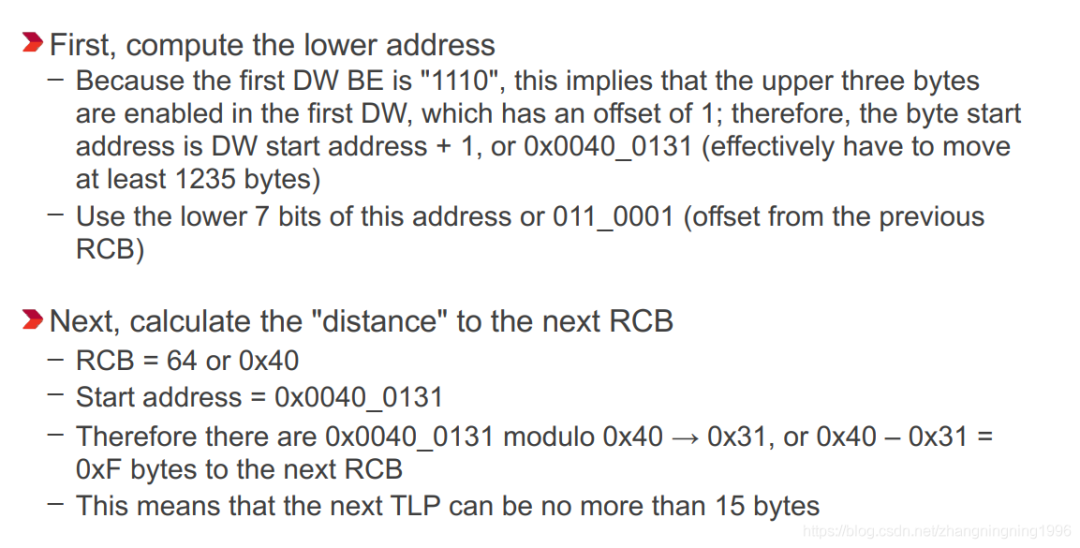

解答:

?

?

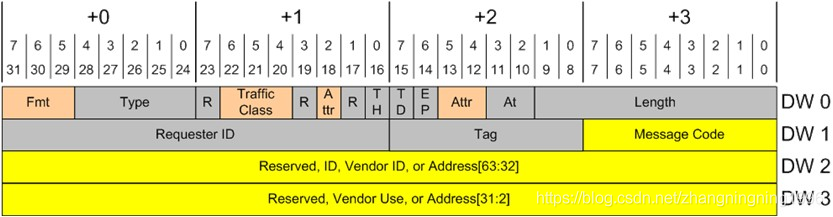

Message/Message with Data TLP格式

?

?

因為一般用不到我們進行手動組信息包,所以這里我們也就不詳細介紹。

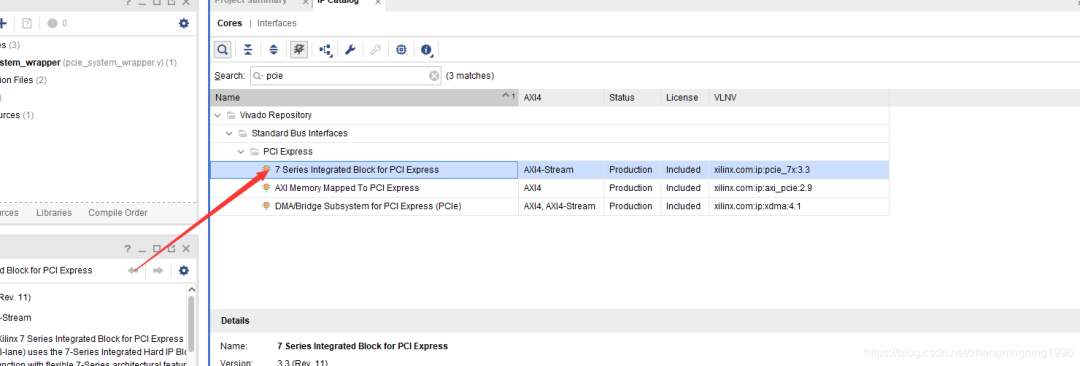

PCIE IP核配置需要的注意點

這里簡單介紹一下PCIE核配置過程中的注意點,這次我們先不使用XDMA IP,使用下面的PCIE IP:  ?

?

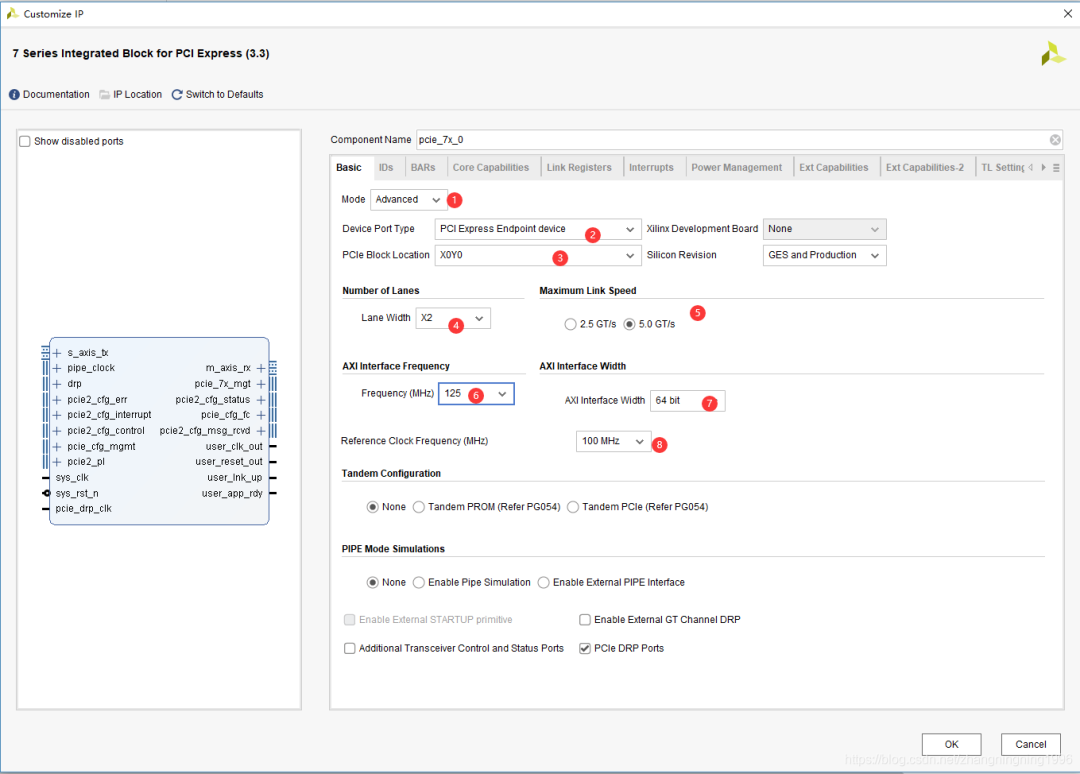

為了盡可能多的了解PCIE IP中的細節,我們選擇高級IP定制:  ?

?

1、選擇高級IP定制,供用戶選擇的功能增多

2、這里可以選擇這個PCIE IP核是當作endpoint還是root port來使用

3、這是指明這個PCIE IP再硬件中的位置編號

4、指明PCIE的lanes數目

5、指明一條lanes的最大通信速度

6、將PCIE轉換成AXI4協議的時鐘

7、將PCIE轉換成AXI4協議的數據位寬

8、PCIE IP的參考頻率  ?

?

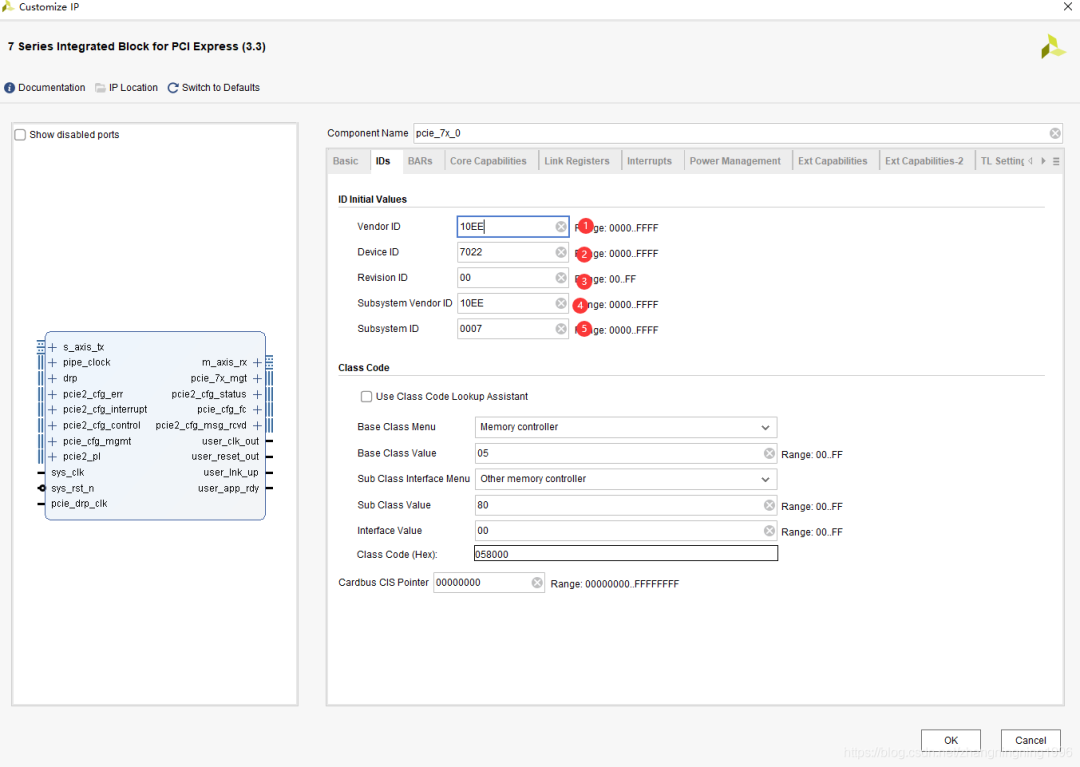

1、廠商ID,專屬于Xilinx的PCIE的ID,是固定的。

2、設備ID,與廠商ID一起指明數據的類型,被使用選擇PCIE上位機的軟件驅動。

3、版本ID,指明使用該PCIE IP進行設置的版本

4、子廠商ID,用來更近一步的區分Xilinx旗下的廠商

5、子系統ID,用來識別板卡的的ID

上面的值一般默認即可,不需要做太多的處理  ?

?

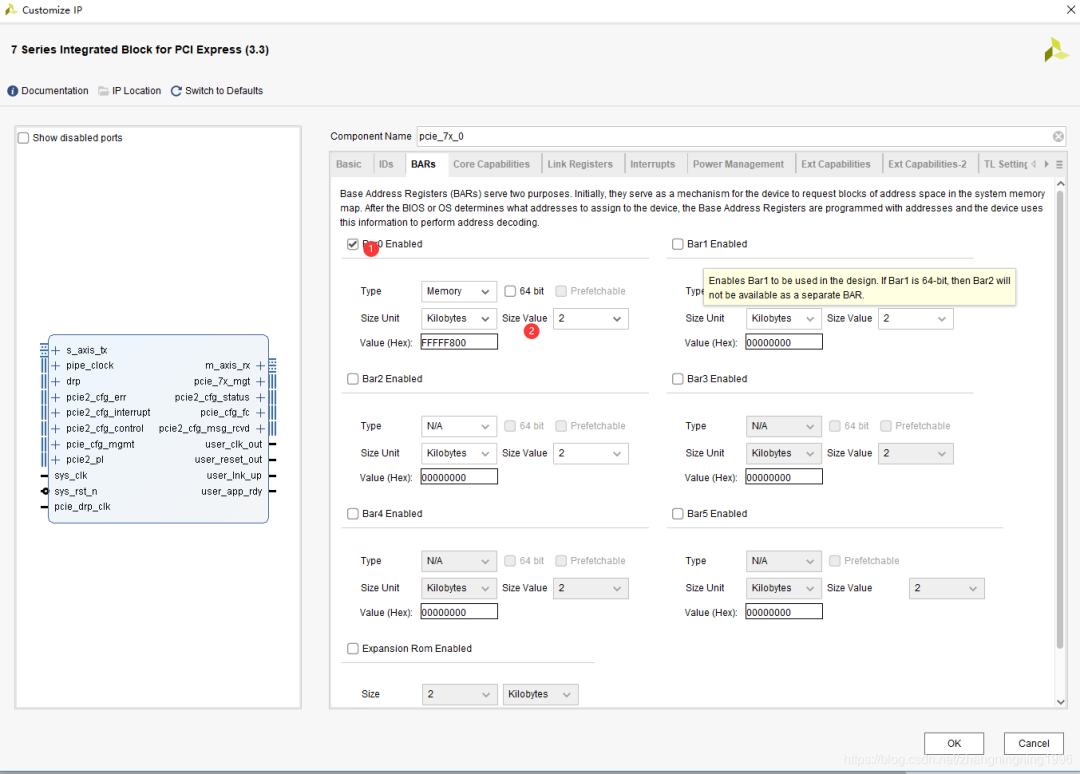

1、選擇使能Bar空間。這里需要注意的是,root port對于endpoint的訪問只能訪問bar空間,而endpoint對root port的讀寫操作可以訪問整個內存。

2、選擇Bar的地址是32位還是64位,空間大小一般選擇1K即可,只是用來傳輸一些命令。其值的大小與空間大小有關,具體的關系這里不清楚。

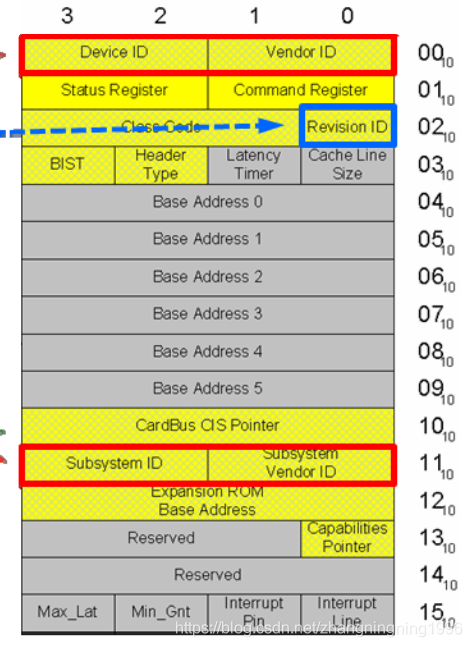

上面整個設置,再PCIE的頭配置空間中均有體現:

?

?

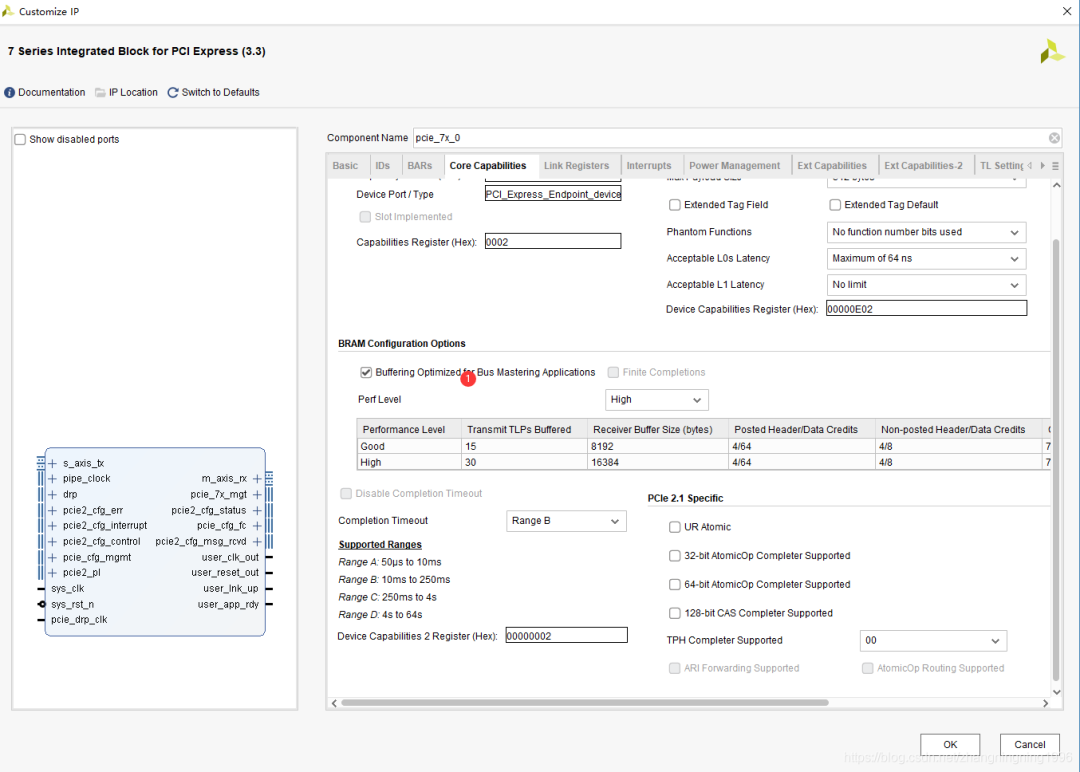

1、這里可以加上buffer進行優化,其余的默認即可。  ?

?

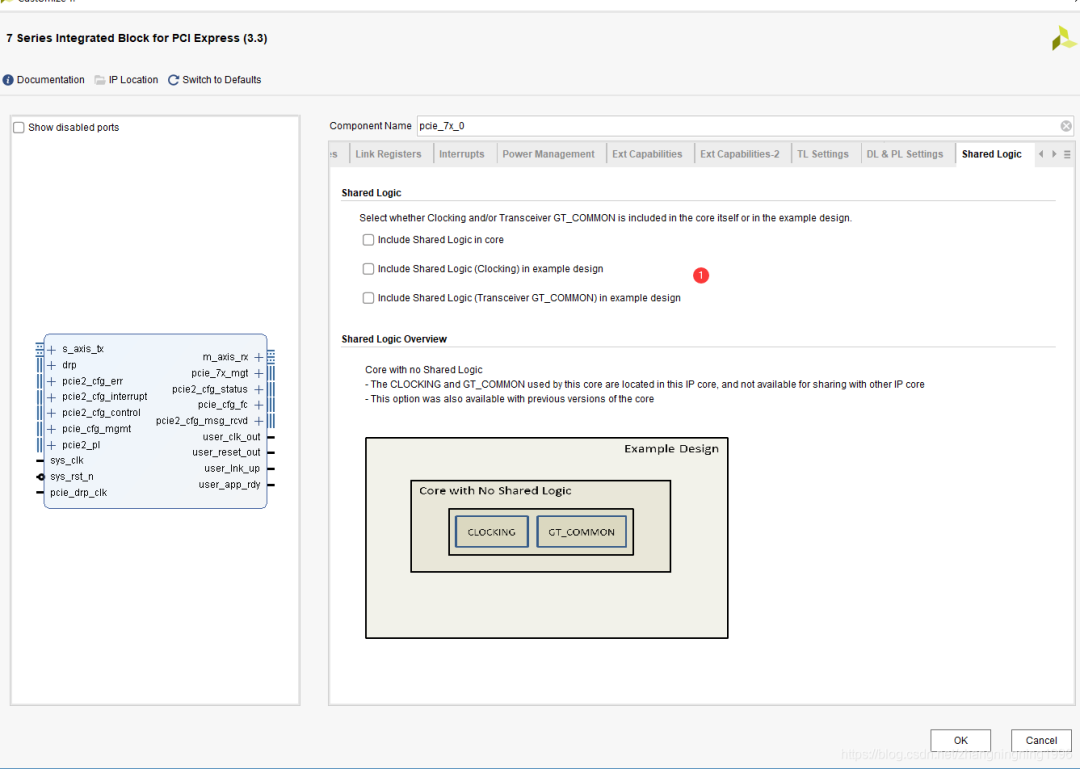

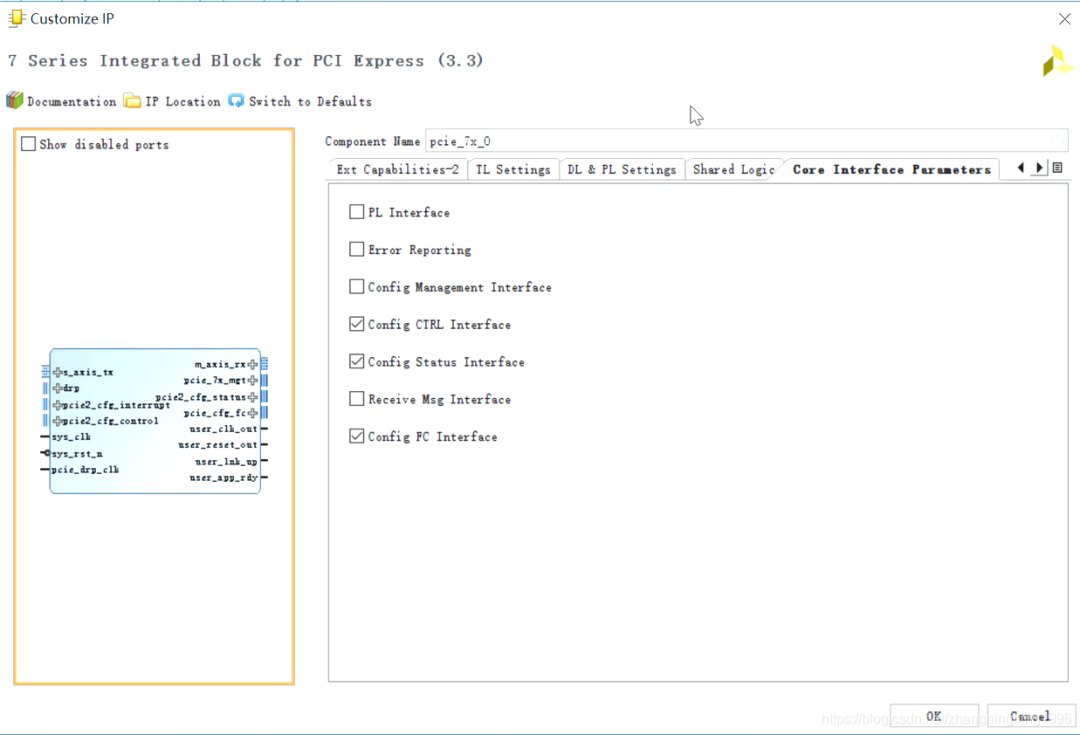

1、這里我們一般不選擇共享邏輯  ?

?

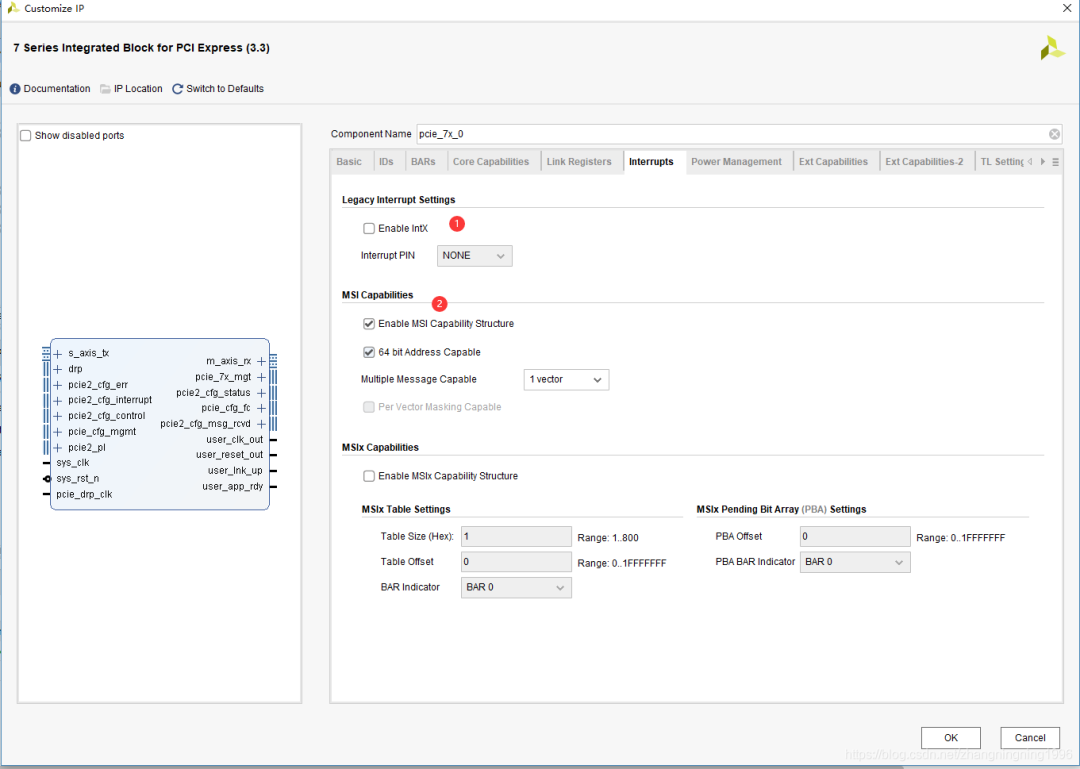

1、引腳中斷,傳統意義下的中斷,在PCIE中基本上不再使用 2、消息中斷,在PCIE中較為常用  ?

?

審核編輯:劉清

-

FPGA

+關注

關注

1640文章

21897瀏覽量

611341 -

PCI

+關注

關注

5文章

675瀏覽量

131146 -

嵌入式計算機

+關注

關注

0文章

64瀏覽量

12359 -

交換器

+關注

關注

2文章

92瀏覽量

16694 -

PCIe接口

+關注

關注

0文章

121瀏覽量

9976

原文標題:基于FPGA的PCIE設計(1)

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于FPGA的PCIE總線擴展卡的設計

FPGA的PCIE接口應用需要注意哪些問題

6678 pcie和FPGA接口

尋求fpga大牛開發一個簡單的fpga pcie設備

如何通過PCIe進行FPGA到PC的通信?

如何利用PCIe DMA總線實現一個基于FPGA的PCIe 8位數據采集卡?

PCIE總線的FPGA設計方法

基于PCIE總線的多DSP系統接口設計

基于FPGA的PCIe總線接口的DMA控制器的實現并進行仿真驗證

基于FPGA的PCIe設備如何才能滿足PCIe設備的啟動時間的要求?

如何使用FPGA的PCIe總線進行DMA平臺設計

評論