我們通過這篇文章來給大家分享DDRx關鍵技術,希望能解答一些朋友的疑問。

一、差分時鐘技術

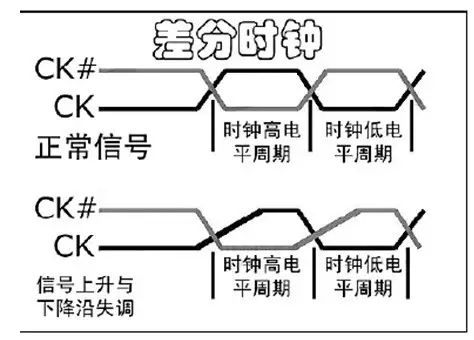

差分時鐘是DDR的一個重要且必要的設計,但大家對CK#(CKN)的作用認識很少,很多人理解為第二個觸發時鐘,其實它的真實作用是起到觸發時鐘校準的作用。

由于數據是在CK的上下沿觸發,造成傳輸周期縮短了一半,因此必須要保證傳輸周期的穩定以確保數據的正確傳輸,這就要求CK的上下沿間距要有精確的控制。但因為溫度、電阻性能的改變等原因,CK上下沿間距可能發生變化,此時與其反相的CK#(CKN)就起到糾正的作用(CK上升快下降慢,CK#則是上升慢下降快),如下圖一所示。

圖一 差分時鐘示意圖

二、數據選取脈沖(DQS)

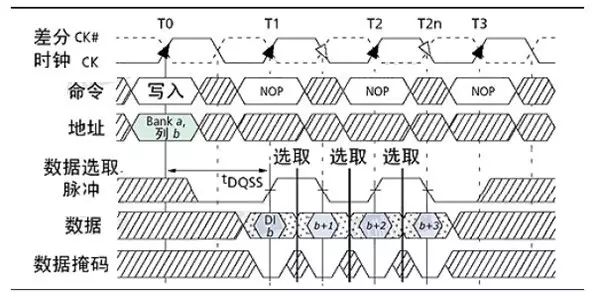

就像時鐘信號一樣,DQS也是DDR中的重要功能,它的功能主要用來在一個時鐘周期內準確的區分出每個傳輸周期,并便于接收方準確接收數據。每一顆8bit DRAM芯片都有一個DQS信號線,它是雙向的,在寫入時它用來傳送由主控芯片發來的DQS信號,讀取時,則由DRAM芯片生成DQS向主控發送。完全可以說,它就是數據的同步信號。

在讀取時,DQS與數據信號同時生成(也是在CK與CK#的交叉點)。而DDR內存中的CL也就是從CAS發出到DQS生成的間隔,數據真正出現在數據I/O總線上相對于DQS觸發的時間間隔被稱為tAC。實際上,DQS生成時,芯片內部的預取已經完畢了,由于預取的原因,實際的數據傳出可能會提前于DQS發生(數據提前于DQS傳出)。由于是并行傳輸,DDR內存對tAC也有一定的要求,對于DDR266,tAC的允許范圍是±0.75ns,對于DDR333,則是±0.7ns,其中CL里包含了一段DQS的導入期。

DQS 在讀取時與數據同步傳輸,那么接收時也是以DQS的上下沿為準嗎?不,如果以DQS的上下沿區分數據周期的危險很大。由于芯片有預取的操作,所以輸出時的同步很難控制,只能限制在一定的時間范圍內,數據在各I/O端口的出現時間可能有快有慢,會與DQS有一定的間隔,這也就是為什么要有一個tAC規定的原因。

而在接收方,一切必須保證同步接收,不能有tAC之類的偏差。這樣在寫入時,DRAM芯片不再自己生成DQS,而以發送方傳來的DQS為基準,并相應延后一定的時間,在DQS的中部為數據周期的選取分割點(在讀取時分割點就是上下沿),從這里分隔開兩個傳輸周期。這樣做的好處是,由于各數據信號都會有一個邏輯電平保持周期,即使發送時不同步,在DQS上下沿時都處于保持周期中,此時數據接收觸發的準確性無疑是最高的,如下圖二所示。

圖二 數據時序

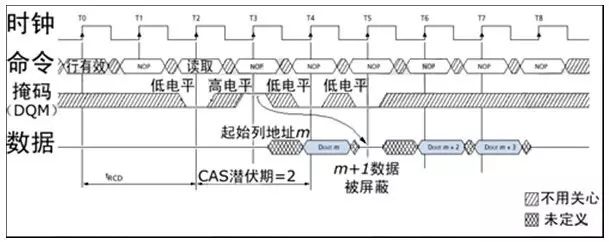

三、數據掩碼技術(DQM)

不是DDR所特有的,但對于DDR來說也是比較重要的技術,所以一并介紹下。

為了屏蔽不需要的數據,人們采用了數據掩碼(Data I/O Mask,簡稱DQM)技術。通過DQM,內存可以控制I/O端口取消哪些輸出或輸入的數據。這里需要強調的是,在讀取時,被屏蔽的數據仍然會從存儲體傳出,只是在“掩碼邏輯單元”處被屏蔽。

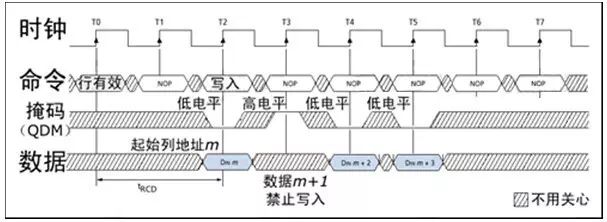

DQM由主控芯片控制,為了精確屏蔽一個P-Bank位寬中的每個字節,每個64bit位寬的數據中有8個DQM信號線,每個信號針對一個字節。這樣,對于4bit位寬芯片,兩個芯片共用一個DQM 信號線,對于8bit位寬芯片,一個芯片占用一個DQM信號,而對于16bit位寬芯片,則需要兩個DQM引腳。SDRAM 官方規定,在讀取時DQM發出兩個時鐘周期后生效,而在寫入時,DQM與寫入命令一樣是立即生效,如下圖三和四分別顯示讀取和寫入時突發周期的第二筆數據被取消。

圖三 讀取時數據掩碼操作

圖四 寫入時數據掩碼操作

所以DQM信號的作用就是對于突發寫入,如果其中有不想存入的數據,就可以運用DQM信號進行屏蔽。DQM信號和數據信號同時發出,接收方在DQS的上升與下降沿來判斷DQM的狀態,如果DQM為高電平,那么之前從DQS中部選取的數據就被屏蔽了。

有人可能會覺得,DQM是輸入信號,意味著DRAM芯片不能發出DQM信號給主控芯片作為屏蔽讀取數據的參考。其實,該讀哪個數據也是由主控芯片決定的,所以DRAM芯片也無需參與主控芯片的工作,哪個數據是有用的就留給主控芯片自己去選擇。

審核編輯:劉清

-

DDR

+關注

關注

11文章

730瀏覽量

66290 -

DRAM芯片

+關注

關注

1文章

88瀏覽量

18253 -

邏輯電平

+關注

關注

0文章

181瀏覽量

14674 -

差分時鐘

+關注

關注

0文章

10瀏覽量

4676 -

dqs

+關注

關注

0文章

7瀏覽量

2383

原文標題:DDRx的關鍵技術介紹(二)

文章出處:【微信號:Ithingedu,微信公眾號:安芯教育科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

評論