Howie Jing and Patrick Wiers

AD9361是一款高性能、高度集成的射頻(RF)捷變收發器?,設計用于 3G 和 4G 應用。AD9361的可編程性和寬帶能力,特別是其通道帶寬范圍從小于200 kHz到56 MHz,功耗低,使其成為各種收發器應用的理想選擇。AD9361推薦用于小型蜂窩應用的新設計,在這些應用中,需要寬帶寬來支持載波必須連續的多載波應用。

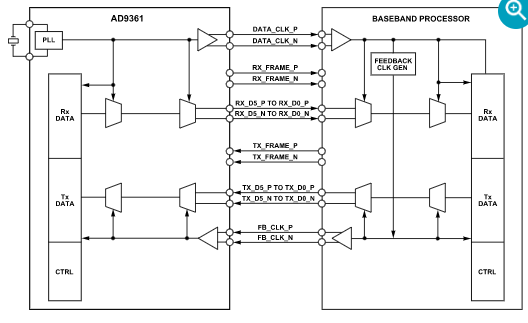

為了支持寬帶寬,必須考慮發射器(Tx)輸出線性度、本振(LO)泄漏和低壓差分信號(LVDS)接口等因素。本應用筆記主要討論支持56 MHz帶寬所需的LVDS接口。圖1顯示了AD9361與具有LVDS接口的定制專用集成電路(ASIC)和現場可編程門陣列(FPGA)之間的連接。接口細節在AD9361數據手冊中討論。本應用筆記重點介紹偽隨機二進制序列(PRBS)校準方法,以使該接口在工藝和溫度變化范圍內更加可靠。

圖1.AD9361 LVDS模式下的數據路徑

問題描述

請注意,就本應用筆記而言,所有對RX_Dx(x = 0至5)、TX_Dx(x = 0至5)、DATA_CLK、RX_FRAME、TX_FRAME和FB_CLK的引用僅指信號。RX_Dx信號是RX_Dx_P和RX_Dx_N引腳上的信號。TX_Dx信號是TX_Dx_P引腳和TX_Dx_N引腳上的差分信號。DATA_CLK信號是DATA_CLK_P引腳和DATA_CLK_N引腳上的差分信號。RX_FRAME信號是RX_FRAME_P引腳和RX_FRAME_N引腳上的差分信號。TX_FRAME信號是TX_FRAME_P引腳和TX_FRAME_N引腳上的差分信號,FB_CLK是FB_CLK_P和FB_CLK_N引腳上的差分信號。

LVDS定時參數

為了支持56 MHz帶寬,AD9361的I/Q數據速率必須設置為最大值61.44 MSPS。對于 2T2R 操作,DATA_CLK信號必須以 4× I/Q 速率 245.76 MHz 運行。在此速率下LVDS數據總線的時序約束如表1所示。

| 參數 | 最小值 | 典型值 | 麥克斯 | 單位 | 描述 |

| t正中電 | 4.069 | 納 | DATA_CLK周期時間(時鐘周期) | ||

| t議員 | t的45%正中電 | t的55%正中電 | DATA_CLK信號和FB_CLK信號高和/或低最小脈沖寬度(包括占空比失真、周期抖動、周期間抖動和半周期抖動的影響) | ||

| tSTX | 1 | 納 | TX_D5 TX_D0和TX_FRAME信號建立時間,以FB_CLK AD9361輸入端的信號下降沿 | ||

| t高超 | 0 | 納 | TX_D5至TX_D0和TX_FRAME信號保持AD9361輸入端FB_CLK信號下降沿的時間 | ||

| tDDRX | 0.25 | 1.25 | 納 | 從DATA_CLK到RX_D5到RX_D0輸出信號的延遲 | |

| tDDDV | 0.25 | 1.25 | 納 | 從DATA_CLK信號到RX_FRAME信號的延遲 |

對與基帶處理器連接的影響

當時鐘速率為245.76 MHz時,DATA_CLK的周期時間為4.069 ns,最小脈沖寬度為占空比的45%,約為1.83 ns,如表1所示。與該脈沖寬度相比,延遲(tDDRX和 tDDDV) 從DATA_CLK信號到RX_D5到RX_D0信號,或RX_FRAME信號的最大速率為 1.25 ns。

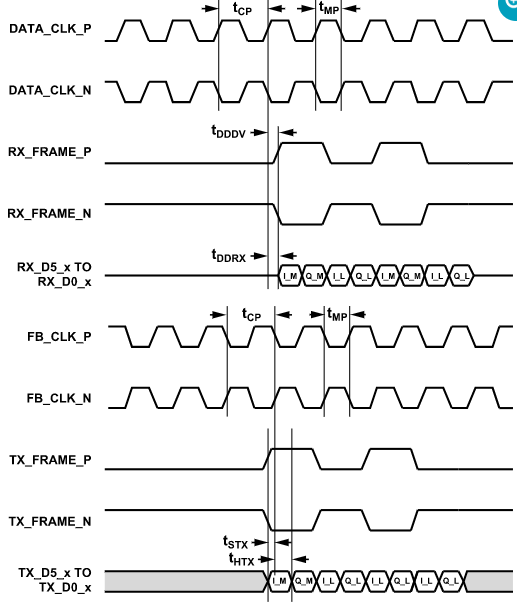

圖2顯示了AD9361中的時序圖。

圖2.數據端口時序參數圖—LVDS 總線配置(其中 x 表示 p 和 n 引腳)。

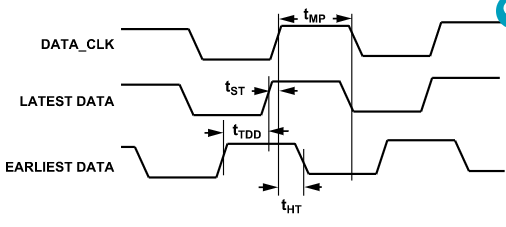

圖3顯示了基帶處理器中的時序圖。

圖3.基帶處理器中的時序圖。

在圖 3 中,tTDD是包括 t 在內的總延遲差值DDRX在AD9361(1.25 ns)中,數據通過印刷電路板(PCB)傳播的路徑延遲差和類似于tDDRX在基帶處理器設備中。對于最壞情況,該值大于 1.25 ns。例如,假設為 1.5 ns,則數據設置的剩余時間 (t圣) 并保持 (tHT)僅為0.33 ns,這很有挑戰性(見圖3),因為即使在工作臺上在一個溫度下滿足時序,也很難在工藝和溫度變化范圍內保持可靠性。

為了使此接口在245.76 MHz下可用,建議進行校準以校正延遲差(tTDD),介于AD9361和基帶處理器之間。

PRBS 校準詳情

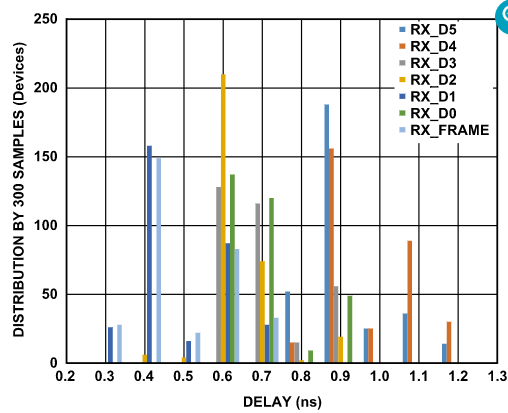

延遲變化測試結果

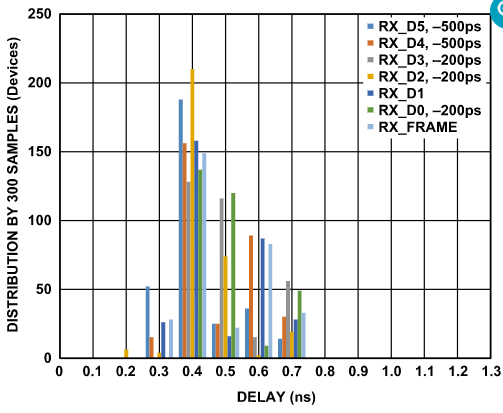

圖 4 顯示了 0 個器件上 5 個RX_D300到 RX_D1 對和DATA_CLK RX_FRAME的延遲變化。這些數字信號彼此具有非常不同的延遲值。最大延遲接近2.0 ns;但是,最短延遲僅為3.0 ns,差異可能為9.<> ns。

圖4.RX_DATA信號的延遲分布和來自DATA_CLK信號的RX_FRAME信號。

基帶處理器中的延遲補償

圖4顯示了另一種現象,例如,最大的延遲主要發生在接近4.1 ns的RX_D2上;但是,在RX_D1上,延遲最大值僅為0.7 ns左右。RX_D4和RX_D1之間的差異為0.5 ns;因此,最好在RX_D0上補償5.1 ns的延遲,然后RX_D4可以與RX_D1對齊。此方法可以擴展到其他RX_D5到RX_D0對和RX_FRAME,也可以TX_D5擴展到TX_D0。

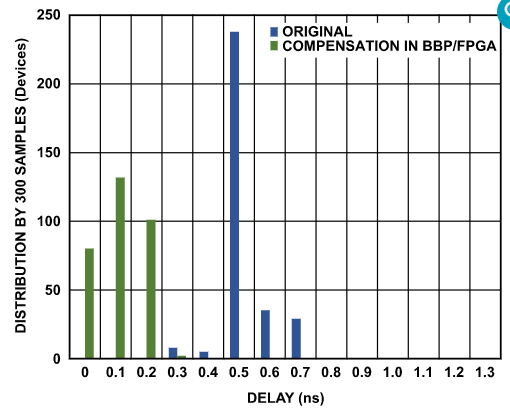

例如,如果這些補償可以在基帶處理器中分別對每個RX_D5進行,以更高的精度RX_D0,如圖4所示,對RX_D500和RX_D5進行了?4 ps的延遲校正,對RX_D200、RX_D3和RX_D2進行了?0 ps的延遲校正, 如圖 5 所示的結果是可能的。延遲更集中在0.2 ns和0.7 ns之間,性能大大提高。

圖5.校正后的延遲分布。

可以在每個設備上調整校準;因此,在單個AD5器件上研究RX_D0 RX_D9361對與DATA_CLK之間的延遲差異更有意義。在圖6中,藍色條顯示了這種延遲差異在300個器件中的分布,沒有任何補償。大多數器件的延遲差集中在0.5 ns,最大值為0.7 ns。采用上一段中描述的相同補償,分布向較低的延遲差,如圖6中的綠色條所示。最大延遲差為0.3 ns,提高了0.4 ns。

圖6.單個設備上延遲差的分布。

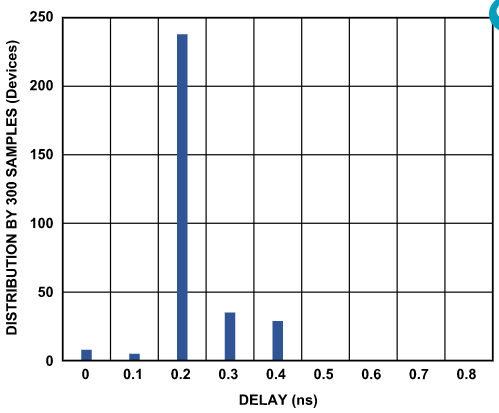

AD9361中的延遲補償

基帶處理器可能無法通過RX_D5 RX_D0來校正延遲差,或者根本無法進行延遲補償。此問題的解決方案是在AD9361中使用Rx寄存器0x006和Tx寄存器0x007進行補償,以調整RX_D5至RX_D0與DATA_CLK信號(或TX_D5至TX_D0和FB_CLK信號)之間的相對延遲,最小有效位(LSB)精度約為0.3 ns。請注意,此延遲會影響具有相同值的所有數據對。AD9361無法單獨調整數據對的延遲。但是,這種補償仍然使校準可行。圖7顯示了在AD300的寄存器0x006中校正9361 ps延遲時的結果。圖7所示結果表明,延遲差主要分布在0.1 ns和0.4 ns之間,最大延遲降低到0.4 ns,時序為t圣+ 噸HT(在圖3中)基帶處理器的裕量更大(約1.4 ns),這保證了工藝和溫度變化的可靠性。

圖7.AD9361中延遲差與延遲校正的分布

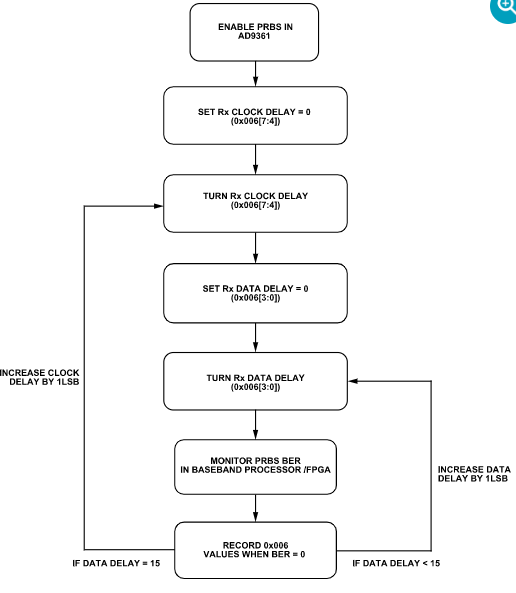

PRBS校準

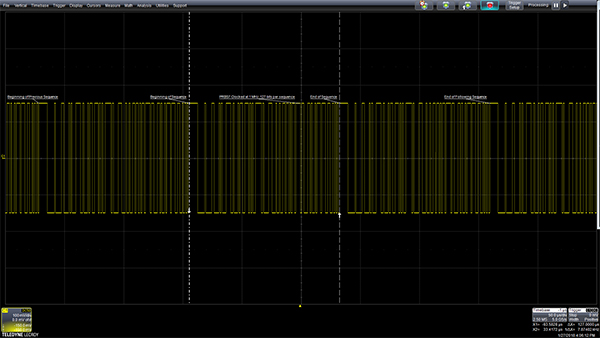

AD9361集成的PRBS發生器提供了一種確定需要多少延遲補償的方法。該PRBS可以注入AD9361的接口,并傳輸到基帶處理器。基帶處理器收到此已知序列后,可以實現PRBS檢查器來計算誤碼率(BER)。如果收到的 PRBS 上沒有發生錯誤,則接口工作正常。否則,調整AD9361或基帶處理器中的延遲補償模塊,直到誤碼率降至所需閾值以下。

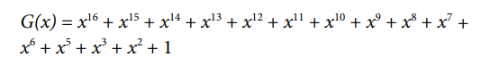

AD9361內置一個16級、14抽頭PRBS發生器,使用16千-階多項式如下式所示。

PRBS生成和多項式方程的詳細描述參考AD9361寄存器映射,寄存器0x3F4。

按照圖8所示的上述校準順序,可以產生如表2所示的基質。在表 2 中,P 表示 PRBS 測試通過,F 表示失敗。在此示例中,注冊0x006的值可以是0x96、0xA7、0xB8、0xC9或0xDA。

圖8.校準順序。

| 寄存器 0x006[7:4] 位值 | 寄存器 0x006[3:0] 位值 | |||||||||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 一個 | b | c | d | e | f | |

| 0 | P | F | F | F | F | F | F | F | F | F | P | P | P | F | F | F |

| 1 | P | F | F | F | F | F | F | F | F | F | F | F | F | F | P | P |

| 2 | P | P | F | F | F | F | F | F | F | F | F | F | F | F | F | P |

| 3 | P | P | P | F | F | F | F | F | F | F | F | F | F | F | F | F |

| 4 | P | P | P | P | F | F | F | F | F | F | F | F | F | F | F | F |

| 5 | F | P | P | P | P | F | F | F | F | F | F | F | F | F | F | F |

| 6 | F | P | P | P | P | P | F | F | F | F | F | F | F | F | F | F |

| 7 | F | F | P | P | P | P | P | F | F | F | F | F | F | F | F | F |

| 8 | F | F | F | F | P | P | P | P | F | F | F | F | F | F | F | F |

| 9 | F | F | F | F | P | P | P2 | P | P | F | F | F | F | F | F | F |

| 一個 | F | F | F | F | F | P | P | P2 | P | P | F | F | F | F | F | F |

| b | F | F | F | F | F | F | P | P | P2 | P | P | F | F | F | F | F |

| c | F | F | F | F | F | F | F | P | P | P2 | P | P | F | F | F | F |

| d | F | F | F | F | F | F | F | F | P | P | P2 | P | P | F | F | F |

| e | F | F | F | F | F | F | F | F | F | P | P | P | P | P | F | F |

| f | F | F | F | F | F | F | F | F | F | F | P | P | P | P | P | F |

|

1P = PRBS 測試通過,F = PRBS 測試失敗。 2延遲設置的最佳值。這些值在兩個方向上至少有兩個LSB(約0.6 ns)的保護裕量,這通常足以應對工藝變化和溫度范圍變化 |

||||||||||||||||

在寄存器0x006上為接收器(Rx)延遲選擇適當的設置后,可以使用相同的方法和順序在Tx LVDS路徑上運行校準程序。這一次,在校準Tx LVDS路徑時,可以在基帶處理器中生成偽隨機二進制序列,并傳輸到AD9361的Tx接口。在AD9361中,內部電路可以將TX_D5環路TX_D0到RX_D5到RX_D0路徑,然后將數據傳輸回基帶處理器,PRBS檢查器與其原始序列進行比較,并確定如何調整寄存器0x007中的延遲,以實現與表2所示類似的矩陣。

結論

本文檔介紹了LVDS路徑延遲上的PRBS校準,以支持245.76 MHz數據時鐘(最大帶寬為56 MHz)。因此,當對Rx數據進行校準時,數據對的延遲變化顯著改善至0.3 ns(基帶處理器中的補償)或0.4 ns(AD9361中的補償)。

兩種補償使高速LVDS接口具有余量,以克

審核編輯:郭婷

-

收發器

+關注

關注

10文章

3559瀏覽量

107125 -

射頻

+關注

關注

106文章

5719瀏覽量

169468 -

lvds

+關注

關注

2文章

1076瀏覽量

66930

發布評論請先 登錄

如何使用PRBS和CMOS器件生成偽隨機噪聲和二進制序列

評論