閃存模數(shù)轉(zhuǎn)換器,也稱為并行ADC,是將模擬信號轉(zhuǎn)換為數(shù)字信號的最快方法。閃存ADC適用于需要超大帶寬的應(yīng)用。但是,這些轉(zhuǎn)換器消耗相當(dāng)大的功率,分辨率相對較低,并且可能非常昂貴。這限制了它們通常無法以其他方式解決的高頻應(yīng)用。典型示例包括數(shù)據(jù)采集、衛(wèi)星通信、雷達(dá)處理、采樣示波器和高密度磁盤驅(qū)動器。

建筑細(xì)節(jié)

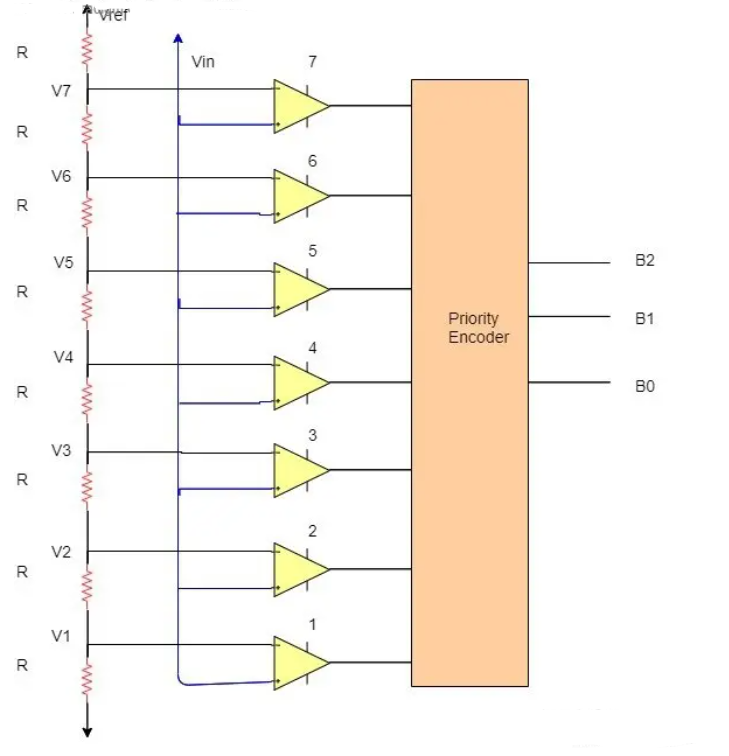

閃存ADC由級聯(lián)高速比較器組成。圖1所示為典型的閃存ADC框圖。對于N位轉(zhuǎn)換器,電路采用2N-1 個比較器。電阻分壓器,帶 2N電阻提供基準(zhǔn)電壓。每個比較器的基準(zhǔn)電壓比其正下方比較器的基準(zhǔn)電壓大一個最小有效位(LSB)。當(dāng)每個比較器的模擬輸入電壓高于施加在其上的基準(zhǔn)電壓時,每個比較器產(chǎn)生1。否則,比較器輸出為0。因此,如果模擬輸入在V之間X4和 VX5、比較器 X1通過 X4產(chǎn)生1s,其余比較器產(chǎn)生0s。代碼從 <> 變?yōu)?<> 的點是輸入信號小于相應(yīng)比較器基準(zhǔn)電壓電平的點。

圖1.閃存 ADC 架構(gòu)。如果模擬輸入介于 V 之間X4和 VX5、比較器 X1通過 X4產(chǎn)生1s,其余比較器產(chǎn)生0s。

這種體系結(jié)構(gòu)稱為溫度計代碼編碼。之所以使用這個名稱,是因為該設(shè)計類似于水銀溫度計,其中汞柱始終上升到適當(dāng)?shù)臏囟龋⑶以谠摐囟纫陨喜淮嬖诠H缓髮囟扔嫶a解碼為適當(dāng)?shù)臄?shù)字輸出代碼。

比較器通常是寬帶低增益級級的級聯(lián)。它們是低增益的,因為在高頻下很難同時獲得寬帶寬和高增益。比較器設(shè)計用于低壓失調(diào),因此每個比較器的輸入失調(diào)小于ADC的LSB。否則,比較器的失調(diào)可能會錯誤地使比較器跳閘,導(dǎo)致數(shù)字輸出代碼不代表溫度計代碼。每個比較器輸出端的再生鎖存器存儲結(jié)果。鎖存器具有正反饋,因此最終狀態(tài)被強(qiáng)制為 1 或 0。

鑒于這些基礎(chǔ)知識,需要進(jìn)行一些調(diào)整來優(yōu)化閃存轉(zhuǎn)換器架構(gòu)。

閃光代碼

通常,比較器輸出將是溫度計代碼,例如00011111。錯誤可能會導(dǎo)致類似00010111的輸出,這意味著結(jié)果中存在虛假零。這種亂序0稱為閃光,這是由不完美的輸入建立或比較器時序不匹配引起的。誤差的大小可能非常大。MAX109/MAX104等現(xiàn)代轉(zhuǎn)換器在ADC前面采用輸入采樣保持以及抑制閃爍碼的編碼技術(shù)。

亞穩(wěn)態(tài)

當(dāng)比較器的數(shù)字輸出不明確(既不是1也不是0)時,輸出定義為亞穩(wěn)態(tài)。通過留出更多再生時間可以降低亞穩(wěn)態(tài)。格雷碼編碼一次只允許輸出中的1位變化,可以大大提高亞穩(wěn)定性。.因此,比較器輸出首先轉(zhuǎn)換為格雷碼編碼,然后根據(jù)需要解碼為二進(jìn)制。

當(dāng)亞穩(wěn)輸出驅(qū)動兩個不同的電路時,會出現(xiàn)另一個問題。一個電路可以將輸入聲明為1,而另一個電路認(rèn)為輸入為0。這可能會產(chǎn)生重大錯誤。為了避免這種沖突,只有一個電路應(yīng)檢測潛在的可測量輸出。

輸入信號頻率依賴性

當(dāng)輸入信號在所有比較器完成其任務(wù)之前發(fā)生變化時,ADC的性能會受到不利影響。最嚴(yán)重的影響是隨著模擬輸入頻率的增加,信噪比(SNR)加失真(SINAD)下降。

測量無雜散動態(tài)范圍(SFDR)是觀察轉(zhuǎn)換器性能的另一種好方法。ADC實現(xiàn)的“有效位”是輸入頻率的函數(shù);通過在ADC前面增加一個采樣保持(T/H)電路,可以對其進(jìn)行改進(jìn)。T/H電路允許顯著改善,特別是當(dāng)輸入頻率接近奈奎斯特頻率時,如圖2所示(取自MAX104數(shù)據(jù)資料)。沒有 T/H 的零件在 SFDR 中顯示出顯著下降。

圖2.無雜散動態(tài)范圍與輸入頻率的函數(shù)關(guān)系。

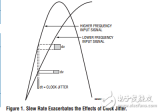

時鐘抖動

當(dāng)采樣時鐘中存在抖動時,SNR會降低。對于高模擬輸入頻率,這一點變得很明顯。為了獲得準(zhǔn)確的結(jié)果,為ADC提供低抖動采樣時鐘源至關(guān)重要。

架構(gòu)權(quán)衡

ADC可以通過采用各種架構(gòu)來實現(xiàn)。這些替代方案之間的主要權(quán)衡是:

完成轉(zhuǎn)換所需的時間(轉(zhuǎn)換時間)。對于閃存轉(zhuǎn)換器,轉(zhuǎn)換時間不會隨著分辨率的提高而發(fā)生重大變化。然而,逐次逼近寄存器(SAR)或流水線轉(zhuǎn)換器的轉(zhuǎn)換時間隨著分辨率的提高而近似線性增加(圖3a)。對于集成ADC,分辨率每提高一位,轉(zhuǎn)換時間就會翻倍。

電路中的元件匹配要求。閃存ADC組件匹配通常將分辨率限制在8位左右。校準(zhǔn)和調(diào)整有時用于改善芯片上可用的匹配。組件匹配要求隨著分辨率的提高而翻倍。此模式適用于閃存、逐次逼近或流水線轉(zhuǎn)換器,但不適用于集成轉(zhuǎn)換器。對于集成轉(zhuǎn)換器,元件匹配不會隨著分辨率的提高而大幅增加(圖 3b)。

芯片尺寸、成本和功耗。對于閃存轉(zhuǎn)換器,分辨率每提高一位,ADC內(nèi)核電路的尺寸就會增加一倍。功率也翻了一番。相比之下,SAR、流水線或Σ-Δ型ADC芯片尺寸將隨著分辨率的提高而線性增加;積分轉(zhuǎn)換器內(nèi)核芯片尺寸不會隨著分辨率的增加而發(fā)生實質(zhì)性變化(圖 3c)。最后,眾所周知,芯片尺寸的增加會增加成本。

圖3.架構(gòu)權(quán)衡。

閃存 ADC 與其他 ADC 架構(gòu)的比較

閃存 ADC 與 SAR ADC

在SAR轉(zhuǎn)換器中,單個高速、高精度比較器確定位,一次確定一位(從MSB到LSB)。這是通過將模擬輸入與DAC進(jìn)行比較來完成的,DAC的輸出由先前確定的位更新,從而連續(xù)接近模擬輸入。SAR的這種串行特性將其速度限制在不超過每秒幾兆采樣(Msps),而閃存ADC則超過每秒千兆采樣(Gsps)轉(zhuǎn)換速率。

SAR 轉(zhuǎn)換器的分辨率高達(dá) 16 位。這種器件的一個例子是MAX1132。閃存ADC通常限制在8位左右。較慢的速度也使SAR ADC的功耗低得多。例如,MAX1106是一款8位SAR轉(zhuǎn)換器,在100.3V時功耗為3μA,轉(zhuǎn)換速率為25ksps。MAX104的功耗為5.25W,功耗比MAX16高約000,1106倍,最大采樣速率快40,000倍。

SAR 架構(gòu)也更便宜。1106k產(chǎn)量的MAX1售價超過一美元(美元),而MAX104的售價為幾百美元(美國)。閃存轉(zhuǎn)換器的封裝尺寸更大。除了更大的芯片尺寸需要更大的封裝外,封裝還需要消耗相當(dāng)大的功率,并且需要許多引腳來實現(xiàn)電源和接地信號完整性。MAX104的封裝尺寸是MAX50的1106倍以上。

閃存 ADC 與流水線 ADC

流水線ADC采用并聯(lián)結(jié)構(gòu),其中每級同時處理一到幾位連續(xù)采樣。這種設(shè)計以功耗和延遲為代價提高了速度,但每個流水線級都比閃存部分慢得多。流水線ADC要求DAC和級間放大器進(jìn)行精確放大,這些級必須穩(wěn)定到所需的線性度電平。相比之下,在閃存ADC中,比較器只需要低失調(diào),并將其輸入解析為數(shù)字電平;不涉及線性建立時間。一些閃存轉(zhuǎn)換器需要前置放大器來驅(qū)動比較器。需要仔細(xì)指定增益線性度。

流水線轉(zhuǎn)換器在 100 至 8 位分辨率下以大約 14Msps 的速度進(jìn)行轉(zhuǎn)換。流水線轉(zhuǎn)換器的一個例子是MAX1449,這是一款105MHz、10位ADC。對于給定的分辨率,流水線ADC比類似分辨率的閃存轉(zhuǎn)換器慢約10倍。流水線轉(zhuǎn)換器可能是需要以高達(dá)100Msps左右的速率采樣、分辨率為10位及以上的ADC的最佳架構(gòu)。對于高達(dá)10位的分辨率和幾百Msps以上的轉(zhuǎn)換速率,閃存ADC占主導(dǎo)地位。

有趣的是,在某些情況下,閃存ADC隱藏在采用另一種架構(gòu)以提高其速度的轉(zhuǎn)換器內(nèi)。

閃存與集成式ADC

單斜率、雙斜率和多斜率ADC可實現(xiàn)16位或更高的高分辨率,價格相對便宜,功耗也更小。這些器件支持非常低的轉(zhuǎn)換速率,通常每秒不到幾百個樣本。大多數(shù)應(yīng)用用于監(jiān)測儀器儀表和工業(yè)市場中的直流信號。這種架構(gòu)與Σ-Δ轉(zhuǎn)換器競爭。

閃存與Σ-Δ型ADC

閃存ADC不與Σ-Δ架構(gòu)競爭,因為目前可實現(xiàn)的轉(zhuǎn)換速率相差多達(dá)兩個數(shù)量級。Σ-Δ 架構(gòu)適用于帶寬低得多(通常小于 1MHz)且分辨率在 12 至 24 位范圍內(nèi)的應(yīng)用。Σ-Δ轉(zhuǎn)換器能夠在ADC中實現(xiàn)盡可能高的分辨率。它們需要更簡單的抗混疊濾波器(如果需要)來在轉(zhuǎn)換前對信號進(jìn)行帶寬限制。

Σ-Δ型ADC通過過采樣來換取速度分辨率,然后進(jìn)行濾波以降低噪聲。然而,這些器件對于多通道應(yīng)用并不總是有效的。此架構(gòu)可以使用采樣數(shù)據(jù)濾波器(也稱為調(diào)制器或連續(xù)時間濾波器)來實現(xiàn)。對于更高的頻率轉(zhuǎn)換速率,連續(xù)時間架構(gòu)有可能以6至8位的低分辨率達(dá)到數(shù)百Msps范圍內(nèi)的轉(zhuǎn)換速率。這種方法仍處于早期研發(fā)階段,與較低轉(zhuǎn)化率范圍內(nèi)的閃存替代品競爭。

閃存ADC的另一個有趣用途是作為Σ-Δ電路內(nèi)的構(gòu)建模塊,以提高ADC的轉(zhuǎn)換速率。

子范圍模數(shù)轉(zhuǎn)換器

當(dāng)需要更高分辨率的轉(zhuǎn)換器或更小的芯片尺寸和功率以獲得給定分辨率時,采用多級轉(zhuǎn)換。這種架構(gòu)稱為子范圍轉(zhuǎn)換器,有時也稱為多步或半閃存轉(zhuǎn)換器。這種方法結(jié)合了逐次逼近和閃存架構(gòu)的思想。

子范圍ADC減少了要轉(zhuǎn)換為較小組的位數(shù),然后通過較低分辨率的閃存轉(zhuǎn)換器運行。與閃存轉(zhuǎn)換器相比,這種方法減少了比較器的數(shù)量,并降低了邏輯復(fù)雜性(圖 4)。與閃存相比,這種權(quán)衡導(dǎo)致轉(zhuǎn)換速度較慢。

圖4.子范圍 ADC 架構(gòu)。

MAX153為8位、1Msps ADC,采用子量程架構(gòu)。該電路采用兩步技術(shù)。首先,使用4位轉(zhuǎn)換器完成轉(zhuǎn)換。產(chǎn)生殘差,其中8位精度DAC將4位轉(zhuǎn)換的結(jié)果轉(zhuǎn)換回模擬信號。從輸入信號中減去模擬信號。其次,該殘余再次由4位ADC轉(zhuǎn)換,并將第一遍和第二遍的結(jié)果組合在一起,提供8位數(shù)字輸出。

工藝技術(shù)

閃存轉(zhuǎn)換器的速度目前超過1Gsps。 2.2Gbps MAX109采用先進(jìn)的SiGE工藝制造。MAX108 (1.5Gsps)、MAX104 (1Gsps)和MAX106 (600Msps)8位ADC采用Maxim專有的先進(jìn)GST-2雙極性工藝(“千兆”速度硅雙極性工藝)制造。

與雙極性技術(shù)產(chǎn)品相比,CMOS閃存轉(zhuǎn)換器的分辨率較低。這些ADC通常用于集成到更大的CMOS電路中。CMOS、BiCMOS和雙極技術(shù)將繼續(xù)改進(jìn),產(chǎn)生越來越高的轉(zhuǎn)化率。

結(jié)論

對于要求中等分辨率(通常高達(dá)8位)且采樣頻率高達(dá)數(shù)百MHz的應(yīng)用,閃存架構(gòu)可能是唯一可行的替代方案。用戶必須提供低抖動時鐘,以確保良好的ADC性能。對于具有高模擬輸入頻率的應(yīng)用,所選的ADC應(yīng)具有內(nèi)部采樣保持功能。

審核編輯:郭婷

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8701瀏覽量

147152 -

驅(qū)動器

+關(guān)注

關(guān)注

52文章

8236瀏覽量

146331 -

adc

+關(guān)注

關(guān)注

98文章

6498瀏覽量

544576

發(fā)布評論請先 登錄

相關(guān)推薦

高速ADC時鐘抖動的影響的了解

閃存存儲器你了解多少

QLC閃存、TLC閃存是什么?QLC閃存、TLC閃存有何區(qū)別?

ADuC832:帶嵌入式62 kB閃存MCU的MicroConverter、12位ADC和DAC產(chǎn)品手冊

利用CTLE和時間交錯閃存ADC來降低ADC分辨率

了解PulSAR ADC支持電路

閃存模數(shù)轉(zhuǎn)換器(Flash ADC)概念框圖解

了解MSP430閃存數(shù)據(jù)保留

了解閃存ADC

了解閃存ADC

評論