本設計筆記顯示了一個電路,該電路修改了一個雙通道、電壓輸出數模轉換器(DAC),以節省功耗,并采用20V電源消耗小于5μA的電流。該電路可用于慢速或靜態應用中的可編程電壓生成,例如微功耗儀器中的失調歸零。

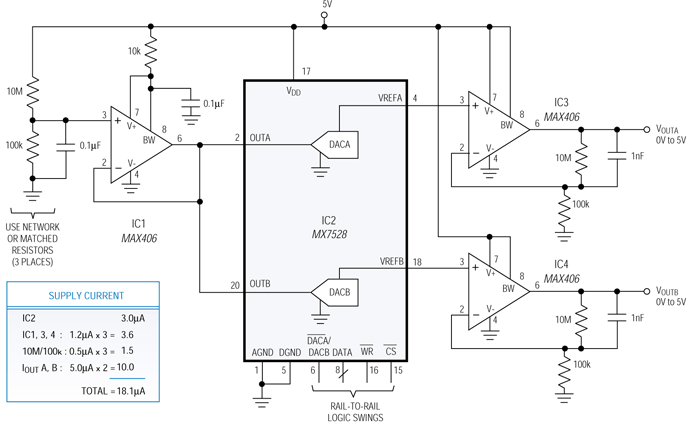

下圖所示的雙通道電壓輸出DAC采用多種省電技巧組合,從20V電源吸收小于5μA的電流。該電路適合慢速或靜態應用中可編程電壓生成的需求,例如微功耗儀器中的失調歸零。

該雙通道DAC電路提供兩個獨立的8位DAC,具有電壓輸出和一個公共基準,采用20V電源吸收的電流小于5μA。

電流輸出DAC通常通過路由I的補碼來浪費功率外接地。圖中的電路通過在反向電壓開關模式下操作每個DAC來避免功耗浪費,在該模式下,基準電壓施加到通常標記為I的引腳上外.

本電路中的OUT引腳具有恒定且相對較低的輸入阻抗(11kΩ)。為了減小輸入電流,基準電壓被分壓100 (從5V到50mV),因此僅向每個DAC輸入提供5μA電流。信號電平通過每個輸出放大器中的100補償增益恢復。廉價的 10MΩ/100kΩ 電阻網絡是需要多個 100:1 衰減器的不錯選擇。雖然精度僅為2%,但它們的匹配和跟蹤比分立電阻器要好得多。

更大的縮放是不切實際的,因為所示輸出放大器的失調為0.5mV (最大值)。放大100時,這些失調會產生±1%(0.05V)的最差輸出誤差。誤差在整個溫度范圍內是恒定的,但在40°C范圍內由于漂移引起的額外誤差通常為±<>/<> LSB。圖中所示的微功耗輸出放大器因其低電源電流而被選中,典型功耗為IDD僅 1μA。

最小化總電流消耗的最后一個要求是確保施加到IC1數字輸入的邏輯信號擺幅在每個供電軌的0.2V以內。指定的最大值 IDD對于該條件,整個溫度為100μA,但此規格(與大多數CMOS I一樣)DD收視率)極其保守。我DD對于軌到軌擺動可以忽略不計,但隨著擺動接近 TTL 水平,擺幅會急劇上升。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17761瀏覽量

250653 -

放大器

+關注

關注

143文章

13612瀏覽量

213668 -

dac

+關注

關注

43文章

2297瀏覽量

191169

發布評論請先 登錄

相關推薦

DAC856X,DAC816X和DAC756X低功耗電壓輸出雙通道數模轉換器資料概述

DAC53xAxW具有I2C或SPI的10位三通道和雙通道電壓輸出和電流輸出智能DAC數據表

DAC82002 16位、低毛刺脈沖、雙通道電壓輸出、非緩沖DAC數據表

DAC7571低功耗、單通道、12位緩沖電壓輸出DAC數據表

DAC5571低功耗、單通道、8位緩沖電壓輸出DAC數據表

DAC8552雙通道、電壓輸出數模轉換器(DAC)數據表

雙通道、電壓輸出DAC功耗極低

雙通道、電壓輸出DAC功耗極低

評論