在設(shè)計(jì)中使用超快速數(shù)據(jù)轉(zhuǎn)換器的高速應(yīng)用通常需要非常干凈的時(shí)鐘信號(hào),以確保外部時(shí)鐘源不會(huì)對(duì)系統(tǒng)的整體動(dòng)態(tài)性能產(chǎn)生不需要的噪聲。因此,選擇合適的系統(tǒng)組件至關(guān)重要,這有助于產(chǎn)生低相位抖動(dòng)時(shí)鐘。以下應(yīng)用筆記可作為選擇合適的元件的寶貴指南,以設(shè)計(jì)適用于超快速數(shù)據(jù)轉(zhuǎn)換器的基于PLL的低相位噪聲時(shí)鐘發(fā)生器。

介紹

許多現(xiàn)代、高速、高性能集成電路,如MAX104和MAX106模數(shù)轉(zhuǎn)換器(ADC),都需要工作在GHz范圍內(nèi)的低相位噪聲(低抖動(dòng))時(shí)鐘。傳統(tǒng)的晶體振蕩器可以提供低抖動(dòng)時(shí)鐘信號(hào),但通常不能在120MHz以上的振蕩頻率中使用。

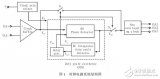

圖1顯示了典型高速數(shù)據(jù)轉(zhuǎn)換器系統(tǒng)的簡化框圖。該系統(tǒng)由帶通濾波器、ADC、高頻時(shí)鐘、高速存儲(chǔ)設(shè)備和后處理單元組成。除MAX104外,高頻時(shí)鐘在決定高速數(shù)據(jù)轉(zhuǎn)換器的精度方面起著重要作用。這種高頻、低相位噪聲時(shí)鐘是高頻壓控振蕩器(U1)、鎖相環(huán)(U2)和晶體振蕩器(U3)的組合,如圖2所示。

圖1.典型的高速數(shù)據(jù)轉(zhuǎn)換器系統(tǒng),采用MAX104 ADC和基于PLL的低抖動(dòng)時(shí)鐘。

圖2.高速、低相位噪聲時(shí)鐘是確保高速ADC最佳動(dòng)態(tài)性能的最關(guān)鍵元件之一。

MAX2620壓控振蕩器(VCO)能夠產(chǎn)生高達(dá)1GHz的振蕩器頻率,同時(shí)提供足夠的噪聲性能。由于固有的頻率漂移,通常需要鎖相環(huán)(PLL)通過將VCO輸出與晶體振蕩器頻率進(jìn)行比較,將VCO輸出鎖定到所需頻率。

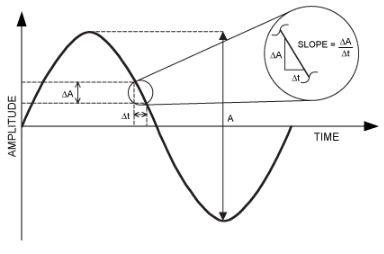

為高速數(shù)據(jù)轉(zhuǎn)換器系統(tǒng)選擇合適的VCO并不像找到具有正確振蕩器頻率的VCO那么簡單。必須考慮的一個(gè)關(guān)鍵參數(shù)是時(shí)鐘抖動(dòng)。抖動(dòng)通常定義為數(shù)字信號(hào)的重要時(shí)刻從其理想時(shí)間位置的短期、非累積變化。圖3顯示了包含抖動(dòng)的采樣時(shí)鐘信號(hào)。時(shí)鐘產(chǎn)生的抖動(dòng)是由各種內(nèi)部噪聲源引起的,例如熱噪聲、相位噪聲和雜散噪聲。對(duì)于數(shù)據(jù)轉(zhuǎn)換器,抖動(dòng)會(huì)影響數(shù)據(jù)轉(zhuǎn)換器的信噪比(SNR)性能。

圖3.時(shí)鐘信號(hào)抖動(dòng)會(huì)降低ADC信噪比。

時(shí)鐘抖動(dòng)如何降低ADC的信噪比(SNR)

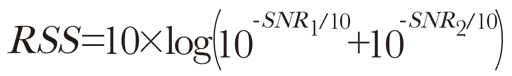

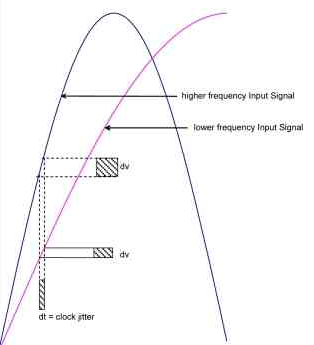

時(shí)鐘源產(chǎn)生的抖動(dòng)可能導(dǎo)致ADC的內(nèi)部電路錯(cuò)誤觸發(fā)采樣時(shí)間。如圖4所示,采樣時(shí)間Δt的不確定性等同于幅度ΔA的不確定性。這會(huì)導(dǎo)致模擬輸入幅度的錯(cuò)誤采樣,從而降低ADC的SNR。通過以下等式,可以計(jì)算出給定時(shí)鐘抖動(dòng)量的數(shù)據(jù)轉(zhuǎn)換器的最大SNR:

圖4.使用采樣時(shí)間不確定性獲得的信噪比模型。

當(dāng)項(xiàng) cos(ωt) = 1 時(shí),斜率達(dá)到最大值。因此,EQ.2可以重新排列為:根據(jù)定義,A/(ΔA)是信噪比,Δt是抖動(dòng)的均方根(RMS)值。等式3可以改寫為: 例如,如果模擬輸入信號(hào)為250MHz,并且要達(dá)到50dB SNR,則最大RMS抖動(dòng)(σ

例如,如果模擬輸入信號(hào)為250MHz,并且要達(dá)到50dB SNR,則最大RMS抖動(dòng)(σRMS)必須小于2ps。

噪聲源如何引起抖動(dòng)

熱噪聲、調(diào)頻 (FM)、幅度調(diào)制 (AM)、相位調(diào)制 (PM) 和雜散分量都會(huì)產(chǎn)生導(dǎo)致時(shí)鐘信號(hào)抖動(dòng)的噪聲。由于難以區(qū)分由FM、AM和PM引起的噪聲,因此所有三種類型的噪聲都?xì)w為一個(gè)通用術(shù)語,稱為相位噪聲。為了明確相位噪聲的計(jì)算,本文以使用MAX2620 VCO和PLL的高頻電路為例。

熱噪聲對(duì)抖動(dòng)的貢獻(xiàn)

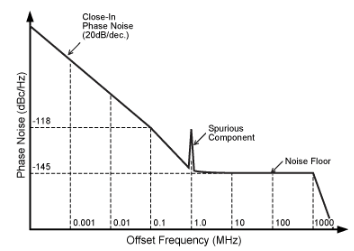

圖5顯示了VCO相位噪聲曲線的簡化圖。MAX2620的輸出放大器具有大約-147dBm/Hz的熱本底噪聲。這種噪聲是帶寬有限的白色高斯噪聲。雖然有效帶寬尚未表征,但可以近似為工作頻率的兩倍。將MAX2620正確調(diào)諧至所需輸出頻率后,本底噪聲對(duì)抖動(dòng)的貢獻(xiàn)可通過下式計(jì)算:

圖5.簡化MAX2620 VCO的相位噪聲曲線與失調(diào)頻率的關(guān)系

= 邊沿到邊抖動(dòng)方差(以 s2 為單位)

ωo = 2πfo = 角時(shí)鐘振蕩(中心)頻率(以 rad/s 為單位)

fo = 振蕩器(中心)頻率(赫茲)

f = 偏離中心頻率的頻率(以 Hz 為單位)

τ = 1/2fo = 周期的一半(以 s 為單位)

L(f) = 偏移頻率 f 時(shí)的相位噪聲(單位為 dBc/Hz)。

為了進(jìn)一步改善噪聲性能,通常在VCO輸出端應(yīng)用頻率響應(yīng)類似于帶通濾波器的功率匹配網(wǎng)絡(luò)(L2和C6)。這會(huì)衰減目標(biāo)帶寬之外的不需要的噪聲。通過這樣做,可以通過從0Hz偏移到f的積分極限來估計(jì)最差的噪聲0.超出這些限值的噪聲會(huì)大大衰減,可以忽略不計(jì)。因?yàn)楸镜自肼晫?duì)于 0Hz 到 f 的偏移頻率是均勻的0,L(f) 可以被認(rèn)為是常數(shù)。等式5可以簡化為:

本底噪聲引起的邊沿到邊序抖動(dòng)為:由于熱噪聲不相關(guān),因此抖動(dòng)不累積。周期間抖動(dòng)與邊沿到邊抖動(dòng)相同。

等式8也可以顯示為:

其中信噪比OSC是本底噪聲引起的振蕩器的信噪比。

相位噪聲對(duì)抖動(dòng)的貢獻(xiàn)

相位噪聲的特征是失調(diào)頻率下的噪聲功率與時(shí)鐘(載波)信號(hào)的功率電平之比。該比率通常歸一化為 1Hz 帶寬,從而產(chǎn)生 dBc/Hz 單位。例如,圖100中5kHz失調(diào)時(shí)的相位噪聲為-118dBc。這意味著1000.1MHz的噪聲功率比118Hz帶寬中1000MHz的載波功率水平低1dB。

MAX2620的自由運(yùn)行相位噪聲從20MHz轉(zhuǎn)折失調(diào)頻率到時(shí)鐘頻率約為1dB/十倍頻程。使用EQ. 11時(shí),相位噪聲引起的周期間抖動(dòng)可以計(jì)算如下:

其中f是時(shí)鐘頻率的失調(diào)頻率,它必須位于相位噪聲每十倍頻程降低20dB的區(qū)域。相位噪聲L(f)取自MAX2620在f = 100kHz失調(diào)頻率下的特性。當(dāng)f = 10kHz時(shí),產(chǎn)生的抖動(dòng)不會(huì)改變。

雜散元件對(duì)抖動(dòng)的貢獻(xiàn)

基于 PLL 的時(shí)鐘信號(hào)會(huì)產(chǎn)生雜散。如果不抑制這些雜散,它們可能會(huì)降低抖動(dòng)性能。圖6顯示了使用頻譜分析儀采集的1GHz時(shí)鐘信號(hào)的頻譜圖。圖中所示的兩對(duì)對(duì)稱雜散分別比載波低約75dBc和85dBc。這些雜散與載波以及彼此之間的分離由鎖相環(huán)中使用的比較頻率決定。在這種情況下,比較頻率為1MHz;因此,載波旁邊的兩個(gè)雜散距離載波和后續(xù)對(duì)正好1MHz。此外,還有另一對(duì)由晶體振蕩器引起的75MHz偏移的-20dBc雜散(未顯示)。以下等式將這些雜散轉(zhuǎn)換為抖動(dòng):

圖6.顯示帶有雜散元件的1GHz時(shí)鐘。

其中 fm是相位噪聲雜散分量出現(xiàn)的失調(diào)頻率。m = 1 時(shí),周期間抖動(dòng)計(jì)算為 4.38x10-6對(duì)于使用ADC的實(shí)際應(yīng)用,例如MAX104,該電平的雜散噪聲引起的抖動(dòng)可以忽略不計(jì)。

總抖動(dòng)

總周期間抖動(dòng)是抖動(dòng)平方和的平方根的函數(shù),可以按如下方式計(jì)算:

鎖相環(huán)

由于溫度、電源、負(fù)載等原因引起的頻率漂移,自由運(yùn)行的VCO很少單獨(dú)使用。通常引入鎖相環(huán)以幫助將VCO輸出鎖定到所需頻率。如果設(shè)計(jì)得當(dāng),鎖相環(huán)有助于降低相位噪聲。環(huán)路帶寬內(nèi)的相位噪聲低于自由運(yùn)行的VCO的相位噪聲。因此,相位噪聲引起的實(shí)際抖動(dòng)小于EQ.11。

圖7顯示了MB15E07在整數(shù)N分頻PLL系統(tǒng)中的功能圖。它由一個(gè)鑒相器(或比較器)、一個(gè)輸出電荷泵、一個(gè)雙模量預(yù)標(biāo)量、一個(gè)N計(jì)數(shù)器和一個(gè)R計(jì)數(shù)器組成。N 計(jì)數(shù)器由一個(gè)主 (M) 計(jì)數(shù)器和一個(gè)燕子或輔助 (A) 計(jì)數(shù)器組成。

然后,N 計(jì)數(shù)器與雙模預(yù)標(biāo)量 (P) 配合使用。

圖7.典型PLL系統(tǒng)的簡化框圖,由PLL、晶體振蕩器、環(huán)路濾波器和VCO組成。

在上電期間(假設(shè)PLL已預(yù)編程),VCO將以所需頻率加上一些偏移振蕩。該頻率首先除以整數(shù)N,然后與參考晶體振蕩器頻率進(jìn)行比較,其頻率也除以整數(shù)R。如果兩個(gè)頻率之間存在相位差,則PLL輸出端的電壓會(huì)相應(yīng)變化。例如,如果VCO頻率低于基準(zhǔn)頻率,則電荷泵將對(duì)環(huán)路濾波電容充電以增加電壓。如果VCO頻率高于基準(zhǔn),電荷泵將對(duì)環(huán)路濾波電容放電以降低電壓。電壓的增加導(dǎo)致頻率的增加,反之亦然。因此,PLL用作反饋環(huán)路,將VCO輸出頻率鎖定在所需頻率。VCO 頻率是 N、R 和 f 的函數(shù)裁判計(jì)算方法如下:

例如,如果 P = 32、M = 31 和 A = 8,則使用 EQ. 14,N 計(jì)數(shù)器計(jì)算為 1000。如果參考振蕩器頻率為20MHz,R計(jì)數(shù)器設(shè)置為20,則使用EQ.15,則VCO頻率鎖定在1000MHz。

設(shè)計(jì)參數(shù)

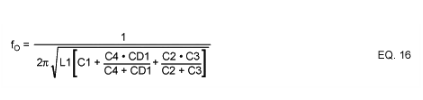

需要仔細(xì)設(shè)計(jì)和實(shí)現(xiàn)時(shí)鐘電路,以確保最佳性能。這可以通過選擇合適的組件和提供精心設(shè)計(jì)的高頻 PC 板來實(shí)現(xiàn)。表1顯示了兩種不同工作頻率的推薦元件值。這些值可確保VCO以所需頻率振蕩和鎖相,同時(shí)提供適當(dāng)?shù)妮敵龉β孰娖健AX2620的輸出頻率由外部諧振電路設(shè)置,諧振電路由L1、C1、C2、C3、C4和D1組成。L1、C1、C2、C3 和 C4 設(shè)置自由運(yùn)行的振蕩頻率。變?nèi)?a target="_blank">二極管D1將輸出頻率微調(diào)至所需頻率。D1 采用反向偏置,電容隨 PLL 輸出產(chǎn)生的偏置電壓而變化。D1電容的變化允許對(duì)輸出頻率進(jìn)行微調(diào)。

振蕩頻率可以用以下公式計(jì)算:

為了適應(yīng)元件容差、PCB、電源電壓和溫度變化,應(yīng)選擇D1的電容,使調(diào)諧范圍約為標(biāo)稱頻率的±5%至±10%。C4是將變?nèi)荻O管耦合到調(diào)諧池的電容器。增加 C4 可以增加調(diào)諧范圍。C2 和 C3 是振蕩器正常工作所必需的反饋電容。通常,C2 = 2.7pF和C3 = 1.0pF。對(duì)于 1.0GHz,選擇 L1 = 5.6nH、C4 = 4.7pF 和 C1 = 1.0pF。 VCO輸出和ADC時(shí)鐘輸入必須匹配至50Ω。VCO輸出端使用LC網(wǎng)絡(luò)(L2和C6),以確保向ADC時(shí)鐘輸入端提供最佳功率傳輸。匹配網(wǎng)絡(luò)具有類似帶通濾波器的頻率響應(yīng),可進(jìn)一步降低本底熱噪聲。

表 1.時(shí)鐘發(fā)生器的建議組件值

| 指定 | 描述 | ||||

| f外= 600兆赫 | f外= 1000兆赫 | ||||

| R1 | 240Ω | 390Ω | |||

| R2 | 240Ω | 390Ω | |||

| C1 | 1.0pF | 1.0pF | |||

| C2 | 2.7pF | 2.7pF | |||

| C3 | 1.0pF | 1.0pF | |||

| C4 | 9.0pF | 3.3pF | |||

| C5 | 9.0pF | 2.2pF | |||

| C6 | 3.0pF | 1.5pF | |||

| C7 | 12nF | 3.9pF | |||

| C8 | 120nF | 39nF | |||

| C9 | 12nF | 3.9nF | |||

| L1 | 12nH (±2%) | 5.6nH (±2%) | |||

| L2 | 18nH | 10nH | |||

| D1 | SMV1233-001 (Alpha Industries) | SMV1233-001 (Alpha Industries) | |||

PLL脈沖的電荷泵輸出,相位比較頻率由R和外部晶體振蕩器確定。采用環(huán)路濾波器將這些脈沖濾波為VCO的恒定直流控制電壓。三階環(huán)路濾波器(圖2)由C7、C8、C9、R1和R2組成。使用簡化的公式 17 到 23 計(jì)算組件值。 N = 等式的計(jì)數(shù)器值 14

N = 等式 14 中的計(jì)數(shù)器值

ξ = 阻尼系數(shù),通常為 0.707

ICP= 電荷泵電流,MB15E07為10mA

KVCO= VCO調(diào)諧增益或靈敏度

VCO 調(diào)諧增益,KVCO,取決于 VCO 油箱中使用的元件值。本設(shè)計(jì)示例中的VCO調(diào)諧增益約為35MHz/V。

MB15E07通過SPI?兼容接口進(jìn)行編程。表2給出了600MHz (MAX106)和1000MHz (MAX104)工作的寄存器/計(jì)數(shù)器設(shè)置:

表 2.建議注冊(cè) 帶15MHz晶體振蕩器的MB07E20的設(shè)置

| 600MHz | 1000MHz | ||||

| fCOMPARISON | 500kHz | 1000kHz | |||

| Loop Bandwidth | 25kHz | 50kHz | |||

| R Counter | 40 | 20 | |||

| P Counter | 32 | 32 | |||

| M Counter | 37 | 31 | |||

| A Counter | 16 | 8 | |||

| SW bit | HIGH | HIGH | |||

| FC bit | HIGH | HIGH | |||

為確保良好的高頻 PC 板布局,請(qǐng)記住以下建議:

保持所有印刷電路板走線長度盡可能短。采用受控阻抗走線設(shè)計(jì)。

盡可能選擇最小的元件尺寸,最好是0603或0402型。

使用高質(zhì)量因數(shù) (Q) 元件將 VCO 相位噪聲降至最低,并最大限度地提高輸出功率傳輸。Q 因子為 40 或更高就足夠了。

諧振電路的所有元件盡可能靠近MAX2620。

將去耦電容放置在VCO附近,并直接連接到接地層。全部 V抄送連接應(yīng)有自己的去耦電容。

在VCO輸出和ADC時(shí)鐘輸入之間保持50Ω連接。

使用表 1 中的組件值建議作為起點(diǎn)。可能的寄生效應(yīng)可能需要對(duì)某些組件值進(jìn)行微調(diào),以確保最佳性能。

實(shí)驗(yàn)結(jié)果

為了演示所建議的時(shí)鐘電路的性能,根據(jù)建議的公式和技術(shù)設(shè)計(jì),圖2中的電路使用MAX104評(píng)估板進(jìn)行設(shè)計(jì)和測試。圖6顯示了使用頻譜分析儀測量的擬議高頻、低抖動(dòng)時(shí)鐘的輸出。振蕩頻率鎖相在1GHz,輸出電平為-2dBm。圖8所示為MAX104 ADC在模擬輸入頻率范圍內(nèi)的信噪比。用 f樣本= 1.0GHz 和 f在在-1dBFS下,對(duì)于47MHz至1GHz的模擬頻率,SNR分別為45.5dB至10.1dB。與已知的低抖動(dòng)信號(hào)發(fā)生器(HP8662A)相比,使用建議的時(shí)鐘測得的SNR僅低~0.4dB。

圖8.采用PLL時(shí)鐘時(shí)MAX104的SNR比采用HP0A時(shí)低約4.8662dB。

審核編輯:郭婷

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8724瀏覽量

147414 -

pll

+關(guān)注

關(guān)注

6文章

777瀏覽量

135203 -

數(shù)據(jù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

1文章

365瀏覽量

28030

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

時(shí)鐘發(fā)生器性能對(duì)數(shù)據(jù)轉(zhuǎn)換器的影響

時(shí)鐘發(fā)生器的相位噪聲和抖動(dòng)性能為什么會(huì)影響到數(shù)據(jù)轉(zhuǎn)換器?

時(shí)鐘抖動(dòng)會(huì)對(duì)高速ADC的性能有什么影響?

一個(gè)低抖動(dòng)時(shí)鐘源的參考設(shè)計(jì),不看肯定后悔

為高速A/D轉(zhuǎn)換器設(shè)計(jì)時(shí)鐘

用于高速AD的低抖動(dòng)時(shí)鐘穩(wěn)定電路

高速ADC的低抖動(dòng)時(shí)鐘設(shè)計(jì)

轉(zhuǎn)換器時(shí)鐘技術(shù)向高速數(shù)據(jù)時(shí)鐘發(fā)展

高速ADC時(shí)鐘抖動(dòng)的影響的了解

基于改進(jìn)延遲鎖相環(huán)的高速低抖動(dòng)時(shí)鐘電路的開發(fā)與設(shè)計(jì)

數(shù)據(jù)轉(zhuǎn)換器中時(shí)鐘發(fā)生器件對(duì)系統(tǒng)性能的影響

模數(shù)轉(zhuǎn)換器的性能及時(shí)鐘抖動(dòng)對(duì)其造成的影響分析

高速模數(shù)轉(zhuǎn)換器的性能分析及時(shí)鐘抖動(dòng)會(huì)對(duì)其造成什么影響

AN-1221: 使用ADF4002 PLL產(chǎn)生高速模數(shù)轉(zhuǎn)換器所需的極低抖動(dòng)編碼(采樣)時(shí)鐘

超低抖動(dòng)時(shí)鐘發(fā)生器和分配器最大限度地提高數(shù)據(jù)轉(zhuǎn)換器的信噪比

為高速數(shù)據(jù)轉(zhuǎn)換器設(shè)計(jì)低抖動(dòng)時(shí)鐘

為高速數(shù)據(jù)轉(zhuǎn)換器設(shè)計(jì)低抖動(dòng)時(shí)鐘

評(píng)論