作者:一博科技高速先生成員 孫小兵

端接就是人為加入電阻來改善信號由于鏈路阻抗突變帶來的反射問題的一種方式,并且引入成本也較低,在很多場合都有運用。但是端接電阻擺放位置一直困惑大家,或許大家只知道串聯(lián)電阻需要靠近發(fā)送端擺放,并聯(lián)電阻需要靠近接收端擺放,但不知道怎么衡量能夠接受的距離是多少。在實際單板設(shè)計中由于芯片周邊空間有限,往往可能需要從BGA中引出較長的一段走線再接上端接電阻,而這段較長走線可能會影響端接效果。下面我們就分別探討串聯(lián)電阻和并聯(lián)電阻到芯片端走線距離對端接效果的影響。

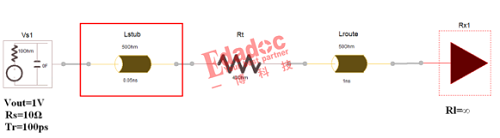

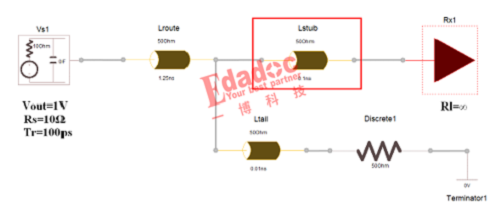

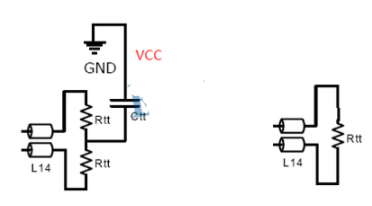

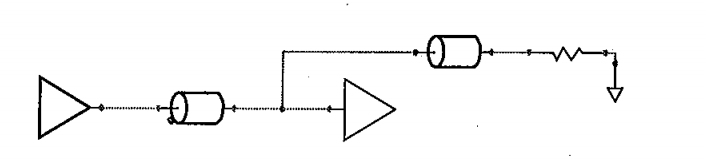

實際運用場合中串阻鏈路模型如圖所示。串阻和驅(qū)動器之間存在一段較長的走線,這段樁線的長度會直接影響端接效果。如果串阻距離發(fā)送器較遠,樁線較長,串阻就可能沒有端接效果。下面我們探究一下這段樁線的長度Lstub對端接效果的影響。

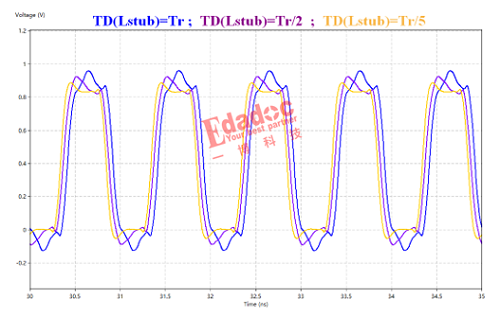

下圖是串阻前面樁線長度延時TD0分別為1Tr、Tr/2、Tr/5時在末端接收信號的反射振幅情況。當樁線延時達到上升時間的一半時,信號反射振幅會達到最大,樁線越短,反射振幅就越小。

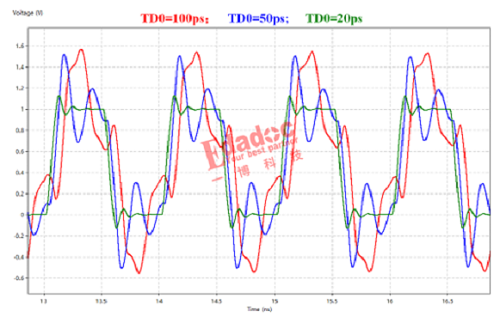

上面是當信號上升時間一定,前面樁線長度變化時對串聯(lián)端接效果的影響。那么當樁線長度一定時,改變信號上升時間對端接效果有沒有影響呢?下面我們又來探究信號上升時間Tr分別是樁線時延TD0、3*TD0、5*TD0時末端接收信號的反射振幅情況。反射幅度隨著信號上升時間的增加而逐漸減小。

根據(jù)以上結(jié)果分析可知,信號上升時間和串阻到芯片走線距離的關(guān)系會影響串聯(lián)端接效果。在設(shè)計中建議樁線的延時應(yīng)該不超過六分之一的信號上升時間,即TDstub≤Tr/6,這樣接收端的噪聲基本能夠控制在10%以內(nèi)。例如信號上升時間為300ps,樁線的延時應(yīng)當要小于50ps,即樁線的長度不超過300mil基本不會出現(xiàn)問題。

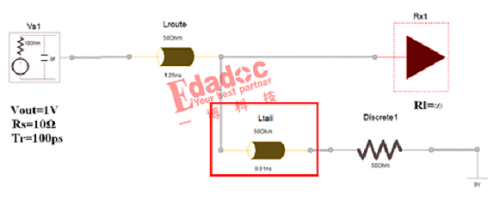

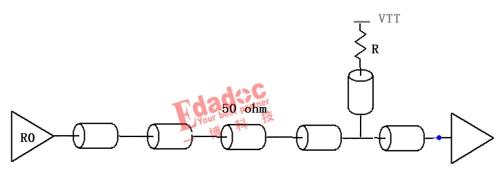

接下來我們探討并聯(lián)端接鏈路中電阻到末端距離對信號的影響。在理想情況下電阻最好放在接收器之后,仿真鏈路模型如下。傳輸線先連接到接收端,然后再引一段“尾巴”走線到端接電阻,端接電阻尾線阻抗與并聯(lián)電阻值保持一致。這樣信號先到接收端,然后再到端接電阻。這種狀態(tài)下端接電阻的尾線長度Ltail對信號質(zhì)量影響非常小。下面也驗證了端接尾線傳輸延時分別是Tr和Tr/10兩種情況下接收端的信號波形狀態(tài)。

可以看到兩個信號波形幾乎完全重合,信號質(zhì)量非常良好。由此分析可知,端接電阻尾線長度對端接效果幾乎沒有影響。

在實際項目設(shè)計中,端接不可能完全都從信號接收端接出來,總會在端接電阻分支點和接收端之間存在一段長度的走線,如下圖鏈路模型。這段樁線的長度Lstub會影響信號接收質(zhì)量,若樁線過長將削弱端接效果。

下圖顯示的是接收端前面樁線長度分別為Tr、Tr/2、Tr/5情況下接收端信號波形狀態(tài)。可以看出當樁線長度越短,端接效果就越好。建議端接電阻前面樁線延時小于Tr/6。

當采用端接來改善信號反射時,串聯(lián)阻應(yīng)盡可能靠近發(fā)送端放置,建議芯片輸出到串阻的走線延時小于六分之一的信號上升時間;并聯(lián)電阻應(yīng)盡可能靠近接收端放置,端接電阻支路尾線長度對端接效果影響較小,建議端接電阻分支點到接收端的走線延時小于六分之一的信號上升時間。這或許也是為什么到DDR5后地址線的末端端接也改成了ODT的形式。

審核編輯:湯梓紅

-

電阻

+關(guān)注

關(guān)注

86文章

5525瀏覽量

172264 -

驅(qū)動器

+關(guān)注

關(guān)注

53文章

8256瀏覽量

146582 -

DDR5

+關(guān)注

關(guān)注

1文章

426瀏覽量

24159 -

PCB

+關(guān)注

關(guān)注

1文章

1813瀏覽量

13204

發(fā)布評論請先 登錄

相關(guān)推薦

DDR終端匹配電阻的長度多少合適?

探究電阻的串聯(lián)、并聯(lián)和混聯(lián)

關(guān)于上下拉電阻的探究

高速電路中電阻端接的作用

不加端接電阻的快樂,你們絕對想象不到!

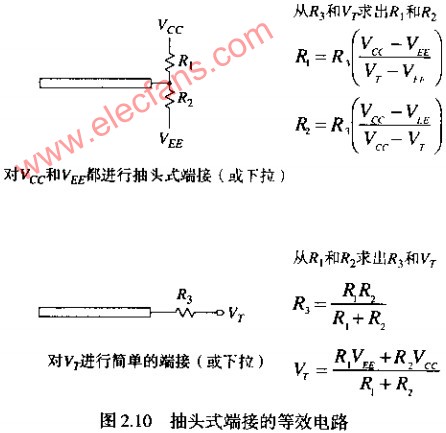

抽頭式下拉端接

時鐘信號抖動怎么辦?串行端接、下拉電阻、電阻橋、LVPECL來幫忙

探究電阻布局對端接效果的影響

探究電阻布局對端接效果的影響

評論