4.1 8253簡介

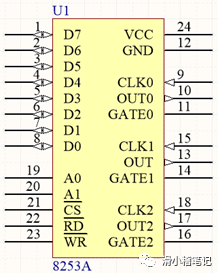

4.1.1 引腳詳解

(1)三態(tài)雙向數(shù)據(jù)口D0~D7:用于8253A與CPU的并行通信;

(2)計(jì)數(shù)脈沖輸入CLK0~CLK2:用于提供8253的計(jì)數(shù)脈沖;

(3)通道門控GATE0~GATE2:控制對應(yīng)通道的輸出;

(4)讀控制信號RD:低電平有效;

(5)寫控制信號WR:低電平有效;

(6)片選信號CS:低電平有效;

(7)地址選擇端A0,A1:用于選擇芯片內(nèi)部的寄存器。

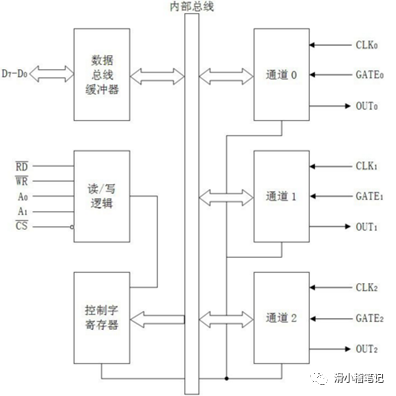

4.1.2 內(nèi)部結(jié)構(gòu)框圖

4.1.3 工作模式

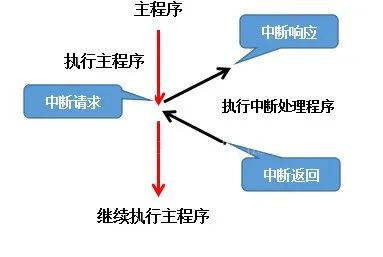

(1)工作模式0—計(jì)數(shù)結(jié)束產(chǎn)生中斷

在計(jì)數(shù)值減到0時(shí)輸出信號OUT將產(chǎn)生一個上升沿,這個上升沿作為CPU的中斷請求信號,當(dāng)CPU執(zhí)行完中斷處理程序時(shí),如果希望再一次啟動計(jì)數(shù)器結(jié)束中斷功能,可以再次將計(jì)數(shù)值送給它。

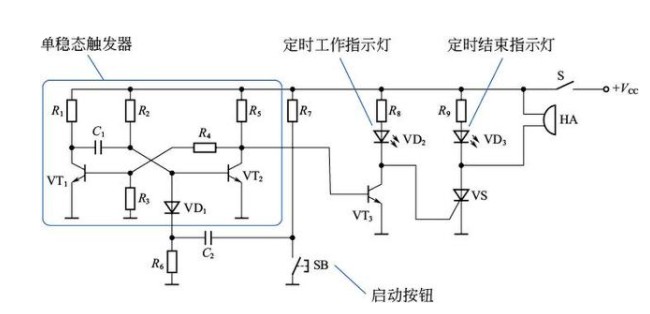

(2)工作模式1—可編程單穩(wěn)態(tài)輸出方式

計(jì)數(shù)初值寫入到8253A后必須等待GATE信號的觸發(fā)才能開始計(jì)數(shù),觸發(fā)后使輸出信號OUT變低,計(jì)數(shù)到0時(shí),OUT信號又回到高電平,這類似于數(shù)字電路中的單穩(wěn)態(tài)電路,而低電平的寬度由計(jì)數(shù)脈沖的個數(shù)決定,所以這種工作方式又稱為可編程單穩(wěn)態(tài)輸出方式。

(3)工作模式2—頻率發(fā)生器/分頻器

該模式在計(jì)數(shù)器減到0的時(shí)候會重新自動地把原來的初值寄存器中的數(shù)據(jù)裝載到減一計(jì)數(shù)器中重復(fù)計(jì)數(shù),第一次運(yùn)行時(shí)有一個額外的下裝脈沖,而后續(xù)的重復(fù)計(jì)數(shù)沒有這個額外脈沖,它的下裝脈沖直接用上一次計(jì)數(shù)的最后一個脈沖,所以,當(dāng)計(jì)數(shù)值設(shè)為N時(shí),第一次要N+1個脈沖,后面重復(fù)計(jì)數(shù)的值皆為N。

(4)工作模式3—方波發(fā)生器

模式3與模式2基本相似,不同之處在于計(jì)數(shù)值如果為偶數(shù),OUT輸出的高電平寬度與低電平寬度相等,稱為方波發(fā)生器,如果計(jì)數(shù)值為奇數(shù),高電平比低電平多一個CLK的脈沖寬度。

(5)工作模式4—軟件觸發(fā)的選通信號發(fā)生器

模式4除OUT的波形與模式0不同,計(jì)數(shù)過程中GATE和計(jì)數(shù)初值發(fā)生變化對OUT的影響與模式0一樣。

(6)工作模式5

模式5除了OUT的波形與模式1不同之外,計(jì)數(shù)過程中GATE和計(jì)數(shù)初值發(fā)生變化對OUT的影響與模式1一樣

4.1.4 控制字格式

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| SC1 | SC0 | RW1 | RW0 | M2 | M1 | M0 | BCD |

控制字的具體描述如下表所示:

| 計(jì)數(shù)器選擇 |

|---|

| SC1 |

| 0 |

| 0 |

| 1 |

| 1 |

| 計(jì)數(shù)器操作方式控制 |

|---|

| RW1 |

| 0 |

| 0 |

| 1 |

| 1 |

| 計(jì)數(shù)器工作模式選擇 |

|---|

| M2 |

| 0 |

| 0 |

| 0 |

| 0 |

| 1 |

| 1 |

| 1 |

| 1 |

D0:二進(jìn)制與BCD碼選擇

0:二進(jìn)制形式

1:BCD碼形式

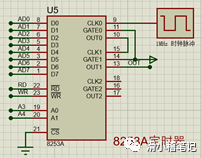

4.1.5 端口地址計(jì)算

8253通過引腳CS、RD、WR、A0和A1五個端口的電平?jīng)Q定芯片內(nèi)部的寄存器,地址對應(yīng)如下表所示。

| CS | RD | WR | A1 | A0 | 功能 |

|---|---|---|---|---|---|

| 0 | 1 | 0 | 0 | 0 | 設(shè)置計(jì)數(shù)器0的初值 |

| 0 | 1 | 0 | 0 | 1 | 設(shè)置計(jì)數(shù)器1的初值 |

| 0 | 1 | 0 | 1 | 0 | 設(shè)置計(jì)數(shù)器2的初值 |

| 0 | 1 | 0 | 1 | 1 | 設(shè)置控制字或命令 |

| 0 | 0 | 1 | 0 | 0 | 讀取計(jì)數(shù)器0的計(jì)數(shù)值 |

| 0 | 0 | 1 | 0 | 1 | 讀取計(jì)數(shù)器1的計(jì)數(shù)值 |

| 0 | 0 | 1 | 1 | 0 | 讀取計(jì)數(shù)器2的計(jì)數(shù)值 |

4.2 8253初始化流程

(1)將控制字寫入8253A

(2)對8253A中的某個計(jì)數(shù)器寫入初值

(3)啟動計(jì)數(shù)器

注意:由于8253A是一個16位的計(jì)數(shù)器,所以當(dāng)計(jì)數(shù)的時(shí)間超出計(jì)數(shù)器的范圍時(shí)可以考慮用兩個計(jì)數(shù)器級聯(lián)達(dá)到目的。

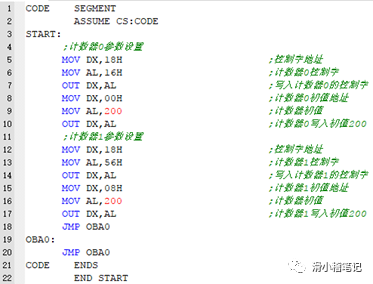

4.3 源代碼

例題:利用8253A芯片產(chǎn)生一個500ms,占空比50%的方波。

解析過程:由于硬件電路設(shè)計(jì)時(shí)利用1MHz作為計(jì)數(shù)器的時(shí)鐘脈沖,所以計(jì)數(shù)器的一個脈沖的時(shí)間應(yīng)該是1us,由于需要產(chǎn)生一個20ms的高電平,所以需要計(jì)數(shù)20000次才可以,但是由于8位的計(jì)數(shù)器數(shù)據(jù)范圍是255,所以采用兩個計(jì)數(shù)器級聯(lián)的方式達(dá)到目的,將兩個計(jì)數(shù)器均設(shè)置為模式3(即方波發(fā)生器),另外,根據(jù)硬件連接,A0連接在地址端的A3,A1連接在地址端的A4,片選CS接地,所以,對應(yīng)計(jì)數(shù)器0的初值設(shè)置地址應(yīng)該是0000 H,計(jì)數(shù)器1的初值設(shè)置地址應(yīng)該是0008 H,控制字的地址為0018 H。經(jīng)過上述分析,源代碼如下圖所示。

注:由于設(shè)定的計(jì)數(shù)器工作在模式3,所以計(jì)數(shù)脈沖會自動在中間產(chǎn)生脈沖

-

信號

+關(guān)注

關(guān)注

11文章

2823瀏覽量

77536 -

Out

+關(guān)注

關(guān)注

0文章

31瀏覽量

13253 -

單穩(wěn)態(tài)電路

+關(guān)注

關(guān)注

0文章

16瀏覽量

15378

發(fā)布評論請先 登錄

相關(guān)推薦

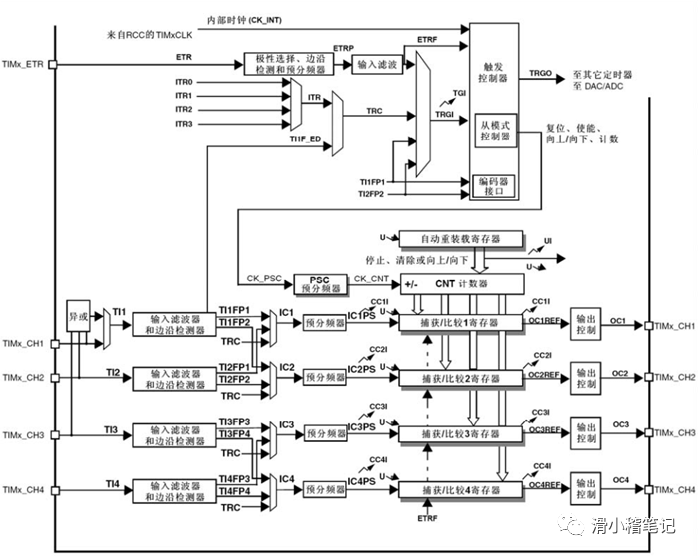

STM32定時(shí)器(二)定時(shí)器中斷

555定時(shí)器

定時(shí)器電路圖工作原理(聲光提示定時(shí)器電路/555定時(shí)器電路/相片曝光定時(shí)器電路)

STM32定時(shí)器-基本定時(shí)器

基于硬件定時(shí)器的軟件定時(shí)器

STM32——高級定時(shí)器、通用定時(shí)器、基本定時(shí)器的區(qū)別

STM32-通用定時(shí)器-定時(shí)器中斷

STM32定時(shí)器學(xué)習(xí)---基本定時(shí)器

SysTick 定時(shí)器

31章-定時(shí)器

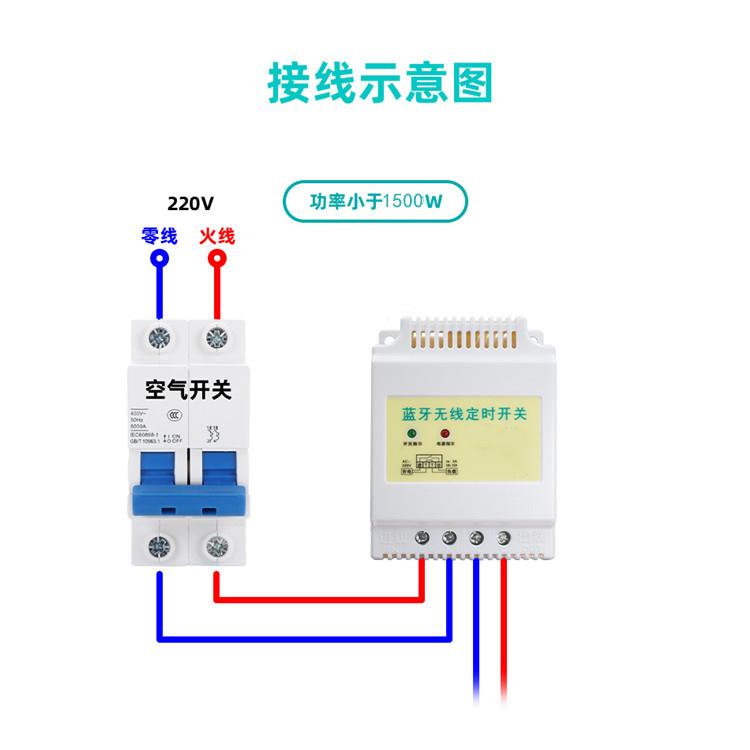

定時(shí)器開關(guān)怎么接線?

基礎(chǔ)定時(shí)器實(shí)驗(yàn)

什么是軟件定時(shí)器?軟件定時(shí)器的實(shí)現(xiàn)原理

定時(shí)器中斷是什么意思,定時(shí)器中斷的工作原理

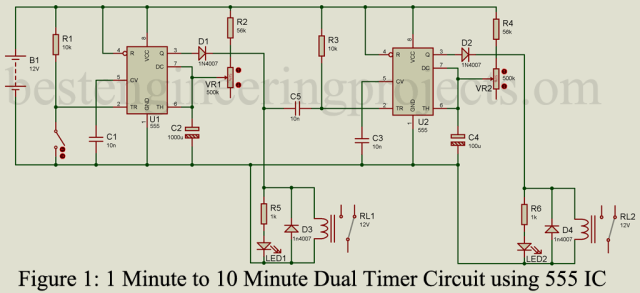

使用555定時(shí)器的可調(diào)雙定時(shí)器電路

評論