回顧:

今天看了這篇論文,感覺還挺有吸引力,就做了如下的筆記:

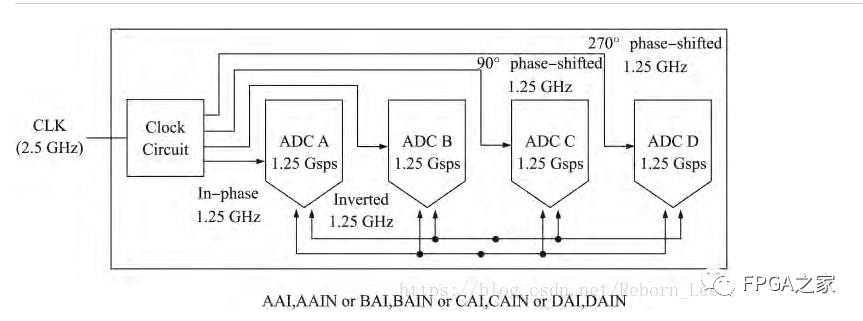

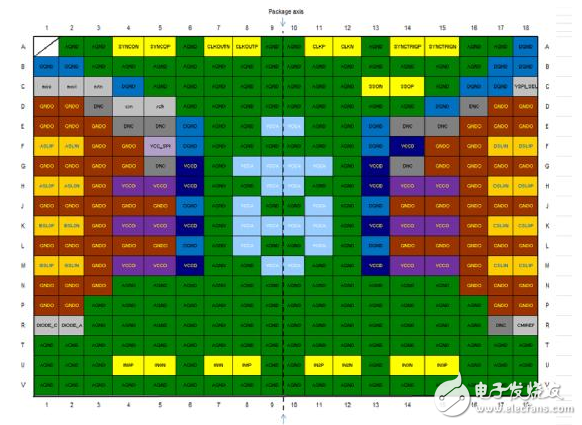

如下圖,首先以單通道工作方式為例,回顧一下這款ADC芯片的工作模式:

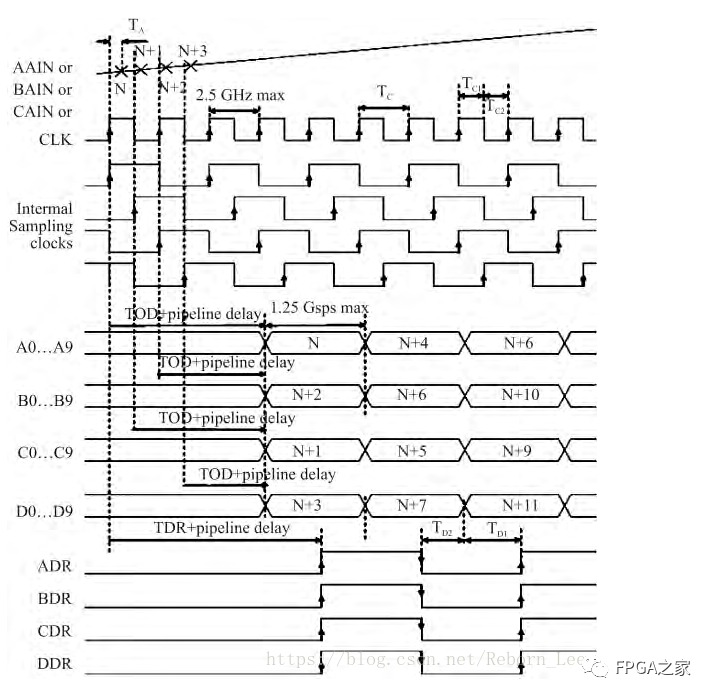

外部給該ADC芯片提供一個(gè)時(shí)鐘CLK,頻率為2.5GHz,通過內(nèi)部時(shí)鐘電路,2分頻之后的時(shí)鐘送到核A(ADC A),相位翻轉(zhuǎn)180°的二分頻時(shí)鐘送到核B(ADC B),相位偏移90°的二分頻時(shí)鐘送到核C(ADC C),相位偏移270°的二分頻時(shí)鐘送到核D(ADC D)。四個(gè)ADC核(A、B、C、D)同時(shí)工作(同時(shí)采樣),工作頻率相當(dāng)于5GHz。

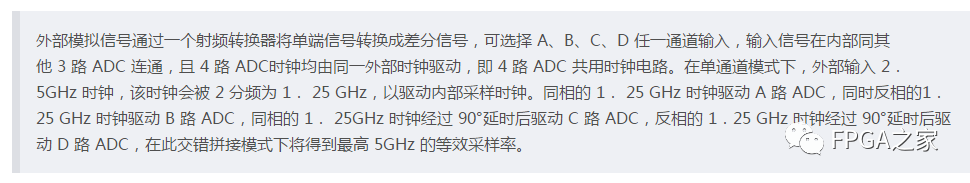

也可以根據(jù)論文上的描述:

從上面的分析大概也能明白了采樣時(shí)鐘的波形是什么樣子的:

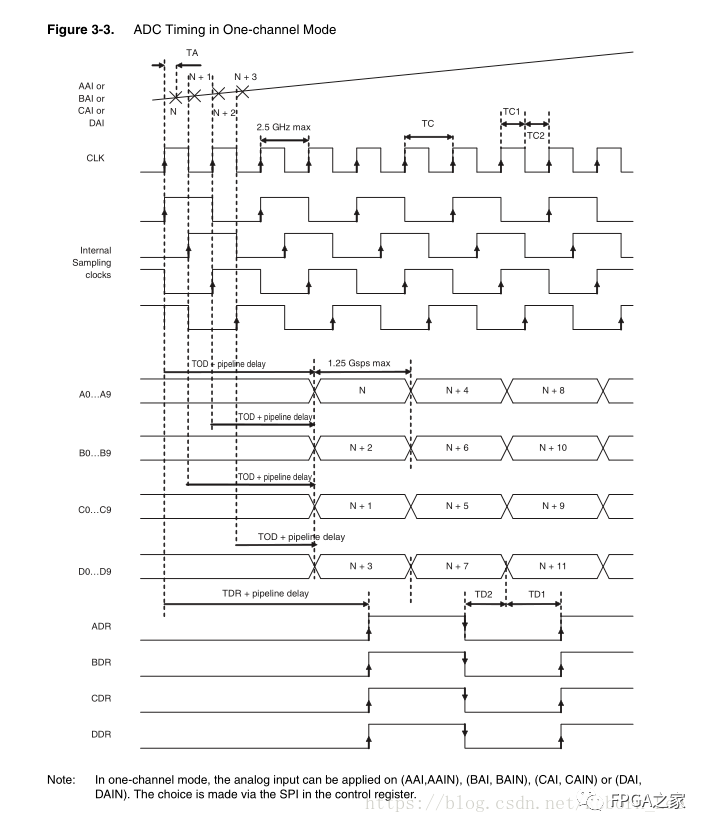

描述一下采樣順序就是ADC A采樣的數(shù)據(jù)為第1個(gè),然后ADC C 采樣的數(shù)據(jù)為第2個(gè), ADC B采樣的數(shù)據(jù)為第3個(gè), ADC D采樣的數(shù)據(jù)為第4個(gè),依次循環(huán)。

正如數(shù)據(jù)手冊(cè)的描述:

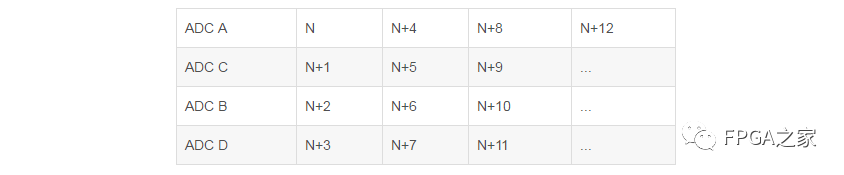

為了簡(jiǎn)化定時(shí)器的目的,關(guān)于采樣的端口的時(shí)間順序是A C B D,因此輸出端口的采樣順序如下:

A: N, N + 4, N + 8, N + 12…

C: N + 1, N + 5, N + 9…

B: N + 2, N + 6, N + 10…

D: N + 3, N + 7, N + 11…

畫個(gè)表格更直觀些:

回顧就到這里吧。

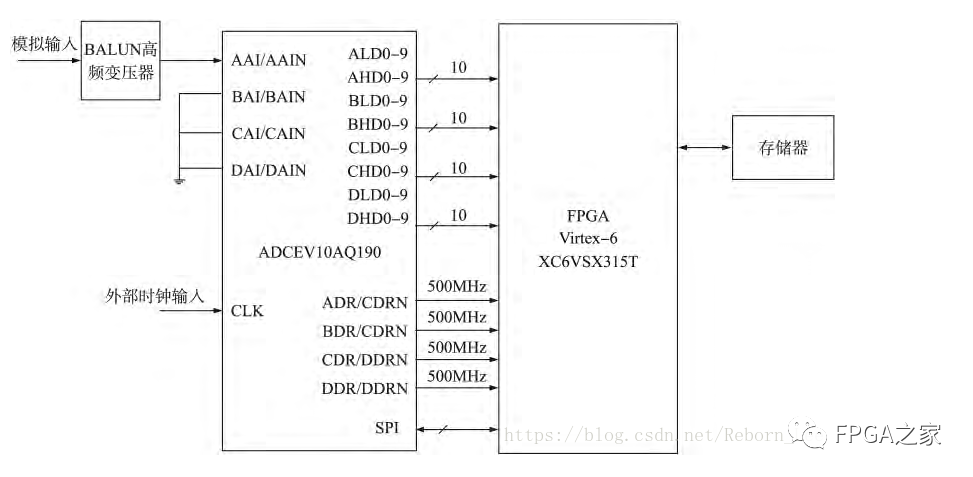

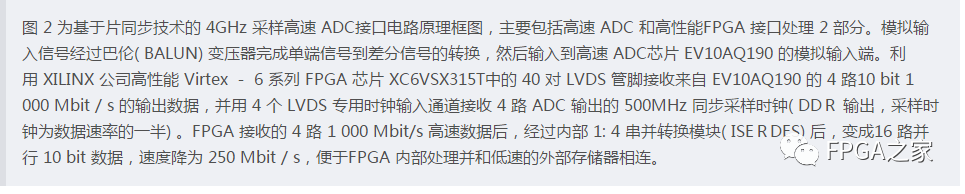

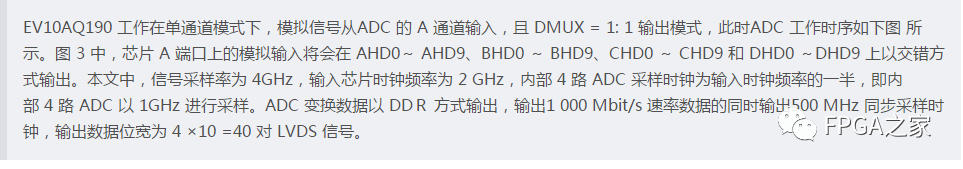

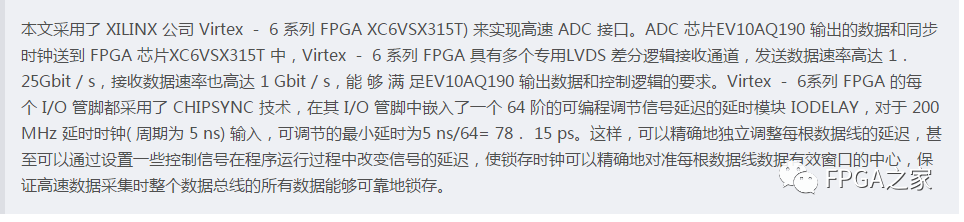

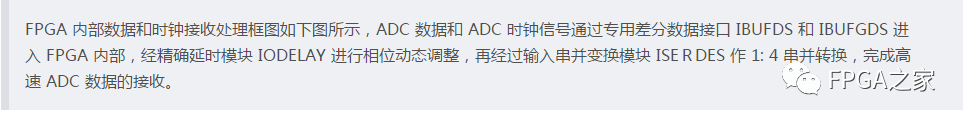

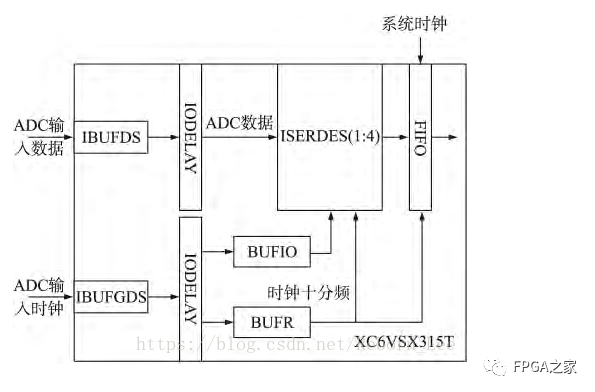

基于片同步技術(shù)的高速 ADC 接口

片同步( CHIPSYNC) 是 XILINX 公司命名的一種同步技術(shù),其本質(zhì)是一種源同步技術(shù),目的是為FPGA 提供一個(gè)高速的源同步數(shù)據(jù)總線接口。它是XILINX 公司在 Virtex - 4 及之后系列 FPGA 上采用的一種技術(shù),XILINX FPGA 內(nèi)部具有若干全局時(shí)鐘緩沖器( BUFG) 和區(qū)域時(shí)鐘緩沖器( BUFR) ,特別適合做源同步接口。FPGA 片內(nèi)每個(gè) I/O 管腳中集成了一個(gè) 64 階的可編程調(diào)節(jié)信號(hào)延遲的延時(shí)模塊( IODELAY) ,可精確控制信號(hào)延時(shí)實(shí)現(xiàn)采樣時(shí)鐘和數(shù)據(jù)相位的動(dòng)態(tài)調(diào)整,從而確定信號(hào)采集的最佳采樣點(diǎn),實(shí)現(xiàn)高速 ADC 接口的可靠、穩(wěn)定工作。

上面說的4GHz的意思是ADC等效的采樣速率,這也就意味著外部輸入時(shí)鐘的頻率為2GHz,如此數(shù)據(jù)同步時(shí)鐘是外部時(shí)鐘的1/4,也就是500MHz。等效采樣速率為4GHz,那么每一個(gè)通道的采樣速率就是1GHz,也就是1000MHz,那么EV10AQ190的每一路輸出數(shù)據(jù)速率為1000Mbit/s,且由于該ADC芯片的采樣分辨率為10bit,也就是每個(gè)采樣點(diǎn)數(shù)據(jù)為10bit。

4路1000Mbit/s的輸出數(shù)據(jù)經(jīng)過FPGA的接收后,經(jīng)過FPGA內(nèi)部1:4串并轉(zhuǎn)換后,每一路串行數(shù)據(jù)變成4路并行數(shù)據(jù),那么4路數(shù)據(jù)串行數(shù)據(jù)變成16路并行數(shù)據(jù),此時(shí)并行數(shù)據(jù)的速率為串行的1/4,也就是250Mbit/s,這樣速率就降低了,便于FPGA內(nèi)部處理并和低速的外部存儲(chǔ)器相連。

高速ADC

ADC與FPGA數(shù)據(jù)接口

至于接下來的仿真等,我還實(shí)現(xiàn)不了。就記到這里吧,以后積累了經(jīng)驗(yàn)在回頭看。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

456文章

50967瀏覽量

424874 -

接口

+關(guān)注

關(guān)注

33文章

8650瀏覽量

151424 -

adc

+關(guān)注

關(guān)注

98文章

6514瀏覽量

545056 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1736瀏覽量

131595 -

端口

+關(guān)注

關(guān)注

4文章

979瀏覽量

32108

原文標(biāo)題:讀論文之《基于EV10AQ190的高速ADC接口設(shè)計(jì)》

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

EV10AQ190AVTPY 模擬多路復(fù)用器現(xiàn)貨

EV12DS460

求一款5ghz的ad轉(zhuǎn)換芯片

請(qǐng)問一下EV12AQ605有哪些特點(diǎn)?

EV8AQ160型ADC在2.5 Gsps雙通道高速信號(hào)采集系統(tǒng)中的應(yīng)用

FPGA與高速ADC和DAC的配合使用方法

關(guān)于高速ADC和DAC與FPGA的配合使用淺析

一種高速ADC接口電路設(shè)計(jì)方案

EV12AQ605,EV12AQ600面向競(jìng)爭(zhēng)激烈的大用量應(yīng)用的優(yōu)化版本

基于EV10AQ190的高速ADC接口設(shè)計(jì)

基于EV10AQ190的高速ADC接口設(shè)計(jì)

評(píng)論