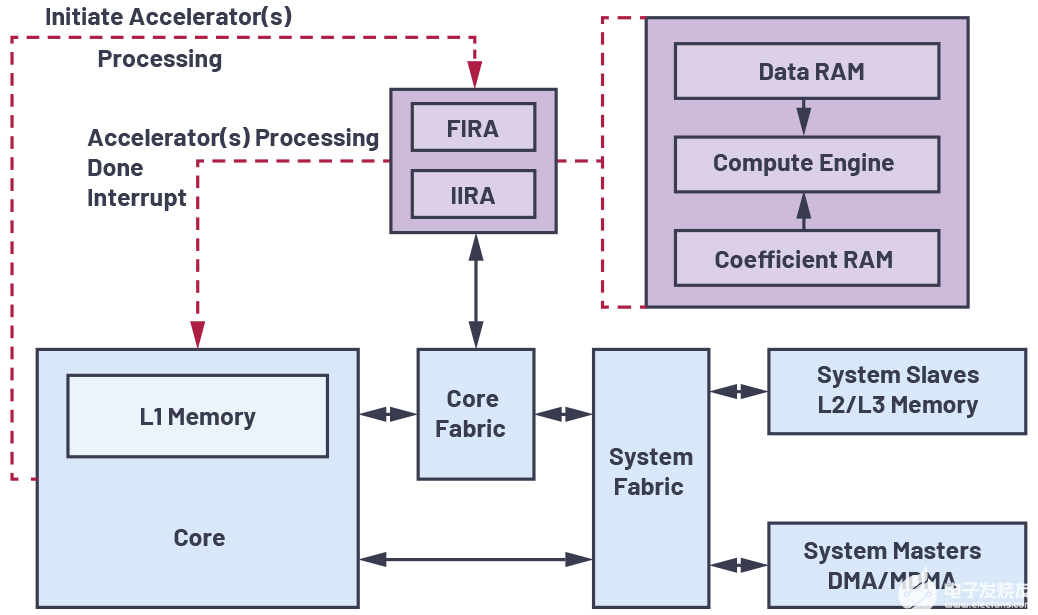

SHARC ADSP-2146x處理器集成了硬件加速器,可實現三種廣泛使用的信號處理操作:FIR(有限脈沖響應)、IIR(無限脈沖響應)和FFT(快速傅里葉變換)。加速器卸載了核心處理器,并有可能使處理器的計算吞吐量增加一倍以上。本文以加速器在下一代音頻系統中的應用為例。?

為什么選擇硬件加速器

數字信號處理中常用的FIR濾波器、IIR濾波器和FFT操作具有常規結構,允許在硬件(特別是硬件加速器)中直接實現。這些加速器是專用的固定功能外設,旨在反復執行單個計算密集型任務。它們卸載了主處理器,使其能夠執行結構幾乎沒有規律性的通用任務。

使用硬件加速器提供了一種經濟高效的方法來提高處理器的整體計算能力,因為系統設計人員獲得了通用處理器的靈活性以及專用硬件的計算優勢。

因此,這種加速器是滿足許多應用領域中越來越復雜系統需求的寶貴資產。其中之一是音頻系統,其中通道的數量正在增加。家庭影院系統從 5.1 聲道增加到 6.1 聲道,現在是 7.1 聲道。高端汽車放大器通常使用 12 個或更多揚聲器來讓聽眾沉浸在聲音中。

此外,音頻源材料現在以高清 (HD) 格式提供,其關聯的解碼器可擴展系統資源。此外,高清算法以更高的采樣率提供內容。以前,內容的峰值采樣率很少高于48 kHz。使用HD算法,采樣率通常為96 kHz,在某些情況下甚至高達192 kHz。

為了更好地了解計算需求是如何增加的,請考慮采用復雜房間均衡算法的最先進的家庭影院接收器。這些算法可補償驅動器響應和揚聲器位置的變化。算法首先使用麥克風和實時傳遞函數測量來分析房間。智能組合多個位置的測量值,然后為每個揚聲器設計補償濾波器。

更精確的房間均衡算法使用FIR濾波器來校正整個頻率范圍內的響應。所需濾波器的長度與采樣率成正比,需要更長的濾波器來精確控制低頻。256點的濾波器長度在48 kHz時很常見,而在96 kHz下實現相同的頻率分辨率需要512點的濾波器長度。采樣率和濾波器長度的加倍導致所需的計算量增加四倍。

SHARC ADSP-2146x中的加速器

ADI公司的SHARC處理器有著悠久的歷史,可在眾多應用中實現復雜的信號處理功能。處理器功能豐富的內核和外設使其成為產品開發人員的合理選擇。ADI公司最近推出的SHARC ADSP-2146x處理器通過更高的時鐘速度(450 MHz)和擴展的片上存儲器(5 Mb)鞏固了這一領導地位。

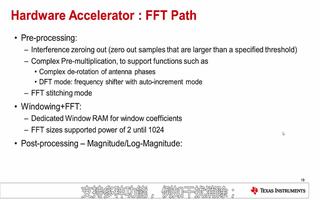

此外,該處理器還具有一組用于實現常見信號處理操作的硬件加速器:FIR 濾波器、IIR 濾波器和 FFT。這些操作構成了通信系統、醫療設備、消費產品以及工業測量和控制應用的基礎。這些加速器是對SHARC ADSP-2136x處理器中引入的板載采樣速率轉換器的補充,也可以被視為硬件加速器。

加速器架構

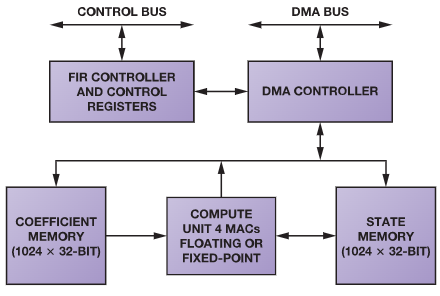

SHARC ADSP-2146x的所有三個加速器都具有相似的設計,這使得下面顯示的FIR加速器很好地說明了硬件加速器架構。FIR 加速器具有以下組件:

控制寄存器集 - 配置加速器的操作。

DMA 控制器 — 在主內存和加速器的本地內存之間移動數據。也可用于配置控制寄存器。

兩個本地內存塊 — 存儲系數和狀態變量(或延遲內存),并減少主內存的帶寬。

計算單元 - 包含為加速器定制的算術運算。FIR 計算單元有四個并行 MAC。

加速器的操作使用鏈式 DMA 自動執行。FIR 加速器通常通過以下步驟進行:

將此通道的系數數據從內部存儲器加載到本地加速器系數存儲。

將此通道的狀態變量從內部存儲器加載到本地加速器狀態變量存儲。這包括第一個輸入樣本。

使用四個 MAC 單元計算輸出樣本。

存儲結果。

如果還有樣本需要處理,則獲取下一個輸入樣本并寫入狀態變量存儲。

重復步驟3至5,直到計算出通道中的所有輸出樣本。

對所有輸入通道重復步驟 1 到 6。

ADSP-2146x內核的最大時鐘速率為450 MHz。通過使用 SIMD(單指令多數據),內核可以在每個時鐘周期執行兩次 MAC(乘法累加)運算,峰值速率為 900 MMAC/秒。相比之下,該加速器以225 MHz的SHARC外設時鐘速率運行。 FIR加速器使用其四個專用MAC單元,實現了900 MMAC/sec的峰值理論吞吐量。配置 FIR 加速器控制寄存器和將數據移入和移出本地內存會產生一些開銷。

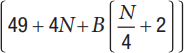

實現給定FIR濾波器所需的外設時鐘周期總數由公式給出

其中 N 是過濾器抽頭的數量,B 是塊大小。周期計數可以進一步細分為:

49 = DMA 傳輸控制塊初始化。

4N = 假設每個載荷有兩個周期,則加載系數和狀態值(延遲線)。

在實踐中使用加速器

應用軟件的設計必須能夠充分利用硬件加速器。請記住,加速器必須配置為與主 CPU 并行運行,因為如果主 CPU 處于空閑狀態等待加速器完成,則沒有任何好處。

加速器通常是在實時環境中運行的較大信號鏈的一部分。與加速器的接口需要雙緩沖輸入和輸出數據,系統設計人員應記住加速器會引入延遲塊。

考慮一個家庭影院系統,該系統具有 7.1 個 96 kHz 的音頻通道,以 32 個樣本的塊大小運行。假設房間均衡由八個FIR濾波器應用,每個濾波器長512點。如果核心CPU要執行濾波,則至少需要96 kHz×8×512 = 393 MMAC/秒或44 MHz SHARC處理器的450%。這種FIR處理代表了整個計算的很大一部分,幸運的是,可以卸載到加速器。FIR濾波器的輸入和輸出是雙緩沖的,允許加速器與音頻信號鏈的其余部分并行工作。雙緩沖在處理過程中引入了32個延遲樣本,在333 kHz時為可接受的96 μs。

使用前面的公式,加速器需要 50,056 個外圍循環才能完成操作。在225 MHz的速率下,這是223 μs,這完全在333 μs的阻塞時間內。

結論

音頻處理技術的不斷進步對音頻DSP提出了更高的要求。下一代SHARC ADSP-2146x處理器中的硬件加速器可顯著提高整體處理能力。加速器將常見的信號處理操作(FIR 濾波器、IIR 濾波器和 FFT 操作)從核心處理器中卸載出來,使其能夠專注于其他任務。這種經濟高效的方法使處理器的計算吞吐量增加了一倍以上。雖然本文側重于音頻應用,但內核和加速器是通用的,非常適合各種信號處理任務。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19849瀏覽量

234110 -

濾波器

+關注

關注

162文章

8116瀏覽量

181516 -

cpu

+關注

關注

68文章

11061瀏覽量

216445

發布評論請先 登錄

ADI推出Blackfin和SHARC處理器的下一代軟件開發平臺CCES

無法導入硬件加速器

如何充分利用數字信號處理器上的片內FIR和IIR硬件加速器?

性能提升1倍,成本直降50%!基于龍蜥指令加速的下一代云原生網關

高通下一代手機處理器3D與視頻性能展示

添加硬件加速器可以加快處理器的正弦計算

利用硬件加速器提高處理器的性能

基于Xilinx FPGA的Memcached硬件加速器的介紹

利用數字信號處理器上的片上FIR和IIR硬件加速器

評論