當今的基站系統(BTS)必須滿足各種不同的標準,并且必須滿足信號鏈各個模塊中的關鍵規范。以下本文介紹了高動態性能ADC、可變增益放大器、混頻器和本振等信號鏈組件的這些需求,并詳細介紹了它們在典型BTS應用中的使用,以及它們如何滿足對高動態性能、高交調性能和低噪聲的嚴格要求。

大多數數字接收器對高性能模數轉換器(ADC)和模擬元件提出了苛刻的要求。例如,在蜂窩基站數字接收器中,需要足夠的動態范圍來處理高電平干擾源(或阻塞信號),同時正確解調較低電平的所需信號。Maxim的MAX1418 15位65Msps或MAX1211 12位65Msps ADC與MAX9993 2GHz或MAX9982 900MHz集成混頻器相結合,可為接收器系列中最關鍵的兩個級提供出色的動態范圍。此外,Maxim的MAX2027和MAX2055 IF數字可變增益放大器(DVGA)具有極高的三階輸出交調截點性能(OIP3),具有許多應用所需的增益調節范圍。

蜂窩基站(BTS:基收發器站)由許多不同的硬件模塊組成,包括執行射頻接收器(Rx)和發射器(Tx)功能的模塊 - 即收發器(TRx)。在較舊的模擬放大器和 TACS BTS 中,一個收發器處理雙工 Rx 和 Tx 射頻載波。需要許多收發器來提供足夠的載波以獲得所需的呼叫覆蓋范圍。模擬技術正在被CDMA和WCDMA在全球范圍內取代,歐洲在十多年前就采用了GSM。在CDMA中,許多呼叫者使用相同的RF頻率,這允許單個收發器同時處理許多呼叫者的信號。如今存在各種CDMA和GSM設計,BTS制造商一直在尋求降低成本和功耗的方法。優化單載波解決方案或開發多載波接收器可以實現這一目標。圖1顯示了BTS設備中常用的子采樣接收器架構中的主要模塊。

圖1.子采樣接收器架構。

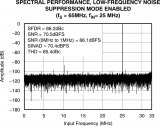

Maxim的MAX9993 2GHz混頻器和MAX9982 900MHz混頻器提供增益、高線性度以及低噪聲系數,使設計人員能夠消除許多設計中的有損無源混頻器。MAX2027和MAX2055設計工作在接收器的第一或第二中頻級。兩款器件均在整個增益調整范圍內提供+1dBm三階輸出交調截點(OIP2)性能。盡管MAX40 (3位1418Msps)和MAX15 (65位1211Msps)數據轉換器如圖12所示,但兩個轉換器系列都包含滿足大多數應用的其他速度等級。如果取消了第二個下變頻(以虛線顯示),則該圖描述了單個下變頻架構。

美信的低噪聲ADC,MAX1418

對于圖1所示的子采樣接收器架構,對ADC提出了嚴格的噪聲和失真要求。在接收器應用中,較低電平的目標信號單獨數字化,或者在存在幅度可能明顯較大的無用信號的情況下進行數字化。為了正確設計接收器,必須在這兩個信號極端下確定ADC有效噪聲系數。轉換器的噪聲系數是通過將其總噪聲功率與本底熱噪聲進行比較來確定的。對于小模擬輸入信號,熱+量化噪聲功率主導ADC的本底噪聲,用于近似ADC的有效噪聲系數(NF)。

在實踐中,一旦在小信號條件下知道ADC的有效噪聲系數,并確定模擬電路(RF&IF)的級聯噪聲系數,就會選擇ADC之前的最小功率增益以滿足所需的接收器噪聲系數。功率增益量決定了最大阻塞信號的上限,或者是接收器在ADC過載之前可以容忍的最高干擾電平。對于BTS應用,如果不實施自動增益控制(AGC),ADC通常沒有足夠的動態范圍來滿足噪聲系數要求(接收器靈敏度)和最大阻塞信號要求。AGC 可以包含在射頻級和/或中頻級中。

MAX1418系列中的其它轉換器針對基帶性能進行了優化,其中輸入= f時鐘/2.在此頻率范圍內工作并使用這些基帶優化部件可提供最佳的轉換器動態范圍。這些轉換器包括針對1419Msps時鐘速率優化的MAX65和針對1427Msps時鐘速率優化的MAX80,在基帶時SFDR性能均等于94.5dBc。

以下示例使用表1418中列出的MAX1規格:

表 1.MAX1418電氣特性

| 參數 | 條件 | 象征 | 典型值 | 單位 |

| 分辨率 | N | 15 | Bits | |

| 模擬輸入范圍 | VID | 2.56 | VP-P | |

| 差分輸入電阻 |

RIN |

1 | kΩ | |

| 交流規格 | f時鐘= 65毫秒 | |||

| 熱+量化本底噪聲 | 模擬輸入 = -35dBFS | Nfloor | -78.2 | dBFS |

| 信噪比模擬 = -2dBFS | fIN = 70兆赫 | 信 噪 比 | 73.6 | 分貝 |

| 無雜散動態范圍模擬 = -2dBFS | fIN = 70兆赫 | SFDR | 84 | 分貝 |

| 信噪比和失真模擬 = -2dBFS | fIN = 70兆赫 | SINAD | 73.3 | 分貝 |

MAX1418無需連接LSB即可與14位接口配合使用。如果這樣使用,SNR性能會略有下降,SFDR性能基本上不受影響。

圖2顯示了在沒有大電平阻塞器的情況下ADC噪聲貢獻。假設ADC前面的所有模擬電路的級聯噪聲系數均為3.5dB。作為第一個近似值,假設設計人員的目標是讓ADC將接收器總噪聲系數降低不超過0.2dB,以滿足CDMA基站接收器中的某些目標靈敏度。該噪聲系數值應為空口要求提供足夠的裕量,這也取決于最終探測器的Eb/No(位能量與噪聲功率譜密度比)要求。如果使用表1418中的MAX1熱+量化本底噪聲值,當器件時鐘頻率為26.9Msps (61倍芯片速率)時,可以計算出44.50dB的等效噪聲系數。由于實現了處理增益,1.23MHz CDMA通道帶寬中的ADC噪聲比奈奎斯特帶寬中的噪聲低14dB。需要36dB的總增益才能實現3.7dB的理想級聯接收器噪聲系數值。

圖2.無阻塞信號的ADC噪聲貢獻。

當增益領先于ADC36dB時,天線端的最大單音阻塞電平高于-30dBm將超過ADC滿量程輸入。cdma2000?蜂窩基站標準規定天線端子上允許的最大阻塞電平為-30dBm。在本例中,6dB增益降低用于增加施加到ADC的最大允許阻塞信號,從而為標準規格提供裕量。假設允許2dB裕量,6dB增益降低會導致天線的最大阻塞電平為-26dBm,ADC輸入端的最大阻塞電平為+4dBm(見圖3)。當存在單音阻塞信號時,蜂窩標準允許相對于基準靈敏度的整體(噪聲+失真)下降3dB。各個噪聲和失真分量的分配由設計人員決定。

假設設計人員允許RF前端級聯噪聲加上失真在阻塞信號施加1dBAGC的情況下將NF降低3dB(標稱5.6dB)。由于ADC前面只有30dB的增益,有效噪聲系數為29.4dB,由ADC SNR性能決定,在“阻塞條件”下,級聯接收器噪聲系數為5.7dB,與根據接收器靈敏度計算的2.3dB噪聲系數相比下降了7dB。由于該計算未考慮雜散性能,因此ADC的無雜散動態范圍(SFDR)性能可能會再降低1dB。當存在阻塞信號時,SINAD 可用于計算有效 NF,而不是單獨計算噪聲和 SFDR 貢獻。

圖3.ADC噪聲對阻塞信號的貢獻。

MAX1211允許單次下變頻架構

如果轉換器在較高的IF頻率下可以獲得足夠的SNR和SFDR性能,則子采樣架構可以與單個下變頻架構一起使用。Maxim的MAX1211是一款12位65Msps轉換器,設計時考慮了這種架構,并即將推出引腳兼容的80Msps和95Msps版本。該系列轉換器允許對高達 400MHz 的輸入頻率進行直接 IF 采樣,并具有差分或單端時鐘輸入等高級功能,允許 20% 至 80% 的時鐘占空比,數據有效指示器允許簡化時鐘和數據定時,2 的補碼或格雷碼數字輸出數據格式全部采用小型 40 引腳薄型 QFN 封裝 (6mm x 6mm x 0.8mm)。MAX2的典型交流規格見表1211,說明了175MHz模擬輸入頻率下出色的交流性能。 (注:改進型MAX1211版本將在大約一個月內上市,其交流規格見下表。

表 2.MAX1211電氣特性

| 參數 | 條件 | 象征 | 典型值 | 單位 |

| 分辨率 | N | 12 | Bits | |

| 模擬輸入范圍 | VID | 2 | VP-P | |

| 差分輸入電阻 | RIN | 15 | kΩ | |

| 交流規格 | f時鐘= 65毫秒 | |||

| 熱+量化本底噪聲 | 模擬輸入 = -35dBFS | Nfloor | 69.3 | dBFS |

| 信噪比模擬 = -0.2dBFS |

fIN= 32.5兆赫 fIN= 175兆赫 |

信 噪 比 |

68.3 66.8 |

分貝 |

| 無雜散動態范圍模擬 = -0.2dBFS |

fIN= 32.5兆赫 fIN= 175兆赫 |

SFDR |

82.4 79.7 |

分貝 |

| 信噪比和失真模擬 = -2dBFS |

fIN= 32.5兆赫 fIN= 175兆赫 |

SINAD |

68.1 66.5 |

分貝 |

選擇單次向下轉換而不是雙次向下轉換時,可以獲得顯著的優勢。通過消除第二個下變頻混頻器、秒中頻增益級和 2德·LO頻率合成器電路,器件數量和電路板空間可減少約10%,成本可減少10至20美元。

不同架構的雜散考慮

如果節省器件數量、電路板空間、功耗和成本不能提供足夠的激勵,以下示例說明了在單下變頻架構中使用MAX1211時獲得的頻率規劃優勢。假設cdma2000接收器設計為在PCS頻段內工作。對于61.44Msps的采樣速率和30.72MHz的合成器參考頻率,請選擇以第六奈奎斯特頻段為中心的第一中頻頻率,頻率為169MHz,帶寬約為1.24MHz。使用相同的第一中頻中心頻率 169MHz,DDC 架構假設 2德·中頻頻率居中為 2德·奈奎斯特頻段為46.08MHz。

表 3.SDC 和 DDC 架構的刺激搜索假設

| SDC | DDC | 參數 | 價值 |

| x | x | 接收頻段 | 1904.3800 至 1905.6200MHz |

| x | x | 時鐘頻率 | 61.44000兆赫 |

| x | x | 最大時鐘諧波 | 30 |

| x | x | 合成器參考頻率 | 30.7200兆赫 |

| x | x | 最大合成器諧波 | 40 |

| x | x | 首次注射LS | 1736.0000兆赫 |

| x | x | 最大第一LO諧波 | 5 |

| x | x | 接收圖像波段 | 1566.3800 至 1567.6200MHz |

| x | x | 第一個中頻波段 | 168.3800 至 169.6200MHz |

| x | 第二次注射LS | 122.9200兆赫 | |

| x | 最大第二LO諧波 | 5 | |

| x | 第一中頻影像波段 | 76.2200 至 77.4600MHz | |

| x | 第二中頻波段 | 45.4600 至 46.7000MHz |

表3列出了單載波、單下變頻(SDC)和雙下變頻(DDC)架構中接近PCS頻段上限的RF載波的雜散搜索假設。對于SDC架構,雜散搜索在RF接收頻段、接收鏡像頻段、IF頻段和IF鏡像頻段總共產生134個雜散。這些雜散中的大多數都是高階的,不會降低接收器的性能。對于 DDC 架構,此雜散搜索結果超過 2400 個雜散,是 SDC 架構計算結果的 18 倍。這些雜散產物出現在RF接收頻帶、接收鏡像頻帶、1圣中頻波段,1圣中頻像段,2德·中頻波段和 2德·中頻圖像波段。通過良好的電路板布局實踐和濾波,由較高時鐘諧波和頻率合成器參考頻率組合產生的雜散將相對容易降低。然而,大量的低階雜散將難以最小化。

Maxim的IF放大器,MAX2027和MAX2055

Maxim還提供高性能IF放大器,具有以1dB增量進行數字可變增益控制。MAX2027為數字可變增益放大器(DVGA),具有單端輸入/單端輸出,頻率范圍為50MHz至400MHz。該DVGA在最大增益下提供5dB的低噪聲系數。MAX2055為單端輸入/差分輸出DVGA,用于驅動頻率范圍為30MHz至300MHz的高性能ADC。升壓變壓器可在MAX2055的差分輸出和ADC差分輸入之間使用。變壓器由差分驅動;從而優化變壓器性能和輸出信號之間的平衡。兩個DVGA均采用5V偏置工作,在所有增益設置范圍內具有+40dBm OIP3。

Maxim的高線性度混頻器,MAX9993和MAX9982

在接收器電路中,混頻器受到大輸入信號的影響,這對它們的性能提出了嚴格的要求。理想情況下,混頻器輸出信號的幅度和相位與輸入信號的幅度和相位成正比,與LO信號特性無關。根據這一假設,混頻器的幅度響應對于RF輸入是線性的,并且與LO輸入無關。

然而,混頻器的非線性會產生不需要的混頻產物,稱為雜散響應,這是由于不需要的信號到達混頻器的RF輸入端口并在IF頻率下產生響應引起的。當它們干擾所需的IF頻率時,混頻機制可以描述為:

f如果= ±毫頻射頻±瞧其中IF、RF和LO分別指指定端口的信號,m和n是RF和LO頻率的整數諧波,它們混合以產生許多雜散產物的組合。

集成(或有源)平衡混頻器設計,如Maxim的MAX9993和MAX9982,其性能可與無源混頻器方案相媲美,因此越來越受歡迎。平衡混頻器在 m 或 n 偶數時抑制某些雜散響應,從而產生出色的 2德·階諧波性能。理想的雙平衡混頻器可抑制m或n(或兩者)為偶數的所有響應。IF、RF和LO端口在所有雙平衡混頻器中相互隔離。使用設計合理的巴倫,這些混頻器可以具有重疊的RF、IF和LO頻段。MAX9993和MAX9982的特性包括:增益、低噪聲系數、集成LO緩沖器、低LO驅動、允許兩個LO頻率輸入的LO開關、出色的LO噪聲性能以及RF和LO端口上的集成RF巴倫。

Maxim的混頻器內置LO緩沖器,具有出色的LO噪聲性能,可降低驅動它們的輸入LO功率要求。LO噪聲與高電平輸入阻塞信號相互混合,使接收器脫敏。MAX9993和MAX9982均具有低噪聲LO緩沖器,設計在存在阻塞信號時對接收器脫敏的影響最小。例如,假設提供注入信號的VCO具有-145dBc/Hz的邊帶噪聲性能。MAX9993的典型LO噪聲性能為-164dBc/Hz,因此復合邊帶噪聲性能僅下降0.05dBc/Hz至-144.95dBc/Hz。這樣,用戶不僅需要向混頻器提供低電平LO注入信號,而且可以確保接收器的互易混頻性能不會因MAX9993 LO緩沖器性能而下降。

特別麻煩的2德·階次雜散響應稱為半IF(1/2 IF)雜散響應,用于低邊注入的混頻器指數(m = 2,n = -2)和(m = -2,n = 2)用于高端注入。對于低側注入,產生半中頻雜散響應的輸入頻率位于所需RF頻率以下,數量為f如果/2所需的RF輸入頻率(見圖4)。所需的RF頻率由1909MHz表示,結合LO頻率1740MHz,得到的IF頻率為169MHz。雖然CDMA RF和IF載波占用1.24MHz帶寬,但它表示為表示中心載波頻率的單個頻率。在本例中,1824.5MHz處的不需要信號會導致169MHz處的半IF雜散產物。

驗證:

2 x fHalf-IF - 2 x fLO =

2 x (fRF - fIF/2) - 2 x (fRF - fIF) =

2 x (fRF - 2 x fIF/2) - 2 x fRF + 2 x fIF = fIF

結果在:

2 x 1824.5MHz - 2 x 1740MHz = 169MHz

圖4.所需頻率的位置射頻, f瞧, f如果和不需要的 f半中頻。

抑制量稱為2x2雜散響應,可通過混頻器的二階交調截點IP2進行預測。圖2中的2x5 IMR或雜散值取自Maxim的MAX9993數據資料。請注意,圖中的信號電平是指計算輸入IP2(IIP2)性能的混頻器的輸入。

如此卓越的 2x2 性能水平可帶來以下結果:

IIP2 = 2 x IMR + PSPUR = IMR + PRF

= 2 x 70dBc + (-75dBm) = 70dBc + (-5dBm)

= +65dBm

類似地,Maxim的MAX9982 900 MHz有源混頻器在類似條件下提供相當于2dBc的典型2RF - 65LO雜散響應,從而產生:

IIP2 = 2 x IMR + PSPUR = IMR + PRF

= 2 x 65dBc + (-70dBm) = 65dBc + (-5dBm)

= +60dBm

圖5.2德·-參考混頻器輸入的信號的階次截點計算,IIP2。

混頻器前方RF路徑中使用的鏡像抑制濾波器可衰減任何放大器諧波。LO路徑中的噪聲濾波器衰減由LO注入源引起的諧波。高電平輸入信號會產生失真或互調產物,可以通過計算器件或系統輸入或輸出端的截點來量化。對于混頻器LO功率保持恒定的情況,交調截點或失真積的階數僅由RF乘法器決定,而不由LO乘法器決定,因為RF信號的變化僅是問題。階數是指失真產物的幅度隨著輸入電平的升高而增加的速度。

研究表明,Maxim的MAX1418 15位ADC具有出色的噪聲性能,因此所需的接收器增益較低,因此能夠以最小的AGC承受更高的阻塞或干擾電平。MAX1211 ADC系列非常適合單變頻接收器架構,具有1圣中頻輸入頻率高達400MHz。此外,Maxim的RF MAX9993和MAX9982混頻器提供所需的線性度、低噪聲系數和足夠的功率增益,無需當今許多接收器設計中的無源混頻器。Maxim的MAX2027和MAX2055 DVGA在整個增益調整范圍內提供約+3dBm的典型OIP40值。綜上所述,包含這些組件的接收器陣容可以在極具成本效益的解決方案中實現高水平的性能。

審核編輯:郭婷

-

放大器

+關注

關注

143文章

13589瀏覽量

213402 -

接收器

+關注

關注

14文章

2468瀏覽量

71889 -

adc

+關注

關注

98文章

6497瀏覽量

544510

發布評論請先 登錄

相關推薦

如何實現超寬帶直接轉換接收器的性能優化

基于RF混頻器的3G無線基站接收器應用

數字接收機中高性能ADC和射頻器件的動態性能要求

數字接收機中高性能ADC和射頻器件的動態性能要求

基于分集接收機實現高性能系統

數字接收器應用中高性能ADC和RF元件的動態性能要求

數字接收器應用中高性能ADC和RF元件的動態性能要求

評論