LVDS(Low-Voltage Differential Signaling ,低電壓差分信號)是美國國家半導(dǎo)體(National Semiconductor, NS,現(xiàn)TI)于1994年提出的一種信號傳輸模式的電平標準,它采用極低的電壓擺幅高速差動傳輸數(shù)據(jù),可以實現(xiàn)點對點或一點對多點的連接,具有低功耗、低誤碼率、低串擾和低輻射等優(yōu)點,已經(jīng)被廣泛應(yīng)用于串行高速數(shù)據(jù)通訊場合當中。

LVDS技術(shù)規(guī)范有兩個標準,即TIA(電訊工業(yè)聯(lián)盟)/EIA(電子工業(yè)聯(lián)盟)的ANSI/TIA/EIA-644標準(LVDS接口也因此稱為RS-644接口)與IEEE 1596.3標準。

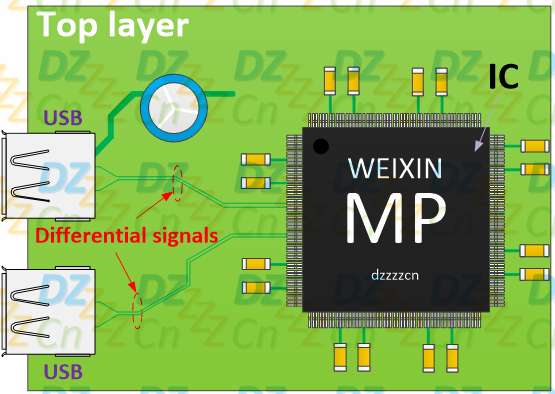

LVDS電平標準采用一對(兩根)差分信號線傳輸數(shù)據(jù)。我們最常見的差分信號線就是USB(Universal Serial Bus, 通用串行總線),現(xiàn)如今,任何一臺PC電腦上都會有USB接口,它可以用來連接U盤、鍵盤、鼠標、打印機、移動硬盤等等,如下圖所示:

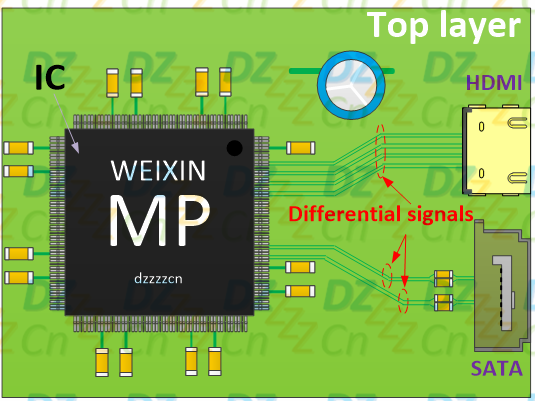

HDMI(High Definition Multimedia Interface, 高清晰度多媒體接口)是一種數(shù)字化音視頻接口技術(shù),適合影像傳輸?shù)膶S眯蛿?shù)字化接口,它由4對差分線組成。我們使用的SATA(Serial Advanced Technology Attachment,串行ATA接口規(guī)范)硬盤也包含接收與發(fā)送兩對差分信號線,如下圖所示:

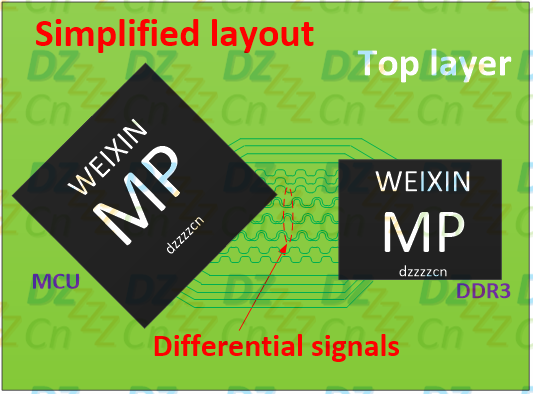

有過DDR3 SDRAM應(yīng)用經(jīng)驗的讀者也會發(fā)現(xiàn)有幾對差分線,如下圖所示:

很遺憾地告訴大家,以上幾種接口的差分信號線使用的都不是嚴格意義上的LVDS電平標準(但很多基礎(chǔ)概念都是相通的),換言之,不是所有的差分信號線都是LVDS電平標準,使用差分信號線進行數(shù)據(jù)傳輸?shù)木唧w電平有很多種,LVDS只是其中之一。

比如,HDMI使用TMDS(Time Minimized Differential Signal, 最小化傳輸差分信號),DDR3使用SSTL(Stub series terminated logic,短截線串聯(lián)端接邏輯)。HDMI(TMDS)、USB與SATA使用的電平標準與LVDS很相似,但從其規(guī)范來看并不是標準的LVDS(它們也是“低電壓差分信號”,但不是我們這里所說的LVDS),不能認為是同一種電平標準(就如同我們不能認為5V TTL電平標準與5V CMOS電平標準是相同的,盡管看起來參數(shù)差別不大),而SSTL(包括SSTL_3、SSTL_2、SSTL_18、SSTL_15)與LVDS就完全不是一個東西了。

當然,只要是使用差分信號線進行數(shù)據(jù)的傳輸應(yīng)用,它們對于PCB布線的要求都是大同小異的,這一點我們將在《高速PCB設(shè)計》專欄文章中詳述。

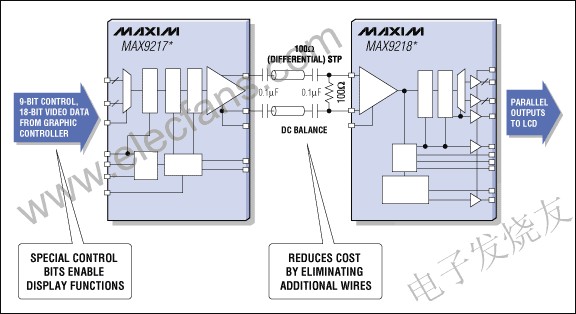

盡管如此(上面都不是LVDS電平標準),LVDS電平標準接口的應(yīng)用場合還是非常廣泛,LVDS接口的液晶顯示屏就是其中之一,它是LCD Panel的通用接口標準。那么到底是什么原因使得LVDS這么受青睞呢?我們從最基本的LVDS硬件收發(fā)器來談?wù)勂稹?/p>

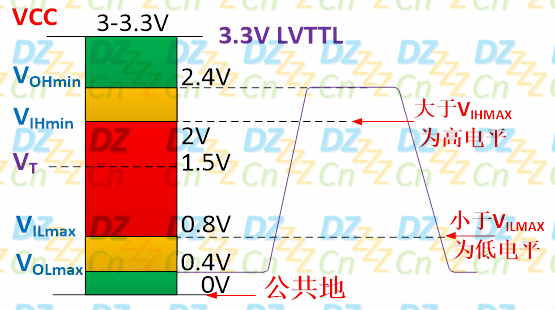

通常大多數(shù)低速數(shù)字邏輯電平(如TTL、CMOS)是以電壓對參考地的幅值來判斷是高電平還是低電平,如下圖所示:

而LVDS卻完全不一樣,它是通過數(shù)據(jù)接收器同相端與反相端的電壓相對大小判斷高低電平的,而不是通過同相端或反相端對公共地(GND)。

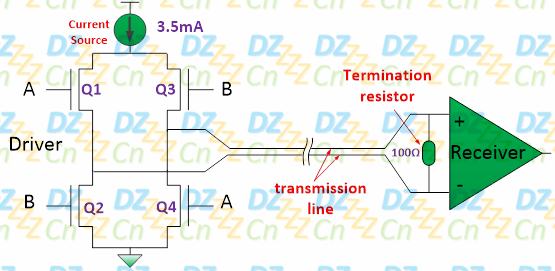

LVDS的發(fā)送器與接收器的基本結(jié)構(gòu)如下圖所示。它使用兩根線(即差分信號線)來傳輸一個信號,并且使用恒流源(Current Source)驅(qū)動,即電流驅(qū)動型(而TTL、CMOS之類電平標準為電壓驅(qū)動型)。

其中,驅(qū)動器(Driver)中的場效應(yīng)管Q1、Q2、Q3、Q4(不一定是場效應(yīng)管,因為LVDS技術(shù)規(guī)范主要側(cè)重于LVDS接口的電氣我、互連與線路端接,對于生產(chǎn)工藝、傳輸介質(zhì)及供電電壓無明確要求,也就是說,可以采用CMOS、GaAs或其它工藝實現(xiàn),能抓到老鼠的黑貓白貓都是好貓)組成一個全橋開關(guān)電路,用來控制3.5mA恒流源的電流流動方向,接收器(Receiver)的同相與反相端之間并聯(lián)了一個100歐姆的端接電阻,這樣電流經(jīng)過電阻即可產(chǎn)生電壓,再經(jīng)過接收器判斷就形成了高低電平。

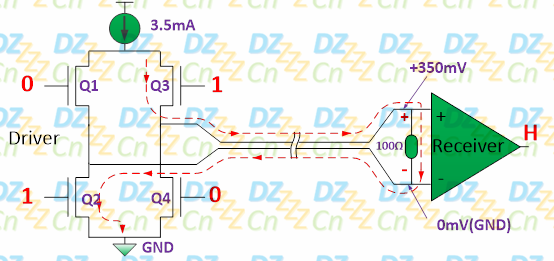

當Q2、Q3導(dǎo)通而Q1、Q4截止時,恒流源電流經(jīng)Q3流向接收器,并向下穿過100歐姆端接電阻再返回至驅(qū)動端,最后經(jīng)Q2到地(GND),3.5mA的電流在100歐姆電阻上產(chǎn)生350mV的壓降,此時同相端電壓高于反相端電壓,輸出為高電平“H”,如下圖所示:

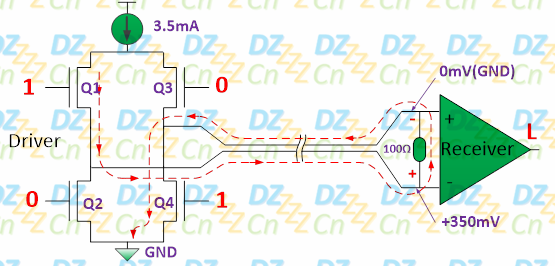

而當Q2、Q3截止而Q1、Q4導(dǎo)通時,恒流源電流經(jīng)Q1向右流向接收器,并向上穿過100歐姆端接電阻再返回至驅(qū)動端,最后經(jīng)Q4到地(GND),3.5mA的電流在100歐姆電阻上也產(chǎn)生350mV的壓降,但此時同相端電壓低于反相端電壓,輸出為高電平“L”,如下圖所示:

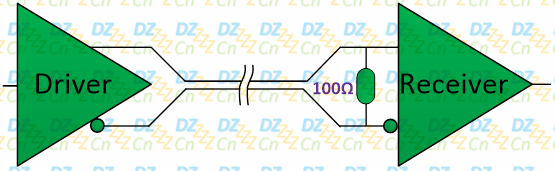

通常我們將LVDS接收器與發(fā)送器簡化成類似下圖所示:

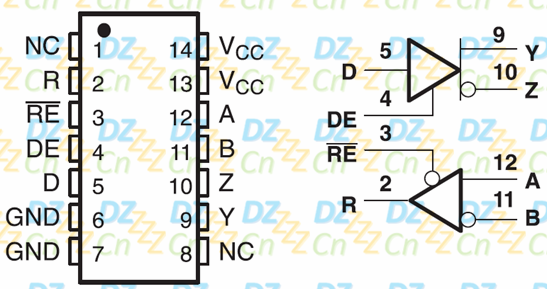

如下圖所示(來自TI公司LVDS收發(fā)芯片SN65LVDS180數(shù)據(jù)手冊)

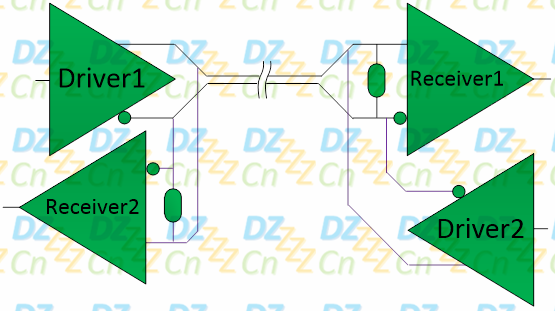

從LVDS結(jié)構(gòu)原理可以看出,一對差分信號線只能夠進行一個方向的數(shù)據(jù)傳輸,即單工通信(也稱為點對點傳輸,point-to-point),但是我們常見的USB接口也只是使用一對差分信號線,為什么卻可以雙向傳輸呢?原因很簡單,它是使用兩對驅(qū)動器與接收器組合而成的,如下圖所示:

這是一種半雙工(half duplex)的配置結(jié)構(gòu),也就是說,在任意時刻差分信號線仍然只能是往一個方向傳輸數(shù)據(jù),但可以分時進行雙向數(shù)據(jù)傳輸,當驅(qū)動器1向接收器1發(fā)送數(shù)據(jù)時,驅(qū)動器2與接收器2相當于無效的,反之亦然。

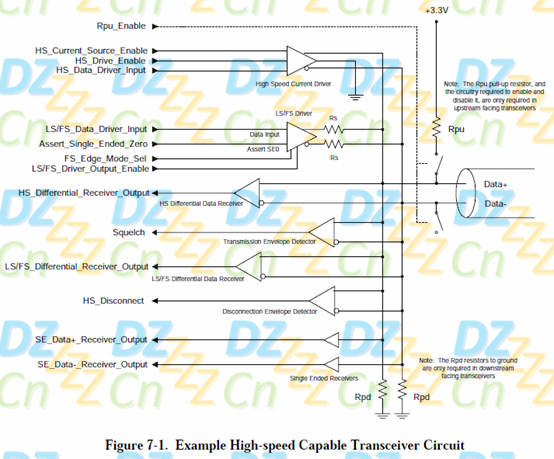

當然,USB總線的實際結(jié)構(gòu)要復(fù)雜得多,如下圖所示(來自USB2.0規(guī)范,扯遠了)

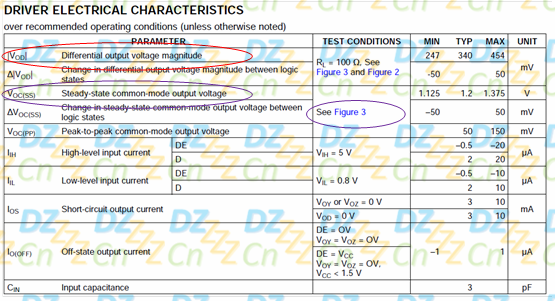

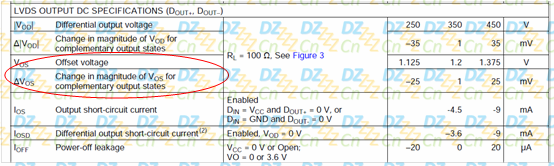

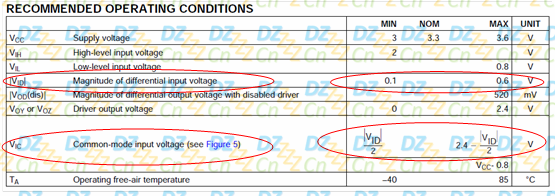

我們來看看如下圖所示的LVDS驅(qū)動器電氣參數(shù)(來自TI公司LVDS收發(fā)芯片SN65LVDS180數(shù)據(jù)手冊)

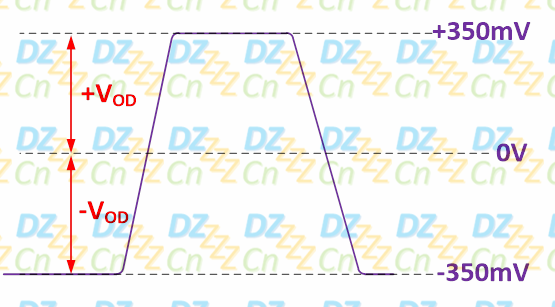

上表中的VOD(Differential output voltage magnitude)即驅(qū)動器的差分輸出電壓幅度,也就是前述在端接電阻上產(chǎn)生的350mV壓降,我們可以用下圖所示(注意:是差模信號):

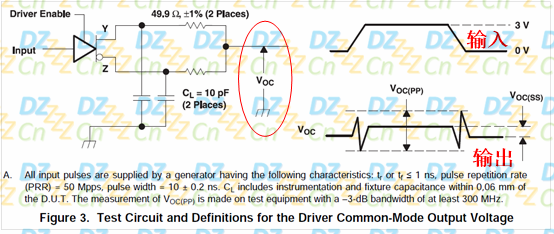

表中還有一個VOC(SS)(Steady-state common-mode output voltage)即穩(wěn)態(tài)共模輸出電壓是個什么東西呢?我也不是很明白!咱們按圖索驥找到數(shù)據(jù)手冊中的Figure 3,如下圖所示:

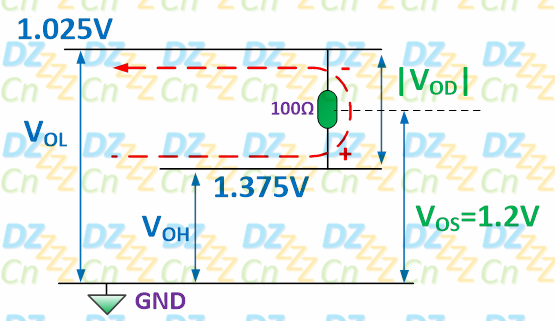

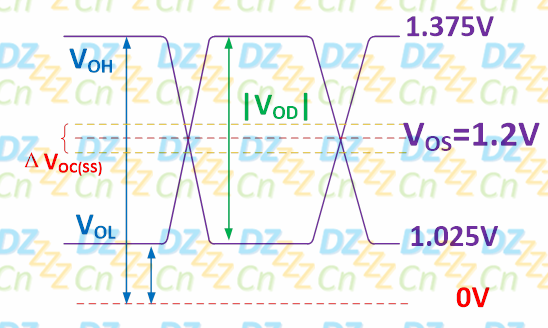

哦,原來是當驅(qū)動器輸入數(shù)字信號(未轉(zhuǎn)換成LVDS信號前)時,轉(zhuǎn)換出來的LVDS信號電壓對公共地的平均值,也稱為VOS(Offset Voltage,),TI公司的其它數(shù)據(jù)手冊有使用VOS如下圖所示:(來自TI公司的LVDS收發(fā)芯片型號SN65LVDS049數(shù)據(jù)手冊)

我們之前講過,當使用LVDS電平標準傳輸高低電平時,接收端收到了+350mV或-350mV的壓降只是差模信號,實際上還有一定的共模信號,它不影響接收器進行數(shù)據(jù)的判斷。

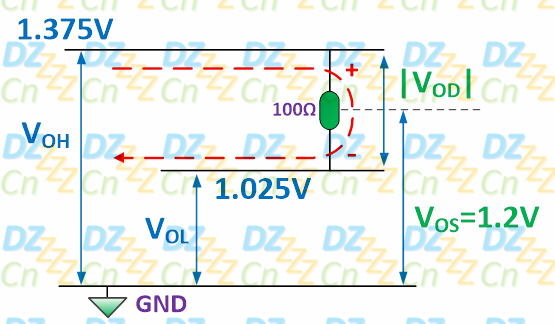

當驅(qū)動器向接收器發(fā)送高電平“H”時,其等效圖如下所示(注意:這個等效圖僅適合傳輸線非常短的條件下):

當驅(qū)動器向接收器發(fā)送低電平“L”時,其等效圖如下圖所示

綜合以上兩種等效電路,我們有如下圖所示的電平波形圖:

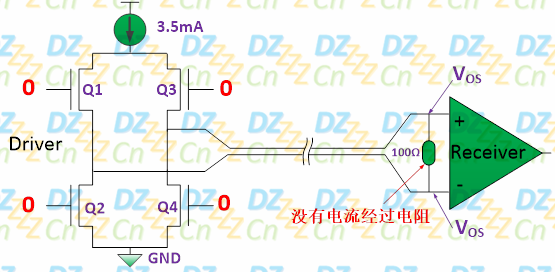

換言之,當LVDS進行高低電平切換時,電流源的電流在換向的瞬間,端接電阻流過的電流為零,因此端接電阻兩端的電壓就是VOS(電阻兩端電壓相同,因此沒有壓降,也沒有電流),如下圖所示:

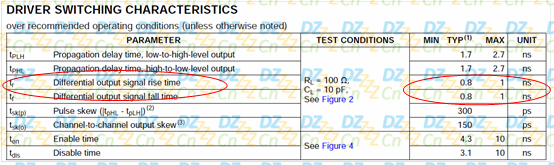

當然,這個電流換向轉(zhuǎn)換瞬間非常短,通常只有幾百皮秒,如下圖所示:

接收器的輸入電氣參數(shù)如下圖所示:

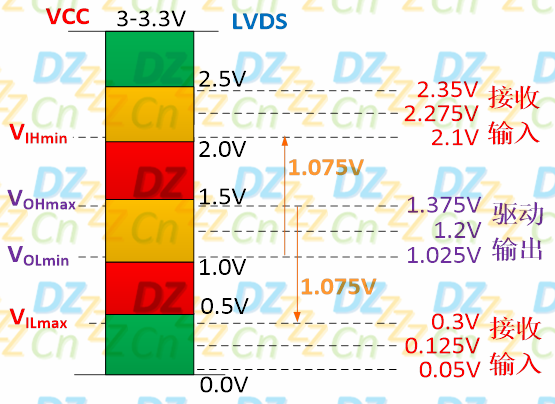

因此我們也可以用下圖表示LVDS電平標準的噪聲容限(關(guān)于噪聲容限請參考《邏輯門2》)

從圖中可以看到,LVDS電平標準的噪聲容限約為1.075V(一般認為其噪聲容限為 1V)這里我們只是根據(jù)TI數(shù)據(jù)手冊畫出電平標準圖,沒有做任何修改,不同廠家的信息可能略有不同。

導(dǎo)演,講了半天還沒提到為什么LVDS信號速度快、抗干擾能力強呀?為什么有些差分線串聯(lián)了電容?為什么不同差分線的阻抗會不一樣?了解了這些基礎(chǔ)知識,我們下節(jié)再來討論一下LVDS電平標準的這些特點。

-

CMOS

+關(guān)注

關(guān)注

58文章

5710瀏覽量

235418 -

HDMI

+關(guān)注

關(guān)注

32文章

1694瀏覽量

151864 -

接口

+關(guān)注

關(guān)注

33文章

8575瀏覽量

151021 -

lvds

+關(guān)注

關(guān)注

2文章

1043瀏覽量

65793 -

差分信號

+關(guān)注

關(guān)注

3文章

367瀏覽量

27678

發(fā)布評論請先 登錄

相關(guān)推薦

差分信號的優(yōu)勢和影響

LVDS差分信號抗噪特性

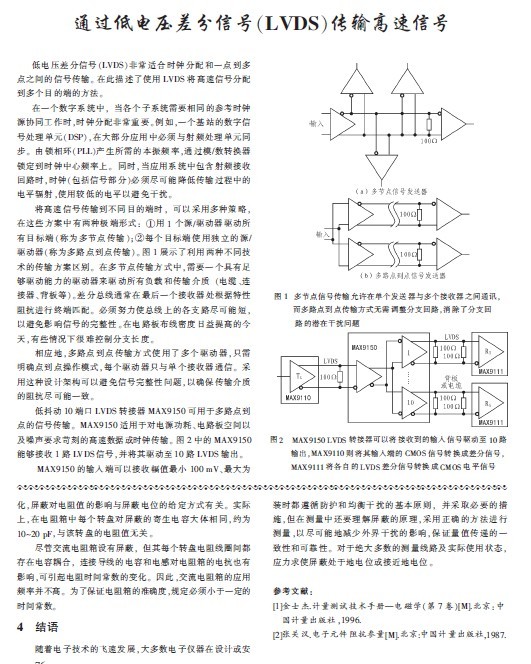

通過低電壓差分信號(LVDS)傳輸高速信號

通過低電壓差分信號(LVDS)傳輸高速信號

低電壓差分信號傳輸(LVDS)在汽車電子中的應(yīng)用

未使用端接的低電壓差分信號總線輸入方案

ADI推出多點低電壓差分信號收發(fā)器ADN469xE

LVDS低電壓差分信號的優(yōu)點及布板注意事項

LVDS振幅差分信號技術(shù)的優(yōu)勢和劣勢

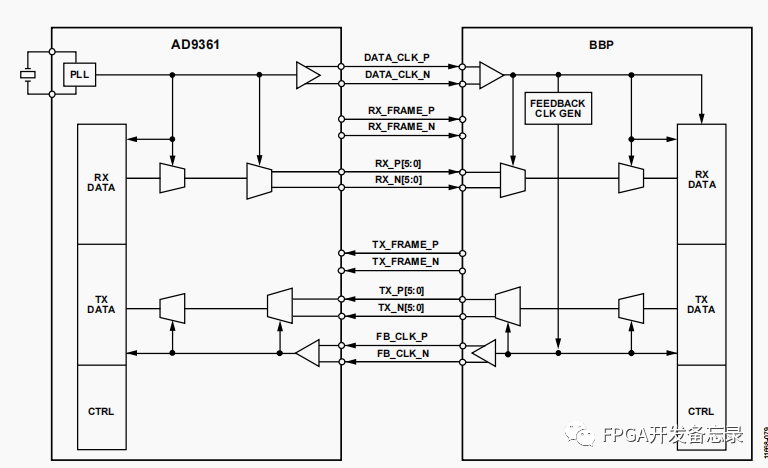

AD9361數(shù)據(jù)路徑在低電壓差分信號(LVDS)模式下運行

低電壓差分信號(LVDS)接口浪涌靜電放電防護電路圖

一文詳解LVDS低電壓差分信號

一文詳解LVDS低電壓差分信號

評論