鎖相環(PLL)頻率生成電路廣泛用于多個行業和應用中,包括基本的 FM 廣播頻段接收器、數字通信、航空航天、儀器儀表、雷達和電子戰。鎖相環用于生成從小于 1MHz 到數十 GHz 及以上的射頻(RF)和中頻(IF)信號。應用要求變化很大,鎖相環設計和優化需要權衡考量功耗、相位噪聲、頻率調諧范圍、頻率分辨率和鎖定時間等參數。

設計過程中必須權衡考量頻率范圍與相位噪聲性能,這一點很重要,如果處理不當,常常會導致性能下降。寬帶壓控振蕩器(VCO)以犧牲出色的相位噪聲性能為代價,提供較寬的頻率范圍。相比之下,窄帶VCO 以犧牲可達到的調諧范圍為代價,提供更好的相位噪聲。可以將多個窄帶 VCO 多路復用,以實現更寬的調諧范圍,但這通常不切實際——需要復雜的外部電路將電源切換給單個 VCO,并選擇適當的 RF輸出。

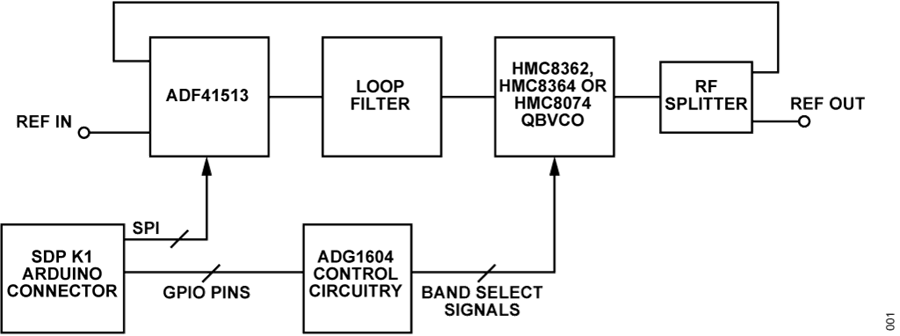

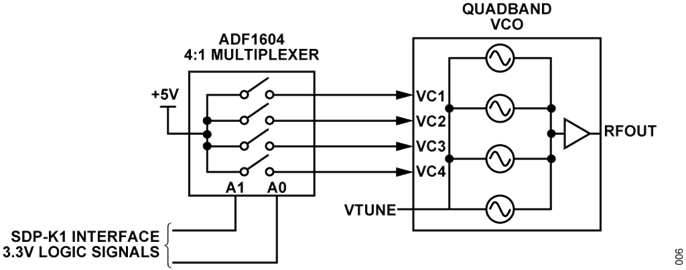

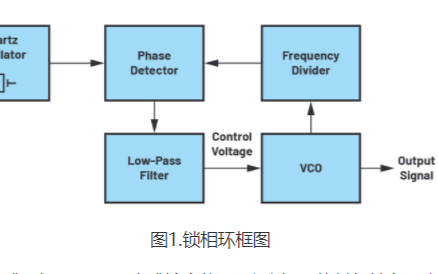

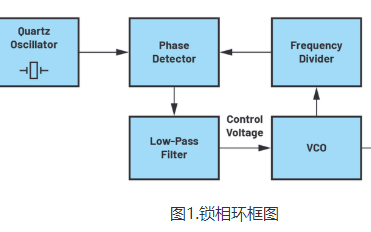

圖 1 所示的電路包含一個集成式四頻 VCO,由四個集成在單個封裝中的窄帶 VCO 組成(下文簡稱該電路為CN0568)。這種設計的優勢在于:它保留了窄帶 VCO 出色的相位噪聲,同時還提供較寬的工作頻率范圍。VCO 頻段通過板載多路復用器電路進行切換,該電路根據主機編程設置的頻率從四個 VCO 中選擇。

圖 1. CN0568 功能框圖

這種切換電路經過優化,可以提供快速 VCO 頻段切換,減少了從最低頻段到最高頻段的總鎖定時間。對于需要在寬頻率范圍內保持快速切換時間的應用,例如快速跳頻,這是有利的。

對于需要高精度的相位再現的波束成形等應用,PLL內置的相位再同步和相位調整功能都非常有用。該電路兼容 Arduino 尺寸平臺板,可以堆疊多個板,共用同一個數字接口。

電路描述

PLL 合成器

本電路選擇 ADF41513 用作 PLL 頻率合成器,它具有 1GHz 至 26.5GHz 寬工作頻率范圍,涵蓋 3 種四頻 VCO 的整個頻率范圍。在小數模式下,∑-Δ 調制器提供 sub-Hz 頻率分辨率。ADF41513 還具有超低本底噪聲性能,在整數模式下為-235 dBc/Hz,在小數模式下為-231 dBc/Hz,以實現出色的相位噪聲性能。

基準輸入

EVAL-CN0568-ARDxZ 可以進行配置,支持來自REFIN SMA 連接器的外部基準頻率,或用于板載超低相位噪聲 100MHz 晶體振蕩器。具有 82fs 低抖動和-90 dBC/Hz 近載波相位噪聲。默認情況下,該板配置采用板載晶體振蕩器選項;通過移除 R8,并在 R28 中插入一個 0 ? 電阻來選擇外部輸入。對于需要 100MHz 基準電壓源的用例,推薦使用板載基準電壓源。

環路濾波器

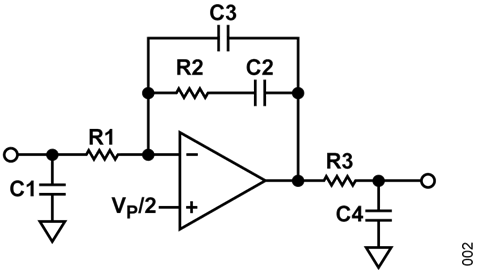

由于 ADF41513 PLL 的電荷泵的工作電壓為 0 至3.3v,這 3 種四頻 VCO 需要 1.0V 至 13.5V 調諧電壓,因此需要具有增益的有源環路濾波器電路。環路濾波器的設計目標是在每個 VCO 頻段的頻率范圍內盡可能提高穩定性,環路帶寬約為 100kHz,相位裕量為 50°。當所選的 VCO 頻段內的調諧靈敏度(頻率與調諧電壓斜率)發生變化時,環路濾波器帶寬根據工作頻率也會略微變化。環路濾波器設計用于使用 100 MHz 基準頻率,如果需要使用其他基準頻率,則需要重新設計。ADISimPLL 工具可用于確定合適的環路濾波器拓撲結構,并使用仿真模型計算所需帶寬和相位裕量等必要的元件值。

采用五階環路濾波器拓撲,是因為它具有更高的帶外滾降,以及更出色的 Σ-Δ 調制器噪聲和雜散衰減性能。環路濾波器中選擇使用的運算放大器是 ADA4625 ,它具有低噪聲性能,可以使用軌到軌電源。圖 2 顯示使用的環路濾波器配置的示意圖。圖3 顯示板載環路濾波器的尺寸。

圖 2. 環路濾波器原理圖

圖 3. 環路濾波器尺寸

電壓控制振蕩器

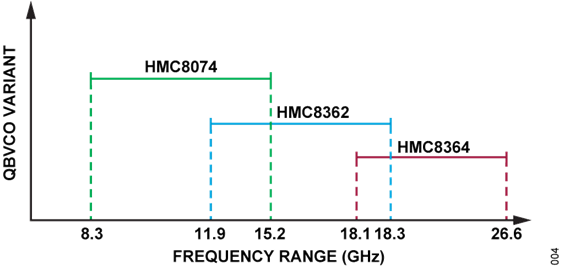

HMC8074/HMC8362/HMC8364 四頻 VCO 每個都由 4 個獨立的窄帶 VCO 內核組成,這些內核集成在單個 LFCSP 封裝中。為對應的內核提供 5v 電源電壓,如此可以選擇每個內核。在任何給定時間內,只能啟用一個內核,以確保輸出緩沖放大器不被過驅動。因為每個內部 VCO 內核的窄帶性能,這些四頻 VCO 具有寬帶 VCO 的頻率范圍,同時保持了出色的相位噪聲性能。

在給定器件版本的所有 4 個頻段內,VCO 調諧曲線保持一致,因此可以使用單個環路濾波器來調節所有頻段。這些四頻 VCO還為功率敏感型應用提供 75mA 的低電流消耗(典型值),包括緩沖放大器。這三種四頻 VCO 版本覆蓋 8.3GHz 至 26.6GHz 的頻率范圍。每個四頻VCO 的頻率范圍如下:

HMC8074:8.3 GHz至15.2 GHz

HMC8362:11.9 GHz至18.3 GHz

HMC8364:18.1 GHz至26.6 GHz

圖 4. 四頻 VCO 版本的頻率范圍

雖然 HMC8364 能夠使用 ADF41513 的最大頻率26.5GHz,但 EVAL-CN0568-ARDxZ 的工作頻率范圍限制在 24GHz。詳細說明參見 頻率靈敏度 部分。

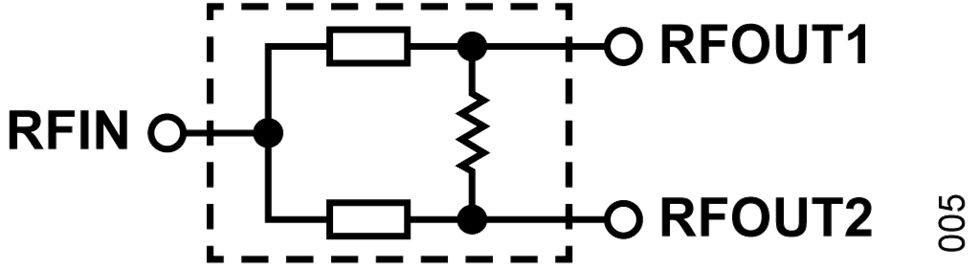

RF 分路器

寬帶寬(1.8-28GHz)、1:2 RF 分路器將 VCO 輸出拆分,分別輸出到 CN0568 RF 輸出端口和 PLL RF 反饋路徑。選擇這種分路器的主要原因在于,它具有2GHz 至 26.5GHz 寬工作帶寬范圍。這意味著,分頻器可以在所有三種四頻 VCO 的頻率范圍內使用。EP2K1+還具有 2.5W 高功率處理能力,尺寸小巧,為 4x4mm。

圖 5. RF 分路器簡化原理圖

插入損耗在分路器的頻率范圍內變化,從 2GHz 時的 0.8dB(典型值)到 26.5GHz 時的 2.4dB。這個插入損耗必須加入到分路器的 3dB 損耗中,以提供在某個頻率下,信號通過分路器遭受的總損耗。在HMC8364 版本電路板更高的工作頻率下,因為ADF41513 的 RF 輸入靈敏度隨著頻率的增加而增加,插入損耗會影響鎖定。詳細說明參見頻率靈敏度部分。

相位再同步

當鎖定到所需頻率時,相位可以建立至相對于基準頻率的任何一個相位偏移。ADF41513 具有相位再同步功能,對于給定的 RFOUT 頻率,從基準電壓源產生一個穩定的相位偏移。在相位關鍵型應用中,例如波束成形,這是一個重要功能。

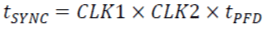

在第一次使能相位再同步后,用戶在操作頻率上選擇相位偏移。如果改變頻率,然后又變回原來的頻率,則保持原來的相位偏移。當相位再同步使能時,內部定時器以下式所給出的間隔 tSYNC產生同步信號:

CLK1 和 CLK2 是 ADF41513 寄存器位域,在應用軟件中編程設置。在編程設置時,必須使 tSYNC大于PLL 最壞情況下的鎖定時間,以確保在 PLL 建立瞬態的最后一個周跳發生相位再同步。注意,如果使用相位再同步,即使在整數模式下運行,也必須使能Σ-Δ調制器。

相位調整

可以使用相位值位域(在 CN-0568 應用軟件中編程設置),按任何給定頻率手動增加相位。可以使用以下公式生成相位偏移:

然后,相位會在每次向 ADF41513 的寄存器0寫入時,按相位偏移量增加。在相位再同步模式下也是一樣,必須使能∑-?調制器來執行相位調整,即使是在整數模式下運行。

頻率靈敏度

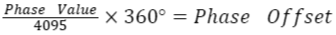

ADF41513 的最大輸入頻率為 26.5 GHz, HMC8364 四頻 VCO 版本稍高一些,為 26.6 GHz。但是,當頻率接近 24GHz 時,有許多因素(如本節所述)會影響性能并導致環路不能鎖定。因此,指定該電路的最大工作頻率為僅 24 GHz。在室溫下使用時,指定工作頻率為 24GHz。但是,如果溫度升高,最大工作頻率可能會降低。

影響鎖定的第一個因素是,HMC8364 VCO 輸出功率會在頻段 4 的頻率增加時降低。具體參見圖6 所示。

圖 6. HMC8364 輸出功率與頻段 4 中整個溫度范圍下的調諧電壓的關系

這種輸出功率降低對電路的整體功率損耗有很大影響。在 23.9 GHz 到 26.6 GHz 范圍內,輸出功率下降了 6 dB。

RF功率分路器插入損耗也隨著頻率的增加而增加。在更高的工作頻率下,這可以產生高達 1dB 的額外損耗,導致反饋環路的總損耗增加。

此外,ADF41513 的 RFIN 頻率靈敏度隨著工作頻率的增加而增加。工作頻率高于 24 GHz 時,這種靈敏度變得更加重要,因為受之前提到的會導致損耗的其他因素影響,會更難以達到所需的輸出功率。RF 反饋路線可以重新設計,以便在較窄的頻率范圍內,在較高的頻率下實現更低的插入損耗。但是,該電路的目標之一是演示所有三種四頻 VCO 在最寬頻率范圍內的性能。另一種增加反饋信號功率的技術是:在反饋環路中添加一個放大器。請參見常見變化章節了解詳細信息。

使用控制電路,根據應用軟件中所選的頻率來選擇不同的 VCO 頻段。GPIO 信號從 SDP-K1 Arduino連接器路由,以根據所需頻率選擇頻段。對自定義固件執行寫入,以傳輸這些 GPIO 控制邏輯信號,具體參見 CN0568 產品頁面。參見 Circuit 電路評估和測試章節,了解有關加載自定義固件的詳細信息。

壓控振蕩器頻段選擇電路的主要組件之一是 ADG1604 4:1 多路復用器。這將來自 LT3045 穩壓器的+5v 電源電壓通過多路復用器的 4 個開關中的一個饋送至對應的 VCO 頻段電源。在控制電路中使用多路復用器可以確保一次只啟用一個 VCO 內核,避免對 VCO 器件造成損壞。所有控制信號都包括濾波電感和電容,以衰減可能發生的噪聲和干擾。圖 7 所示為控制電路的簡化框圖,用于進行說明。(包含控制電路的電路板完整原理圖在 CN0568 設計支持包中。)

圖 7. VCO 頻段選擇,包含多路復用器

VCO 集成式輸出緩沖器通過單刀雙擲(SPDT)開關進行開關,該開關通過另一個 SDP-K1 GPIO 信號進行管控。默認情況下,該信號在應用軟件建立連接后保持高電平。

頻率更新序列

ADF41513 上的頻率控制寄存器受到雙重緩沖。這意味著,要改變 RF 輸出頻率,必須執行兩個事件。首先,必須根據所需的新頻率更新頻率控制字寄存器。然后,對寄存器 0 執行寫操作,以開始頻率變化。每次在應用軟件前面板上更新頻率,會對總共4 個寄存器進行寫入,包括寄存器 0 寫入。這些寄存器必須按以下順序寫入:寄存器 6,寄存器 3,寄存器 1,然后是寄存器 0。

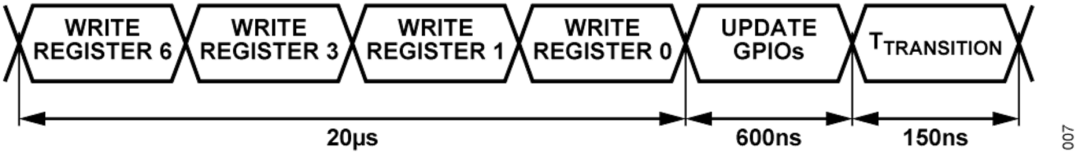

當使用不同 VCO 頻段的頻率更新到當前頻率時,GPIO控制信號在寄存器寫入后更新,如圖8所示。

圖 8. 頻率更新序列

在寄存器 0 更新約 600ns 后,GPIO 更新。轉換時間是變化的 GPIO 地址位和進行多路復用的對應輸出開關之間的延遲時間。ADG1604 4:1 多路復用器的典型轉換時間為 150ns。

電源調節

EVAL-CN0568-ARDxZ 由兩個外部電源供電,它們連接至板載 SMA 連接器。+25v 提供給 V+SMA,6v 提供給 J1。ADF41513 電源根據 EV-ADF41513SDxZ 評估板上的默認電源分組進行分組。通過組合更多電源引腳來減少穩壓器的數量,可能會在輸出頻譜中產生不必要的雜散。

提供給 J1 的+6v 電源為四個板載 LT3045 LDO 穩壓器提供輸入電壓。選擇 LT3045 穩壓器的原因在于它具有出色的低噪聲性能和 500mA 輸出電流能力。這些穩壓器為所有的+3.3V ADF41513 電源,以及四頻 VCO 和晶體振蕩器基準電壓源的+5v 電源供電。通過在 SET 引腳上相應設置 RSET電阻,以配置每個穩壓器的輸出電壓。參見 LT3045 數據手冊獲取更多詳細信息。

通過 V+SMA,從外部電源將+25v 電源直接提供給有源環路濾波器電源。在供電路徑中包括解耦電容,以減少干擾供電的外部噪聲。

常見變化

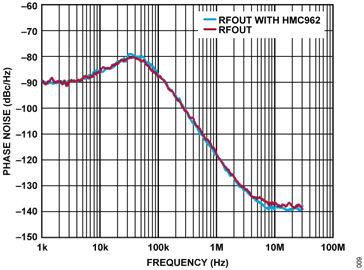

為了補償 HMC8364 四頻 VCO 版本在高于 24GHz時的輸出功率降低,可以在 RFOUT 信號之后增加一個放大器。放大后的信號可以作為 ADF41513 RFIN 端口的反饋信號,以增大工作頻率范圍,最大頻率為 26.5GHz。在圖 9 中,相位噪聲結果匯聚起來,將 HMC962 LNA 連接至 RFOUT 端口。為了比較,然后將其與不帶LNA 的默認配置進行重疊。

圖 9. RFOUT 上連接和不連接 HMC962 時的相位噪聲比較

如圖 9 所示,輸出中包含 HMC962 時,相位噪聲不會降低。在 24 GHz 時,放大器的增益約為 12.5 dB。在這種情況下,放大器的輸入功率電平為-7.4 dBm。在輸出端,測量到的功率電平為 5.23 dBm。這是一個非常合適的功率電平,因為它在 ADF41513 的24GHz 頻率下的最大和最小靈敏度范圍內。有關ADF41513靈敏度水平的更多信息,請參見數據手冊。

電路評估與測試

EVAL-CN0568-ARDxZ 板通過運行 CN0568 特定固件的 SDP-K1 控制板連接至主機。也可使用其他兼容 Arduino 的 3.3v 邏輯接口板,但需要進行固件開發。在首次連接時,演示軟件裝置中的自定義固件文件會加載到 SDP-K1 控制器板中。這通過將軟件包中包含的十六進制文件復制到 SDP-K1 驅動器位置來實現。

設備要求

EVAL-CN0568-ARDxZ 評估板

EVAL-SDP-CK1Z 控制器板

運行 windows 7 或更高版本的 PC/筆記本電腦

頻譜分析儀或相位噪聲分析儀,具有合適的測量頻率范圍

2 × 香蕉插頭,連接至 SMA 電源線

1 × 50 ? RF/微波電纜,帶 2.92mm 連接器

雙電源,提供+25v 和+6v 輸出電壓

步驟

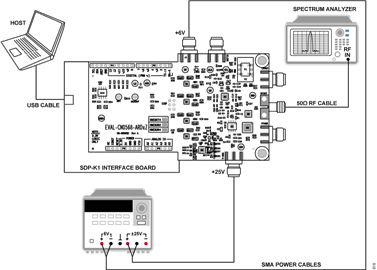

本節介紹設置 EVAL-CN0568-ARDxZ 任意版本,以在 RFOUT 端口上輸出頻率的一般步驟。關于詳細說明,請參見 EVAL-CN0568-ARDxZ 用戶指南。

將 EVAL-CN0568-ARDxZ 安裝到 SDP-K1控制器板上。

通過 USB 電纜,將主機 PC/筆記本電腦連接至 SDP-K1 接口板。

將+6v(限流值 = 200mA)連接至 J1,+25v(限流值= 20mA)連接至 V+SMA。

將 50 ? RF 電纜連接至頻譜/相位噪聲分析儀。

確保電源已關閉。如圖 10 所示設置評估板。

接通兩個電源

打開 CN0568 軟件,選擇正確的版本。然后按“連接”按鈕,啟動該器件。

選擇工作頻率范圍內的頻率,然后選擇“更新頻率”。

所選的頻率將在頻譜分析儀上顯示。

圖 10. 測試設置

結果

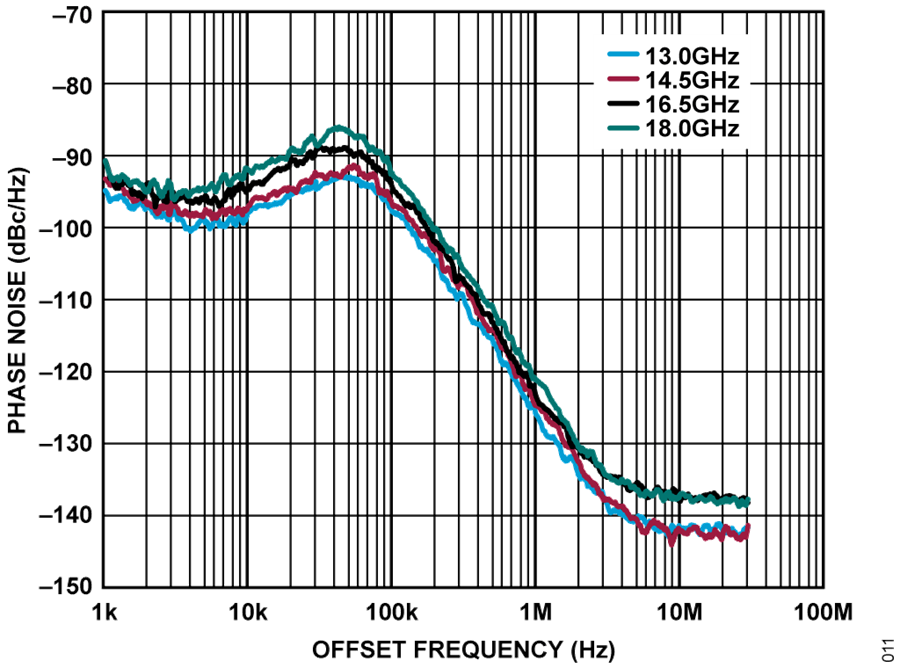

使用 HMC8362 四個頻段的中心頻率獲取相位噪聲結果圖。圖 11 顯示重疊后的相位噪聲圖。

圖 11. EVAL-CN0568-ARD2Z 相位噪聲

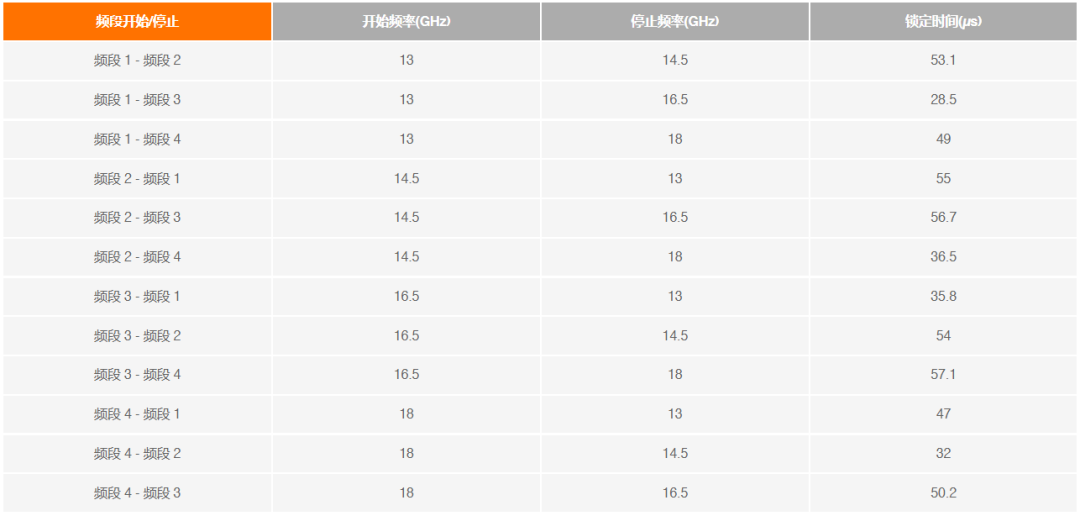

測試結果是使用默認的板載環路濾波器配置(100kHz 環路帶寬)在室溫下獲得的。表 1 中還顯示 EVAL-CN0568-ARD2Z 的電路的測量鎖定時間。

表 1. EVAL-CN0568-ARD2Z 測量鎖定時間

對于這些測量的鎖定時間,鎖定標準是頻率已達到+/- 10kHz 停止頻率,且隨后沒有偏離該閾值。ADISimPLL 用于驗證預期得到的模擬鎖定時間,該時間與這些測量值非常接近。

審核編輯:劉清

-

鎖相環

+關注

關注

35文章

584瀏覽量

87743 -

振蕩器

+關注

關注

28文章

3832瀏覽量

139044 -

接收器

+關注

關注

14文章

2468瀏覽量

71878 -

pll

+關注

關注

6文章

776瀏覽量

135136 -

VCO

+關注

關注

12文章

190瀏覽量

69184

原文標題:集快速開關、高性能PLL和四頻VCO于一體的鎖相環頻率生成電路

文章出處:【微信號:ADI智庫,微信公眾號:ADI智庫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

鎖相環常見問題解答

一文讀懂鎖相環(PLL)那些事

基于高壓VCO的高性能PLL設計

【模擬對話】鎖相環(PLL)基本原理

驅動高壓鎖相環頻率合成器電路中的VCO詳細分析

集快速開關高性能PLL和四頻VCO于一體的鎖相環頻率生成電路介紹

集快速開關高性能PLL和四頻VCO于一體的鎖相環頻率生成電路介紹

評論