1 運行平臺

硬件:CRD500數字信號處理板

系統:win7/64;win7/32;win10/64

軟件:Quartus/ModelSimSE/Verilog/Matlab

2 主要功能及性能指標

3.2.1主要功能

1)產生基帶原始數據

2)位同步信號提取

3.2.2主要性能指標

1) 發送端

系統時鐘:50MHz

基帶數據碼率:1.5625Mbps

數據內容:“11111010”循環碼

2) 接收端

系統時鐘:50MHz

同步方式:超前-滯后型鎖相環位同步

同步精度:1/8 碼元寬度

3 程序結構框圖說明

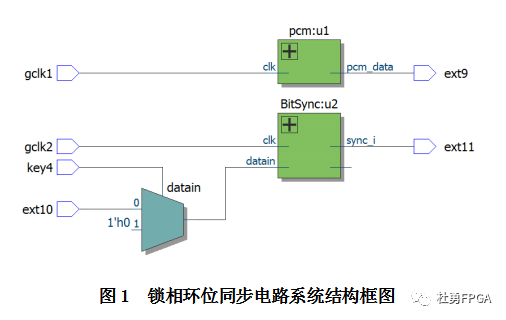

鎖相環位同步電路系統主要由基帶數據生成模塊(pcm.v)、位同步模塊(BitSync.v)組成。

基帶數據生成模塊生成的原始數據(1.5625Mbps)送至開發板上擴展口的第9腳,經短接線由第10腳送回FPGA芯片;位同步模塊從接收到的原始數據中采用鎖相環法提取位同步信號,提取出的位同步信號由擴展口的第11腳輸出。為真實的驗證位同步通信功能,發送端(pcm.v)的時鐘由CRD500開發板上的X1晶振驅動,接收端(BitSync.v)的時鐘由X2晶振驅動。

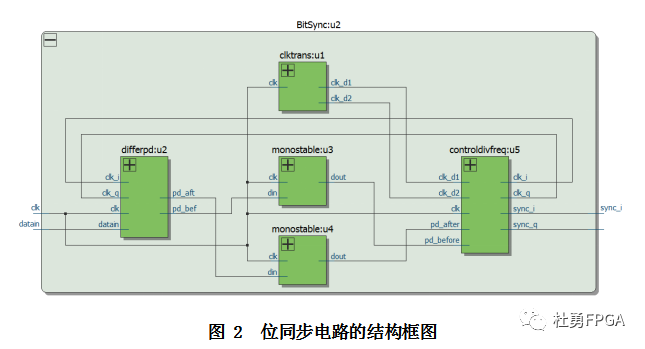

位同步電路的結構框圖如圖2所示。

實例采用超前-滯后型鎖相環位同步電路實現位同步的提取功能,電路主要由鑒相模塊(differpd.v)、雙相時鐘模塊(clktrans.v)、單穩觸發器模塊(monostable.v)和控制分頻模塊(controldivfreq.v)組成。

審核編輯:劉清

-

鎖相環

+關注

關注

35文章

584瀏覽量

87739 -

數字信號處理

+關注

關注

15文章

560瀏覽量

45844 -

同步電路

+關注

關注

1文章

60瀏覽量

13310 -

FPGA芯片

+關注

關注

3文章

246瀏覽量

39795

原文標題:鎖相環位同步(Quartus/Verilog/CRD500)

文章出處:【微信號:杜勇FPGA,微信公眾號:杜勇FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一文詳解鎖相環位同步

一文詳解鎖相環位同步

評論