LTC1709-7 利用了多相的優勢?開關技術可減少輸入電容器的數量和電感器尺寸,并延長電池壽命。隨著 CPU 時鐘頻率的增加,對內核電源電流的需求也隨之增加。當今的 22A CPU 內核電流要求將單級開關穩壓器推向了極致。LTC1709-7 中設計的多相開關允許使用成本更低、外形更緊湊的部件,并且還改善了瞬態響應。

LTC?1709-7 是一款雙通道、電流模式、多相控制器,其驅動兩個同步降壓級 180° 異相。這款小型 SSOP-36 封裝控制器集成了四個高電流 MOSFET 驅動器、一個用于真正輸出遠程檢測的差分放大器、自動均流電路、一個電源良好指示器和 5 位移動 VID 控制。LTC1709-7 還具有在輕負載條件下的突發模式操作和不連續導通模式操作。由此產生的電源解決方案在任何負載條件下都非常高效,并且占用最小的電路板空間。

1 步、2 相 CPU 內核電源

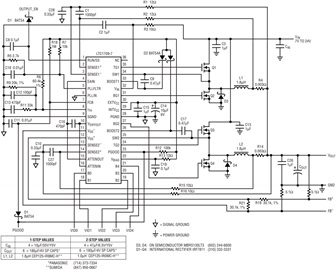

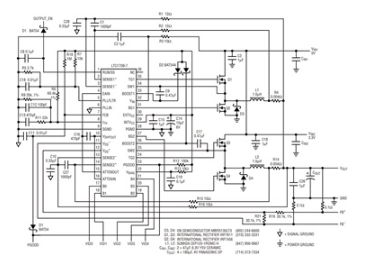

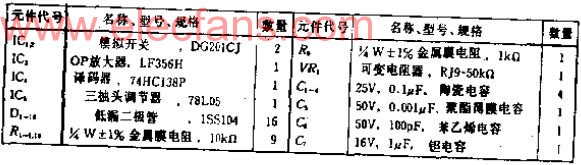

圖 1 示出了將 LTC1709-7 用于 CPU 內核電源的典型應用電路。在 1 步配置中,CPU 內核電壓直接從墻上適配器或電池降壓。輸入電壓可在 7V 至 24V 之間。輸出電壓介于 0.925V 和 2V 之間,由 5 位 VID 輸入設置。該電源將為 CPU 內核提供 22A 的最大電流。僅采用 8 個 IC、1 個 SO-8 MOSFET 和 83 個 20.1μH 扁平表面貼裝電感器,8V 輸入和 22.80V/4A 輸出的效率高達 22%。在 200A 至 <>A 的負載范圍內可保持超過 <>% 的效率。由于輸入電壓較高,底部MOSFET的體二極管中的反向恢復損耗可能很大。肖特基二極管需要與底部MOSFET并聯,以緩解反向恢復問題。由于最大輸入電壓下的開關損耗相對較高,因此選擇了<>kHz的開關頻率。

圖1.單輸入、1 步或 2 步 LTC1709-7 CPU 內核電源。

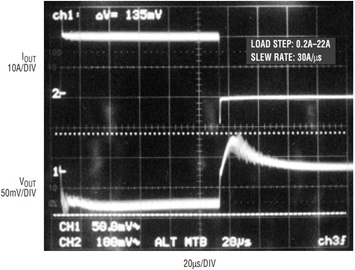

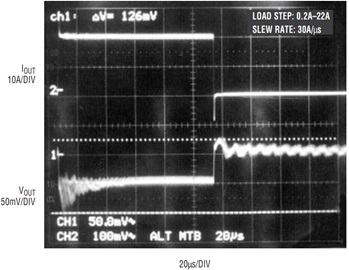

圖2顯示了在20V輸入和1.6V輸出下測得的負載瞬態波形。負載電流在0.2A至22A之間變化,壓擺率約為30A/μs。由于輸出上只有六個低 ESR SP 電容 (180μF/4V),負載瞬變期間的最大輸出電壓變化小于 140mVP-P.請注意,由于穩態占空比較小,高到低負載階躍響應比低到高負載階躍響應慢。本設計采用有源電壓定位以減少輸出電容器的數量(有關有源電壓定位的更多詳細信息,請參閱凌力爾特設計解決方案 10)。R9和R6提供輸出電壓定位,不會降低效率。

圖2.圖1電路的瞬態響應(1步版本);V在= 20V, C外= 六個 SP 帽。

2 步、2 相 CPU 內核電源

在前面描述的1步解決方案中,CPU內核電源的輸入電壓可高達24V。由此產生的低占空比會減慢高到低負載瞬態響應(如圖2所示),并增加同步FET中的電流應力。這增加了輸出電容和MOSFET的尺寸和成本。高輸入電壓還會增加頂部 MOSFET 中的開關損耗和功耗。為了盡量減少內核電源中產生的熱量,CPU內核電源最好從低輸入電壓源(如5V系統電源)獲取電源。由于5V電源通常由電池或墻上適配器產生,因此這種方法總共需要兩步電源轉換。

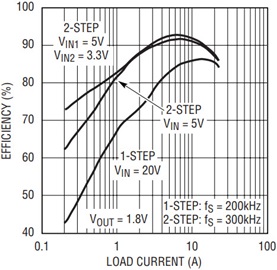

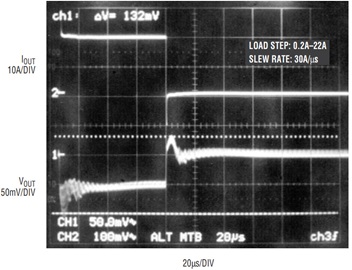

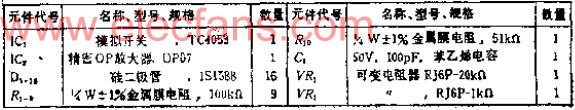

5V輸入、兩步CPU內核電源設計與圖2所示幾乎相同。唯一的區別是圖 1 表中所示的組件更改。如圖1所示,與3步解決方案相比,2步設計將輕負載效率提高了20%,滿載效率提高了2%。如圖1所示,負載瞬態響應也得到了改善。由于輸出端的SP電容少了兩個,兩步電路實現了與4步相似的性能。

圖3.1 步和 2 步設計的效率與負載電流的關系。

圖4.圖1電路的瞬態響應(2步版本);V在= 5V, C外= 四個 SP 上限。

因為 CPU 功率可以大于 40W,所以為 LT5-1709 供電的 7V 電源的輸出電流額定值可能超過 15A。這將顯著增加5V系統電源電路的功率損耗、成本和尺寸。如果 3.3V 和 5V 系統電源由兩相 LTC2 電路產生,則 LTC1876 電路中兩個降壓通道的功率不平衡會降低輸入紋波電流消除的有效性。LTC1876 電路的輸入側必須使用更多的高電壓電容器 (>25V)。有關更多信息,請參見 LTC1876 的產品手冊。

為了提高為 LT1876-1709 供電的 LTC7 電路的效率并降低總體成本,可能需要從兩個不同的電源 3.3V 和 5V 獲取 CPU 內核電源,如圖 5 所示。這樣,就可以優化 3.3V 和 5V 電源的設計,以最大限度地減小 LTC1876 電路的功率損耗。此外,由于2.3V輸入通道上的開關損耗更低,3輸入設計進一步提高了輕負載效率。然而,由于沒有輸入紋波電流消除,因此2輸入設計需要在3.3V和5V電源軌上使用更大的濾波電容;如圖5所示,從低到高的負載階躍響應將比單6V輸入設計慢,因為3.3V輸入通道具有較少的電壓來增加電感電流。有關 2 輸入、2 相設計的更多信息,請參見凌力爾特設計說明 222。

圖5.2 輸入、2 步 LTC1709-7 CPU 內核電源。

圖6.圖5電路的瞬態響應(1步版本);V合1= 5V, V合2= 3.3V, C外= 四個 SP 上限。

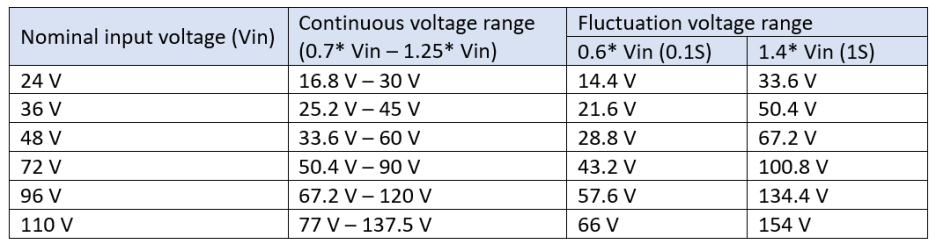

表 1 比較了不同設計方法的性能。顯然,在CPU電源的性能和尺寸方面,2步設計比1步設計更具優勢。5V 輸入、2 步設計在內核電源中具有最佳性能。

|

1-Step VIN = 20V |

2-Step |

|

| VIN = 5V |

VIN1 = 5V VIN2 = 3.3V |

|

|

Efficiency at VOUT = 1.8V |

IOUT = 0.2A | 43% |

| IOUT = 22A | 83% | |

|

CIN |

4 × 10μF/35V/Y5V ceramic caps | |

|

COUT |

6 × SP caps | |

|

Inductors |

2 × 1.8μH | |

|

Load transient response: 0.2A–22A |

< 140mVP-P | |

|

Switching frequency |

200kHz | |

結論

基于 LTC1709-7 的低電壓、高電流移動 CPU 電源同時實現了高效率和小尺寸。電容器、電感器和散熱器的節省有助于最大限度地降低整體電源的成本。本文介紹的 LTC1709-7 電路適合為需要大內核電源電流的高速移動 CPU 供電。與 1 步解決方案相比,2 步設計提供了更好的內核電源效率,并且需要更小的輸出電感器和電容器。

審核編輯:郭婷

-

電感器

+關注

關注

20文章

2329瀏覽量

70509 -

cpu

+關注

關注

68文章

10855瀏覽量

211594 -

開關穩壓器

+關注

關注

4文章

793瀏覽量

73450

發布評論請先 登錄

相關推薦

矩陣切換器怎么分類?

什么是矩陣切換器

多相切換器減少了元件數量,實現了更小、更便宜的移動CPU電源

多相切換器減少了元件數量,實現了更小、更便宜的移動CPU電源

評論