xilinx和altera都有通過IO驅動HDMI的方案,支持的分辨率各有不同,這跟不同系列的FPGA性能是相關的。

易靈思的鈦金系列FPGA是采用16nm工藝的,屬于高性能FPGA,它支持1.5G LVDS及高速的IO,這成為了實現HDMI自環的基礎。并通過本實驗驗驗證了Ti60F100來實現了1080p60的接收與發送的可行性。

我們先來了解下TMDS的電氣特性。

TMDS電氣特性

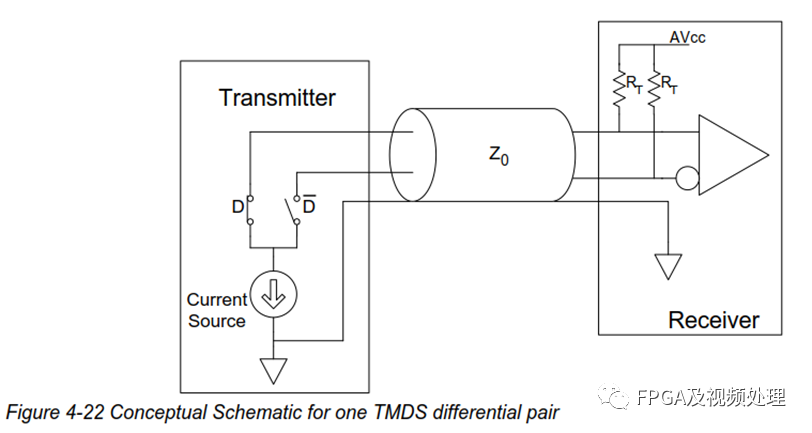

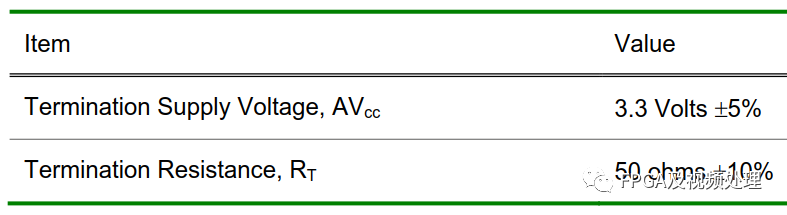

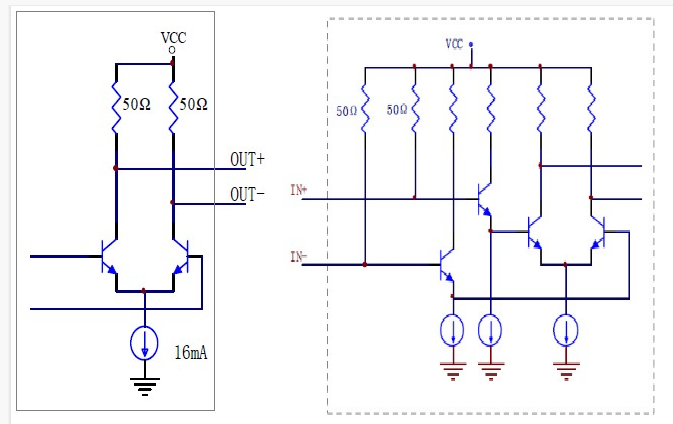

TMDS利用電流驅動技術在直流耦合傳輸線接收端產生低壓差分信號。鏈路參考電壓AVcc設置差分信號的高電壓電平,而低電壓電平由HDMI源端的電流源和接收終端電阻(RT)決定。終端電阻(RT)和電纜的特性阻抗(Z0)必須匹配。

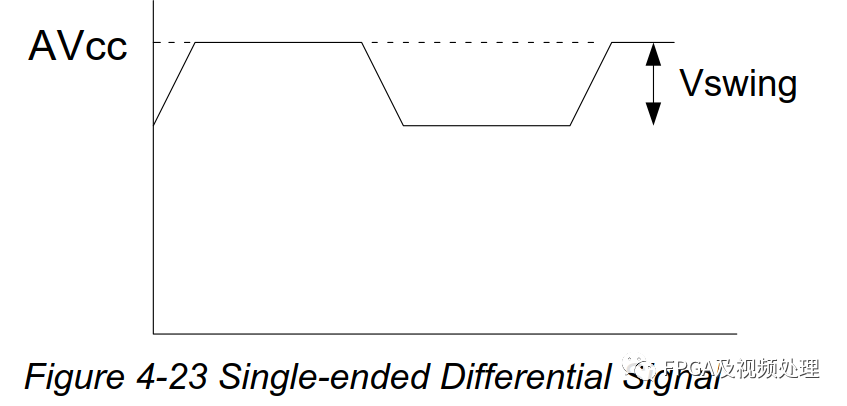

對于差分信號的一端,標稱高電平電壓為AVcc,標稱低電平電壓為(AVcc - Vswing)。

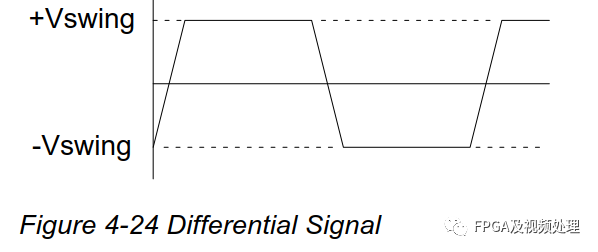

差分對上的擺幅是一端擺幅的兩倍,2*Vswing ,約為1000mV(VP-VN,分別指TMDS差分對的P端或者N端)。

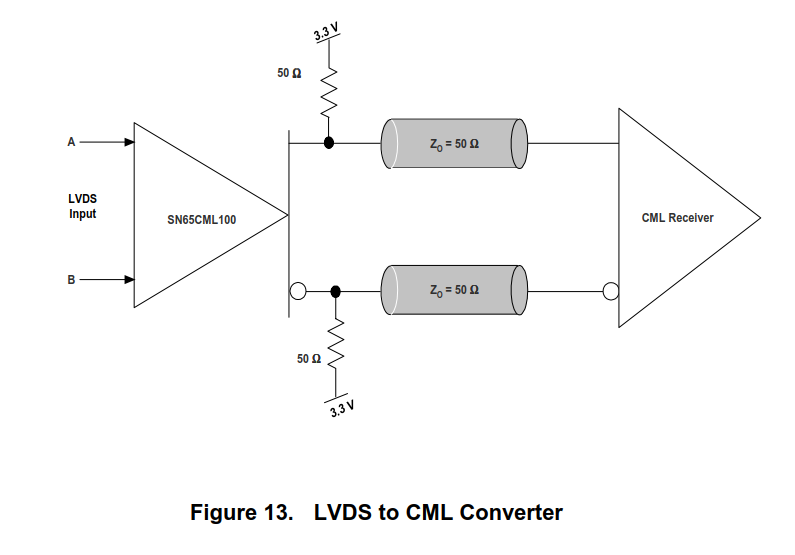

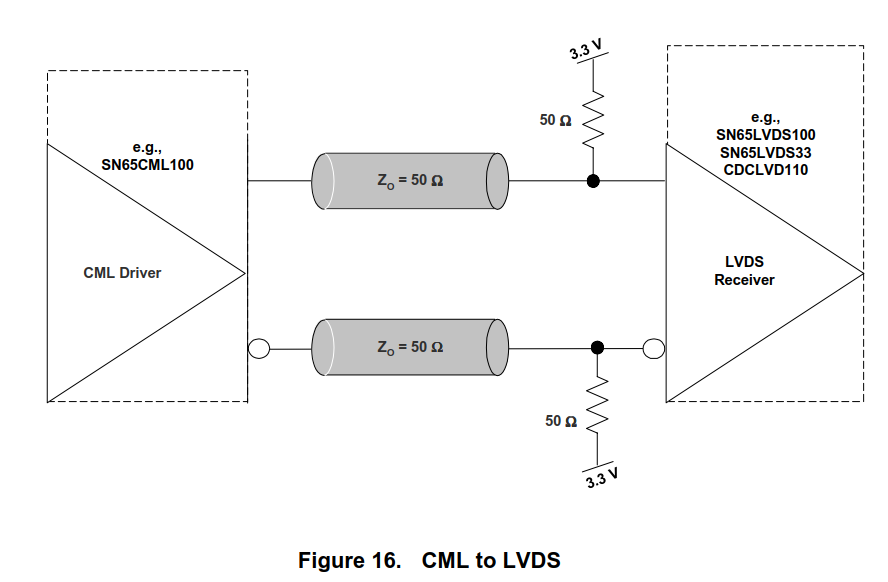

從框圖上看TMDS電平更符合或者說接近CML的電平標準。在源端都有一個恒流源。而且差分對高電低電平的實現也都是通過源端一端導通一端截止來實現,只是HDMI的上拉通過接收端來實現。在接收端都對輸入信號上拉到了50歐,其余部分也可以認為相同。

所以LVDS與CML的電平轉換成為了硬件設計的理論基礎。

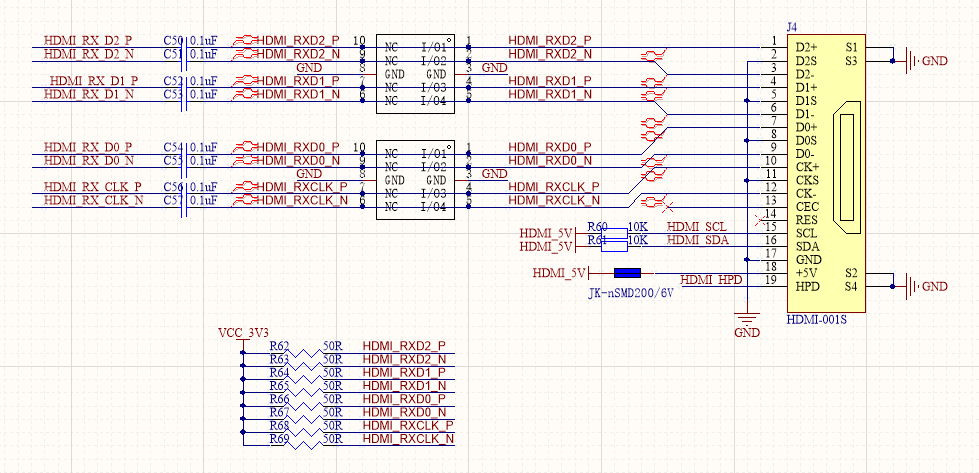

本次驗證通過Ti60F100來實現。硬件采用炫覽科技開發的demo板。

測試環境為輸入采用1.5M HDMI線,輸出采用3M HMDI。測試分辨為1080p60fps和720p60fps.

HDMI接收過程

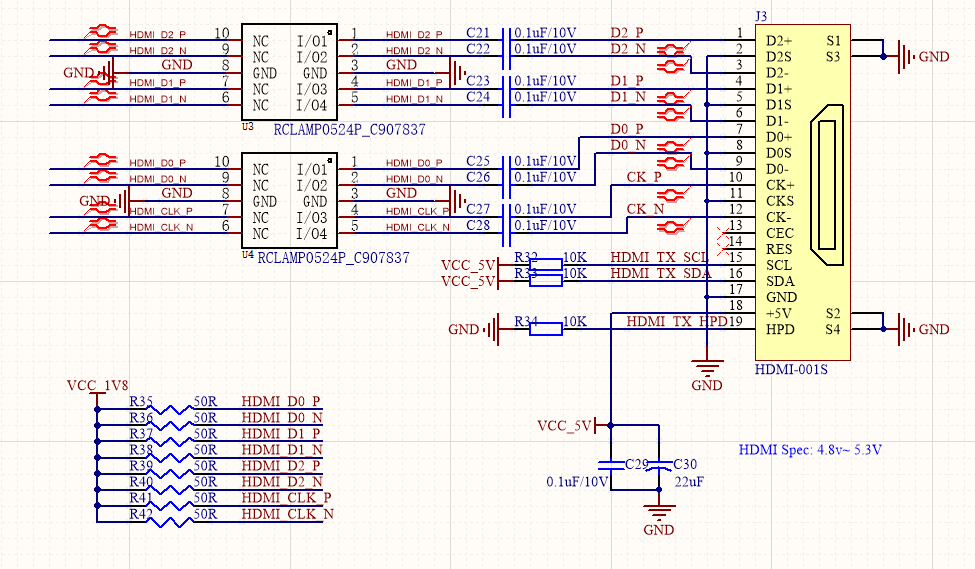

HDMI接收端通過50R電阻上拉,再通過電容耦合連接到FPGA。

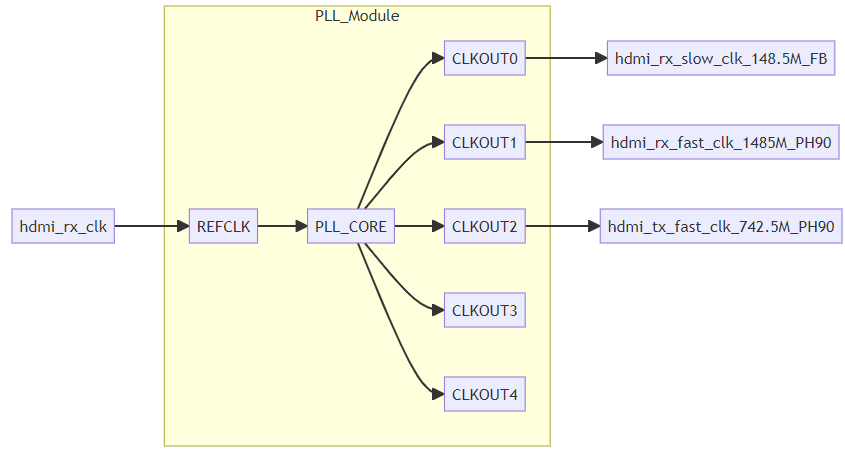

時鐘方案如下:

HDMI接收時鐘經過PLL產生串行時鐘742.5M用于1080p串行數據采集。通過LVDS實現串并換轉換成10位并行數據同步到148.5M的時鐘上。

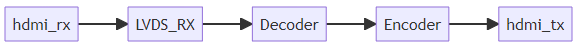

實現過程如下:

HDMI發送處理

與LVDS轉CML的電平轉換相似,只不過這里都使用了交流耦合。有時間再嘗試DC耦合方式。

另外從IO的和鎖相環性能的角度出發,我們試驗了以下兩種方案:

方案一 :通過單端實現偽TMDS差分

理論基礎是:

TMDS差分傳動技術是一種利用2個引腳間電壓差來傳送信號的技術。傳輸數據的數值("0"或者"1")由兩腳間電壓正負極性和大小決定。即,采用2根線來傳輸信號,一根線上傳輸原來的信號,另一根線上傳輸與原來信號相反的信號。這樣接收端就可以通過讓一根線上的信號減去另一根線上的信號的方式來屏蔽電磁干擾,從而得到正確的信號。

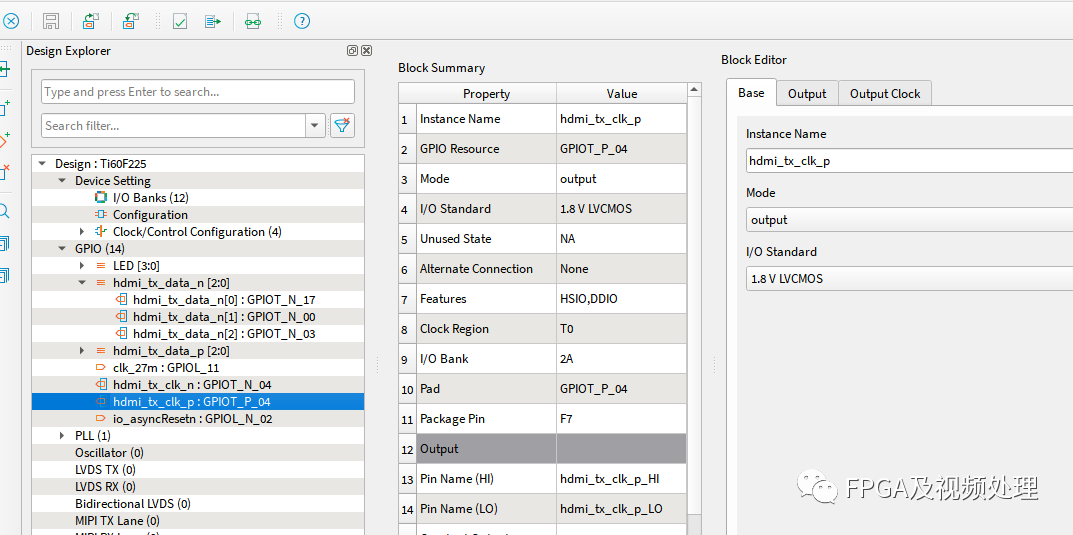

按照上面的原理我們把HDMI的4對差分對通過單端來實現。我們分別對HDMI的三對數據和一對時鐘用LVCMOS 1.8V電平實現。并勾選DDIO選項。

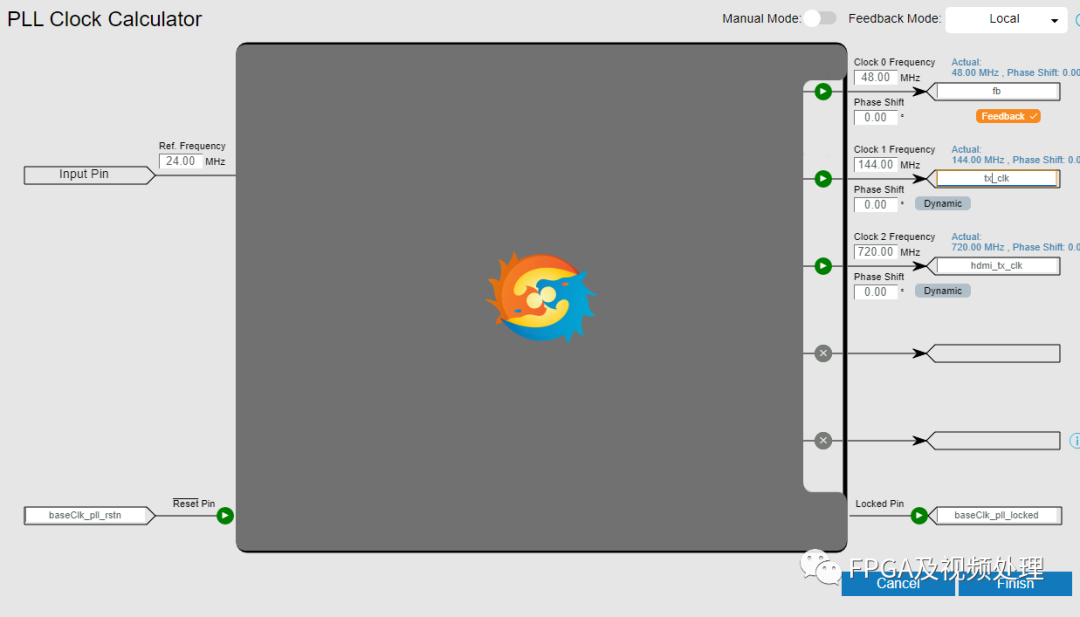

時鐘的設置如下。由于鎖相環的限制,內部處理時鐘為144,數據位寬為10位,接口上通過時鐘雙沿采樣,時鐘為720。測試分辨率為1080p@58Hz,畫面輸出正常。如果通過時鐘用25M的話,快速時鐘為750M應該也是可以的。

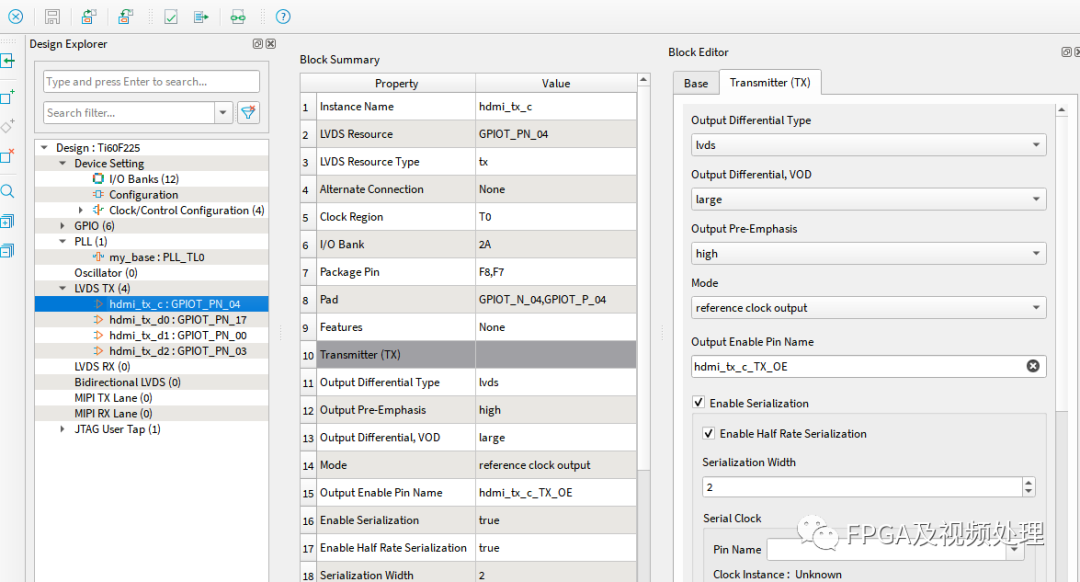

方案二:通過LVDS實現替代TMDS差分對

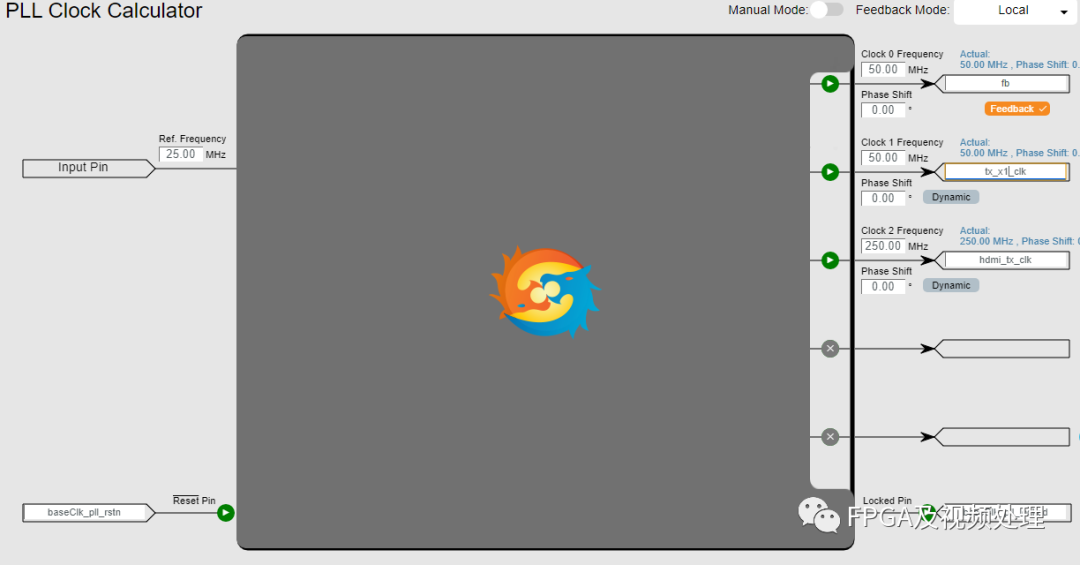

在interface中例化4對LVDS輸出。并通過PLL產生對應的并行與串行時鐘。

另外關于5V接收與發送,HPD和DDC的處理都相對比較簡單,在這里就不詳細展開了。

審核編輯:劉清

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603009 -

HDMI

+關注

關注

32文章

1694瀏覽量

151864 -

TMDS

+關注

關注

1文章

22瀏覽量

15507 -

LVDS屏

+關注

關注

0文章

9瀏覽量

1387

原文標題:Ti60F100高速IO實現HDMI環出方案

文章出處:【微信號:gh_ea2445df5d2a,微信公眾號:FPGA及視頻處理】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Ti60F100 內外flash操作方案

求一種DisplayPort到DVI / HDMI信號轉換適配器方案

一種高速串行視頻接口TIDA-00137參考設計

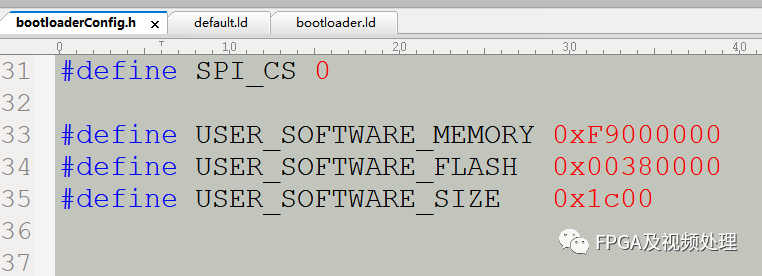

Ti60F100用片內flash啟動RISCV程序不能成功的解決辦法

易靈思Ti60F100驅動LCD屏案例

求一種Ti60F100高速IO實現HDMI環出方案

求一種Ti60F100高速IO實現HDMI環出方案

評論